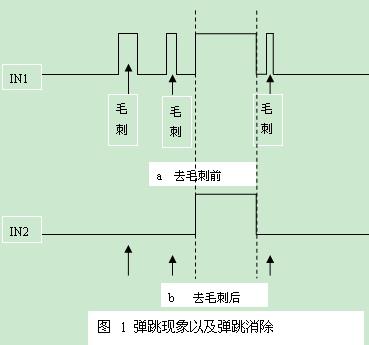

按鍵作為一種機械開關,在進行按鍵操作時,機械接觸點的彈性及電壓突變等原因,在機械開關合閉的時候會出現電壓抖動,因此在實際的應用當中需要做一定的處理。

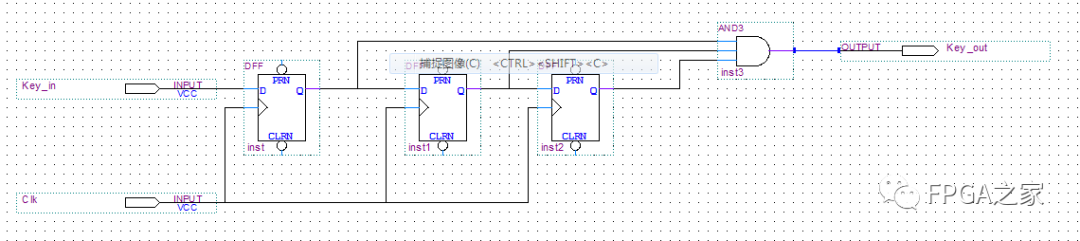

一般按鍵按下就是低電壓,這種按鍵去抖動的關鍵就是獲取穩定的低電壓電平狀態,因此,對于對于一個按鍵信號,可以用一個脈沖信號對其進行采樣,如果連續三次采樣都為低電平的話,就認為是按鍵被按下。其數字電路原型為下圖

其實,我們在做FPGA設計之前,就應該大概知道自己的coding 在FPGA芯片上面會映射成什么電路,這樣寫的代碼才是可靠的,有了上面的原理圖,那么Verilog代碼就很容易了,如下

input wire Clk ;

input wire key_in ;

output wire key_out ;

reg key_dly1;

reg key_dly2;

reg key_dly3;

always @(posedge Clk)

begin

if(Rst_n == 1'b0) begin

key_dly1 <= 1'b0; key_dly2 <= 1'b0; key_dly3 <= 1'b0; end

else

begin

key_dly1 <= key_in ;

key_dly2 <= key_dly1;

key_dly3 <= key_dly2;

end

end

assign key_out = key_dly1 | key_dly2 | key_dly3;

對于復雜的電路我們也可以把他分解為每一個觸發器,然后心里有個大概的硬件原理圖,這樣寫代碼才胸有成竹。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

27259 -

觸發器

+關注

關注

14文章

2034瀏覽量

62009 -

FPGA芯片

+關注

關注

3文章

248瀏覽量

40289

原文標題:按鍵抖動消除 verilog

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于按鍵抖動問題的解決

消除按鍵抖動的兩種方法分享

如何通過軟件編程實現消除鍵盤的抖動

運用外部中斷函數消除按鍵抖動

按鍵彈跳消除模塊的程序設計與應用

外部中斷的按鍵抖動(按鍵消抖)

單片機按鍵去抖動的方法

按鍵抖動消除verilog設計

按鍵抖動消除verilog設計

評論