ASIC的架構是復雜的,它需要大量的經(jīng)驗來完成和描述架構和微架構。本文討論了架構和微架構設計,在ASIC設計階段非常有用。

在芯片設計和開發(fā)過程中,芯片架構設計的重要策略如下:

理解功能和模塊級表示

單時鐘或多時鐘

功率要求

面積和速度要求

并行性

流水線

外部接口

技術節(jié)點

下面將從芯片的架構設計、微架構設計、使用設計文檔、設計分區(qū)、時鐘域和時鐘組、架構調整與性能改進、處理器微架構設計策略等角度進行說明,并以視頻H.264編碼器設計為例。

01

架構設計

對于任何基于ASIC的產(chǎn)品開發(fā),我們首先需要了解的是功能規(guī)范,然后我們需要落實:

外部接口

電氣特性

速度,功率和面積要求

機械裝配或封裝

設計和驗證策略

測試策略

在此基礎上,根據(jù)設計的功能以及對面積、速度和功率的要求,討論對復雜設計有用的架構和微架構設計概念。

假如我們設計一款用于視頻編碼的H.264編碼器,用于處理1920×1080P的高清圖像。

對于芯片工程師而言,最初我們的任務是設計功能模塊,積累工程經(jīng)驗和方法,然后我們將利用經(jīng)驗來完成架構和微架構的設計。

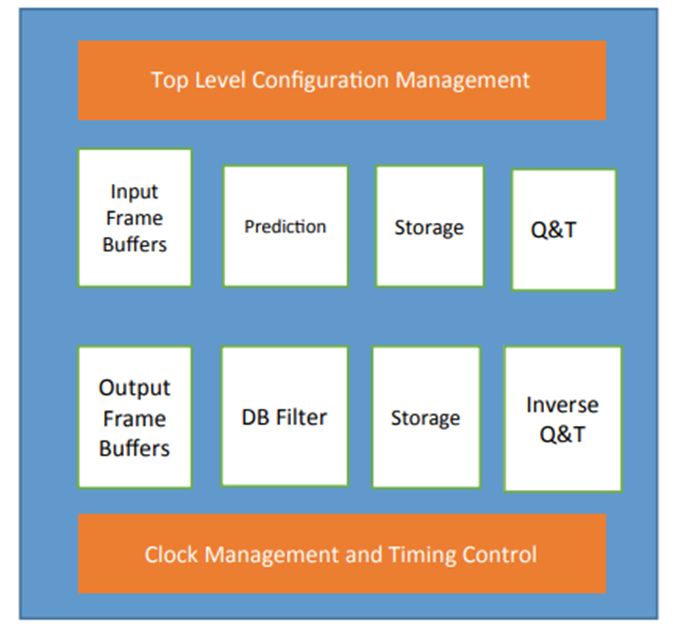

H.264編碼器的重要功能模塊如圖1所示,主要包括:

幀緩沖區(qū)

預測(幀內、幀間)

存儲緩沖區(qū)

量化與變換(Q&T)

逆量化與變換(Q&T)

去塊濾波器(DB濾波器)

圖1 H.264功能塊級表示

架構師團隊使用以下設計要點,完成ASIC架構的設計!

(a)設計功能和對設計應用的理解

(b)將在何處使用該設計,以及與之有關的限制

(c)速度、功率、面積等優(yōu)化約束

(d)晶圓廠制定規(guī)則,即DRC

(e)低功耗架構和低功耗排序要求

(f)具有不同時鐘組的多個時鐘域設計和策略

(g)不同階段的IP要求可能是硬IP或軟IP

(h)內存和宏單元需求

(i)設計的總體數(shù)據(jù)速率、時序和時鐘要求

(j)ASIC設計軟硬件劃分的總體策略

(k)所需的測試設置和EDA工具

(l)電氣特性和接口時序要求

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52291瀏覽量

437635 -

asic

+關注

關注

34文章

1244瀏覽量

122118 -

架構

+關注

關注

1文章

528瀏覽量

25890

原文標題:【芯片設計】架構與微架構設計

文章出處:【微信號:FPGA算法工程師,微信公眾號:FPGA算法工程師】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

汽車電子電氣架構設計及優(yōu)化措施

STM32軟件架構設計的意義

對嵌入式系統(tǒng)中的架構設計的理解

系統(tǒng)架構設計的詳細講解

SWE.2的軟件架構設計

SYS.3的系統(tǒng)架構設計

STM32軟件架構設計

架構與微架構設計

架構與微架構設計

評論