編者注:我在很多場合講過從仿真到測量這個話題,最近我也看到了一些調(diào)研數(shù)據(jù)。這個問題現(xiàn)在在國內(nèi)來講應該算是處于起步階段,但是我相信未來會越來越好。

數(shù)據(jù)中心利用發(fā)射系統(tǒng)和接收系統(tǒng)之間的通道,可以準確有效地傳遞有價值的信息。如果通道性能不佳,就可能會導致信號完整性問題,并且影響所傳數(shù)據(jù)的正確解讀。因此,在開發(fā)通道設備和互連產(chǎn)品時,確保高度的信號完整性非常關(guān)鍵。測試、識別和解決導致設備信號完整性問題的根源,就成了工程師面臨的巨大挑戰(zhàn)。本文介紹了一些仿真和測量建議,旨在幫助您設計出具有優(yōu)異信號完整性的設備。

中央處理器(CPU)可將信息發(fā)送到發(fā)光二極管顯示器,它是一個典型的數(shù)字通信通道示例。該通道 — CPU 與顯示器之間的所有介質(zhì) — 包括互連設備,例如顯卡、線纜和板載視頻處理器。每臺設備以及它們在通道中的 連接都會干擾 CPU 的數(shù)據(jù)傳輸。

信號完整性問題可能包括串擾、時延、振鈴和電磁干擾。盡早解決信號完整性問題,可以讓工程師開發(fā)出可靠性更高的高性能的產(chǎn)品,也有助于降低成本。

通道仿真

工程師通常會用電子設計自動化軟件來創(chuàng)建電路仿真。設計自動化軟件則是采用逐位和統(tǒng)計仿真技術(shù),用以提供快速而準確的通道仿真。算法建模接口是設計軟件所使用的一種標準, 它可以輕松仿真從發(fā)射到接收的多千兆位串行鏈路。

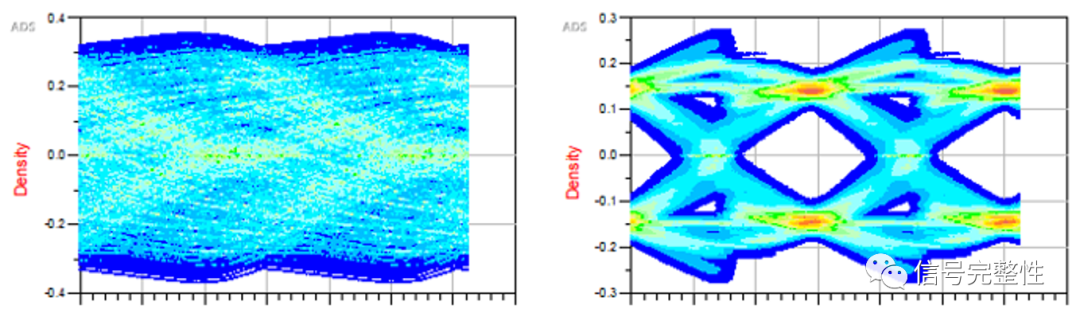

除了仿真軟件以外,工程師還使用眼圖、混合模式 S 參數(shù)、時域反射測量之類的信號分析工具。在仿真從發(fā)射機到接收機的數(shù)據(jù)傳輸時,示波器上顯示的眼圖可以作為分析參數(shù),幫助評估通道性能。

眼圖的寬度和高度是信號失真的關(guān)鍵指標。寬大的眼圖意味著數(shù)據(jù)傳輸良好。閉合的眼圖表示信號完整性大幅降低。如果發(fā)射機處的眼圖是開眼,接收機處是閉眼,下一步就需要確定通道中的哪些設備或互連導致了信號衰減。工程師可以直接查看發(fā)射機輸出端的眼圖,通過每個互連追溯到接收機,從中確定導致信號衰減的組件。

圖 1:閉合的眼圖和正常的眼圖的示例

確定信號衰減的根本原因

描述給定設備的頻率特性時,工程師可以使用 S 參數(shù)作為標準。互連的 S 參數(shù)(無論是在時域還是在頻域中進行測量)代表了互連的特征模型。該參數(shù)涵蓋了信號從進入一個端口到離開另一個端口時的所有特性信息。

為了確定信號衰減的根本原因,重要的是先要確定您對 S 參數(shù)的期望值。將期望值與測量值進行比較,有助于識別導致信號完整性衰減的通道區(qū)域。

接下來,您需要更深入地研究被測設備和設備之間的連接,以便確定根本原因。對于差分通道,可以使用混合模式 S 參數(shù)進行分析。最常見的 S 參數(shù)是與電磁干擾有關(guān)的差分回波損耗(SDD11)、差分插入損耗(SDD21)和差分至共模轉(zhuǎn)換(SCD21)。

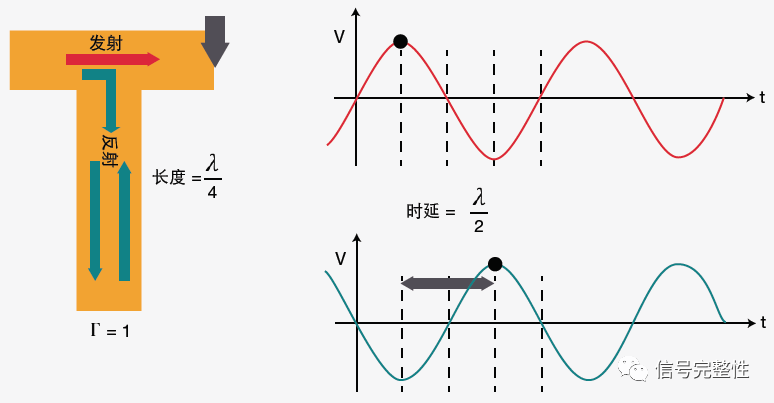

在分析傳輸質(zhì)量時,還需要重點考慮反射因素。每當出現(xiàn)瞬時阻抗變化時,信號就會被反射。反射會使返回的原始信號出現(xiàn)延遲(如下圖 2 所示),并與原始信號結(jié)合而產(chǎn)生干擾。

圖 2:反射對信號質(zhì)量的影響

探索和設計信號完整性解決方案

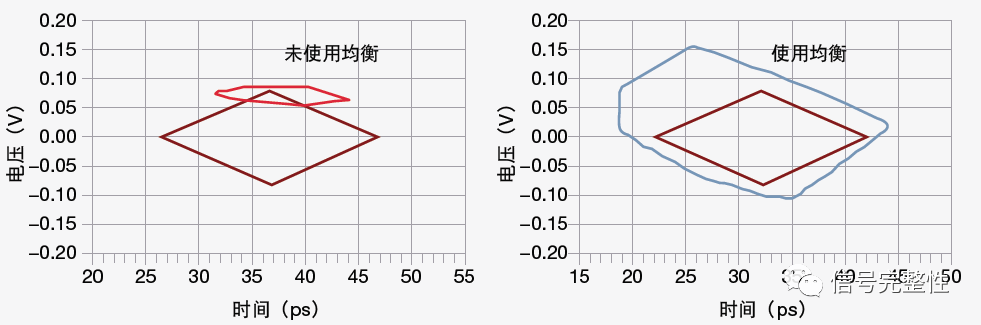

初步找到信號衰減的根本原因之后,您就需要研究并確定最佳的解決方案。首先,要執(zhí)行去除設計缺陷后的仿真測試,以驗證您確實找到了信號完整性衰減的根本原因。我們的建議是,與其將刪除有問題的區(qū)域作為解決方案,不如試著在接收機上添加均衡,例如添加決策反饋均衡

(DFE)、頻域中的連續(xù)時間線性均衡或時域中的發(fā)射機前饋均衡。同樣,您也可以通過仿真來 添加均衡,通過在示波器上實時觀察眼圖的變化,即可測試該均衡是否已經(jīng)解決了信號完整性衰減的問題。

如圖 3 所示,另一個測試選項就是將眼圖模板應用于添加均衡之前和之后。在添加均衡之前,圖像相交,表示眼圖閉合。在添加均衡之后,圖像不再相交,表示眼圖打開。

圖 3:使用 DFE 前后的眼圖模板比較

信號完整性分析

當產(chǎn)品設計從仿真階段進展到硬件環(huán)節(jié)時,您需要使用矢量網(wǎng)絡分析儀(VNA)來測試高速數(shù)字 互連。首先,您需要對通道、物理層設備、連接器、電纜、背板或印刷電路板的預期測量結(jié)果有所了解。在獲得實際測量結(jié)果之后,再將實際結(jié)果與這個預期結(jié)果進行比較。我們的目標是,通過軟件和硬件來建立可靠的信號完整性工作流程。硬件測量步驟包括儀器測量設置,獲取通道數(shù)據(jù),以及分析通道性能。

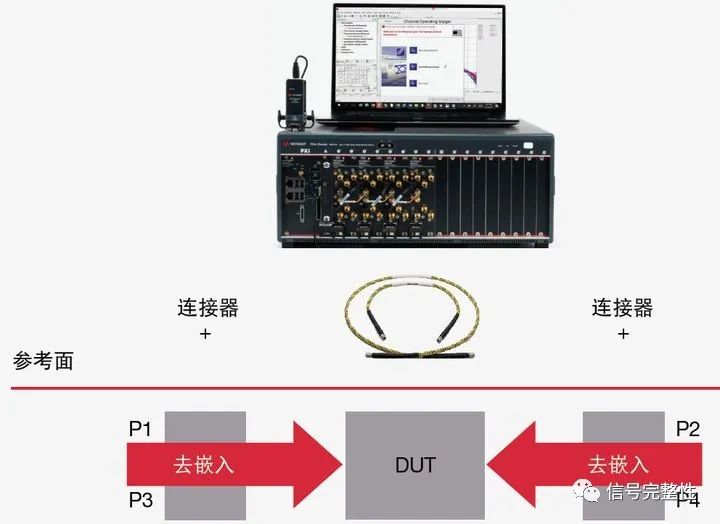

對于矢量網(wǎng)絡分析儀(VNA)等高動態(tài)范圍的儀器,您需要全面了解誤差校正,才能確保最準確的 S 參數(shù)測量。誤差校正包括校準(測量前誤差校正)和去嵌入(測量后誤差校正)。通過調(diào)整校準和去嵌入的參考點檢查通道中除了 DUT 之外的所有節(jié)點項目。以下內(nèi)容介紹了校準和去嵌入誤差校正之間的差異以及二者的使用方法。

信號校準

默認情況下,當矢量網(wǎng)絡分析儀(VNA)開啟時,其參考平面位于前面板。將電纜連接到被測設備時,校準參考必須使用短路-開路-負載-直通法(SOLT)、直通反射線或直通反射匹配參考結(jié)構(gòu)。SOLT 是最常見的方法。

電纜可以直接連接到 DUT 或夾具。夾具安裝在電纜和 DUT 之間,有助于兼容不同類型的連接器,例如 HDMI、顯示端口、串行 ATA 和 PCI Express。在本示例中,校準參考面包括電纜,而去嵌入?yún)⒖济姘▕A具。將校準誤差校正和去嵌入相結(jié)合時,必須包括通道中與 DUT 的所有互連。連接 DUT 后,您就可以進行測量,并執(zhí)行測量后(去嵌入)誤差校正。

圖 4:使用參考面進行校準的測試設置

去嵌入

完成測量,在 DUT 的輸入和輸出端設置去嵌入?yún)⒖键c,以便移除測試夾具。移除測試夾具之后,也就去除了引入到系統(tǒng)中的損耗和反射,最終得到 DUT 的準確 S 參數(shù)測量和表征結(jié)果。

通過將兩層校正(校準和去嵌入)的 S 參數(shù)結(jié)果與預期結(jié)果進行比較,您可以進行模型調(diào)整以便匹配實際測量值,然后繼續(xù)進行設備開發(fā)。

圖 5:使用參考面進行去嵌入的測試設置

克服信號完整性問題

隨著數(shù)據(jù)傳輸速度的提高,信號完整性對于通道設備和互連產(chǎn)品越來越重要。為了確保您的設備具有出色的信號完整性,首先您要確定好希望獲得的仿真結(jié)果,然后再將其與實際測量結(jié)果進行比較。

接下來,結(jié)合信號分析技術(shù)(例如在示波器上顯示的眼圖)和仿真軟件,即可找到導致信號衰減的根本原因。下一步就是確定合適的解決方案,使用軟件和硬件來建立可靠的信號完整性工作流程。

必須使用高質(zhì)量的矢量網(wǎng)絡分析儀(VNA),設置校準參考面以執(zhí)行 S 參數(shù)測量,設置去嵌入?yún)⒖济嬉哉_移除夾具。測量結(jié)果將會包括準確的 S 參數(shù)和可靠的 DUT 特性。盡早解決信號完整性問題,您就可以優(yōu)化電路設計,保證優(yōu)異的設備性能和出色的價格優(yōu)勢。

審核編輯:劉清

-

示波器

+關(guān)注

關(guān)注

113文章

6709瀏覽量

189364 -

接收機

+關(guān)注

關(guān)注

9文章

1224瀏覽量

54605 -

信號完整性

+關(guān)注

關(guān)注

68文章

1445瀏覽量

96782 -

中央處理器

+關(guān)注

關(guān)注

1文章

126瀏覽量

16866

原文標題:從仿真到測量的信號完整性

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

信號完整性基礎(chǔ)指南

信號完整性與電源完整性的仿真

什么是信號完整性?

如何設計出具有優(yōu)異信號完整性的設備?

如何設計出具有優(yōu)異信號完整性的設備?

評論