前言:從今天開始,我們會定期整理FPGA交流群(包括其他FPGA博主的群)里面有價值的問題,并匯總成文章,如果問題多的話就每周整理一期,如果問題少就每兩周整理一期,一方面是希望能幫到不經常看群消息的小伙伴,另一方面也算是我們的技術積累。

Q:FPGA中的Bank和Clock Region有什么關系?

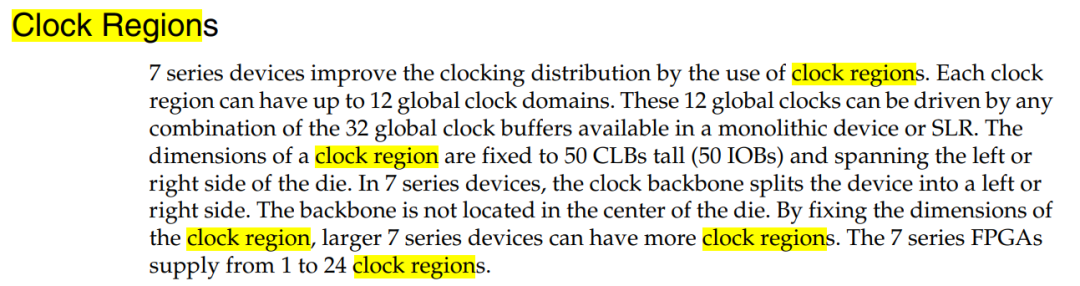

A:這應該是很多FPGA工程師都很困惑或者沒有認真相關的一個問題,首先來看Clock Region的定義,我們以7系列為例:

image-20230513230025082

image-20230513230025082

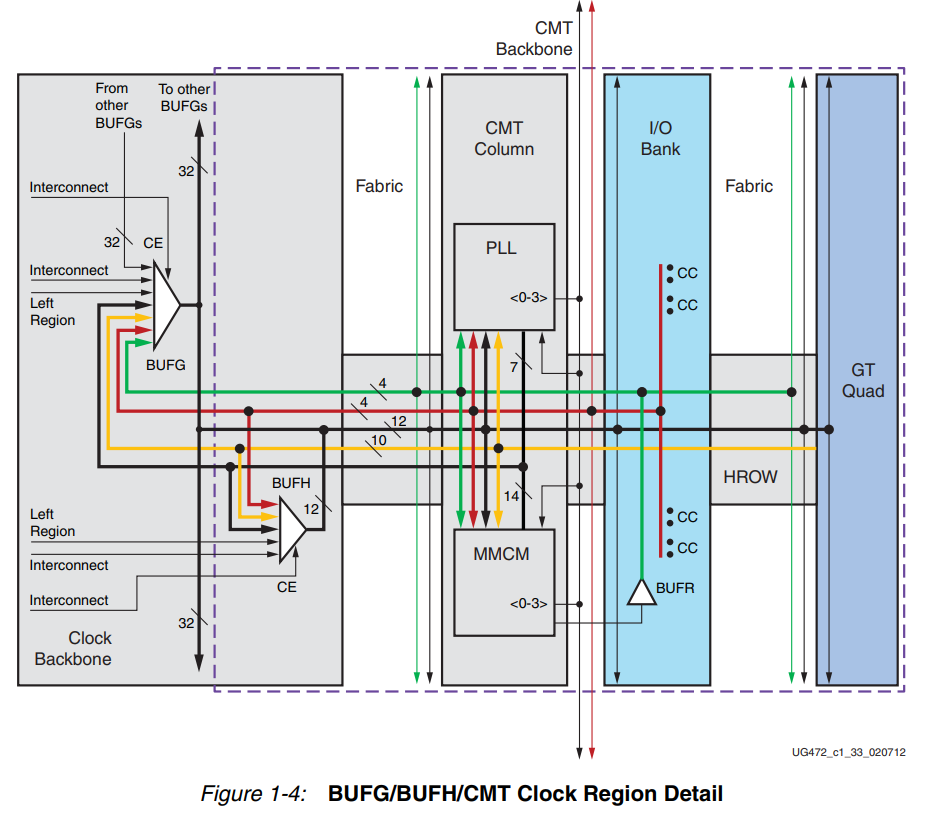

可以看出,Clock Region是包含很多東西的:CLB、CMT、BUFG、BUFH等,當然也包括IO Bank,CLB中又包含了FF、LUT、DSP等資源。

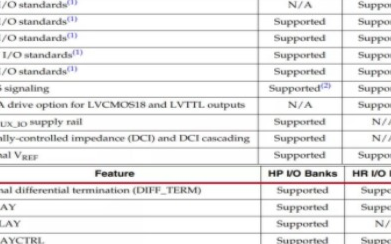

而IO Bank的定義如下:

I/ObanksarecollectionsofI/Oblocks(IOBs),withconfigurableSelectIOdriversandreceivers,supportingawidevarietyofstandardinterfaces,bothsingle-endedanddifferential.

可以看出,IO Bank一般就是指一堆有相同特性的 IO的合集,所以我們一般不會說一個bank里面包含FF/DSP這些資源。

Q:FPGA中如何對寄存器類型做初始化?

A:FPGA的初始化其實比ASIC更靈活一些,initial語句原本是用于仿真時的初始化,但在FPGA中,initial是可以被綜合的,這是因為FPGA是基于SRAM查找表結構實現的,上電后需要從外部加載配置信息,這個時候initial可以讓存儲器載入一個初始化文件,實現初始化的操作。

但對于ASIC的話,initial只能用于仿真,無法綜合。

我們甚至還可以采用如下的方式進行初始化:

initialbegin:INIT $readmemh(pMemInit,mem_bk); end

審核編輯:湯梓紅

-

dsp

+關注

關注

556文章

8151瀏覽量

355860 -

FPGA

+關注

關注

1644文章

21993瀏覽量

615407 -

寄存器

+關注

關注

31文章

5427瀏覽量

123718 -

工程師

+關注

關注

59文章

1589瀏覽量

69290 -

仿真

+關注

關注

51文章

4250瀏覽量

135450

原文標題:FPGA問答系列--FPGA中Bank和Clock Region之前有什么關系?

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA中Bank和Clock Region之前有什么關系?

FPGA中Bank和Clock Region之前有什么關系?

評論