從5G到工業應用,隨著收集、傳送和存儲的數據越來越多,也在不斷擴大模擬信號處理器件的性能極限,有些甚至達到每秒千兆采樣。由于創新的步伐從未放緩,下一代電子解決方案將使解決方案體積進一步縮少,電源效率持續提高,并對噪聲性能提出更高的要求。

人們可能認為應當最大限度地減少或隔離各電源域(模擬、數字、串行數字和數字輸入輸出(I/O))中產生的噪聲,以實現出色的動態性能,但追求絕對最小噪聲可能會使收益遞減。設計人員如何知道電源的噪聲性能是否足夠?首先要量化器件的靈敏度,使電源頻譜輸出與該電源域要求匹配。知識就是力量:通過避免過度設計來節約設計時間,對設計會有很大的幫助。

本文概述如何量化信號處理鏈中負載的電源噪聲靈敏度以及如何計算最大可接受電源噪聲。還會討論測量設置。最后,我們將討論一些滿足電源域靈敏度和現實電源噪聲需求的策略。

了解并量化信號處理負載對電源噪聲的靈敏度電源優化的第一步是研究分析模擬信號處理器件對電源噪聲的真正靈敏度。其中包括了解電源噪聲對關鍵動態性能規格的影響,以及電源噪聲靈敏度的表征 — 即,電源調制比(PSMR)和電源電壓抑制比(PSRR)。

PSMR和PSRR表明是否具有良好的電源抑制特性,但僅憑它們并不足以確定紋波應有多低。本文介紹如何利用PSMR和PSRR確定紋波容限閾值或最大允許電源噪聲。只有確定與電源頻譜輸出相匹配的閾值才可能實現優化電源系統設計。如果確保電源噪聲低于其最大規格值,則優化電源不會降低每個模擬信號處理器件的動態性能。

電源噪聲對模擬信號處理器件的影響應了解電源噪聲對模擬信號處理器件的影響。這些影響可通過三個測量參數進行量化:

-

無雜散動態范圍(SFDR)

-

信噪比(SNR)

-

相位噪聲(PN)

了解電源噪聲對這些參數的影響是優化電源噪聲規格的第一步。

無雜散動態范圍(SFDR)

電源噪聲可耦合到任何模擬信號處理系統的載波信號中。電源噪聲的影響取決于其相對于頻域中載波信號的強度。一種測量方法是SFDR,它代表能與大干擾信號區分開來的最小信號 — 具體來講,就是載波信號的幅度與最高雜散信號幅度的比值,不管它在頻譜的哪個位置,都得出下式:

SFDR = 無雜散動態范圍(dB)

載波信號 = 載波信號幅度的均方根值(峰值或滿量程)

雜散信號 = 頻譜中最高雜散幅度的均方根值

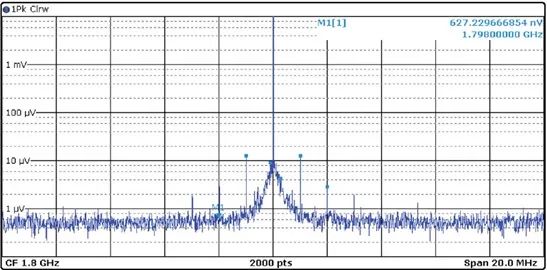

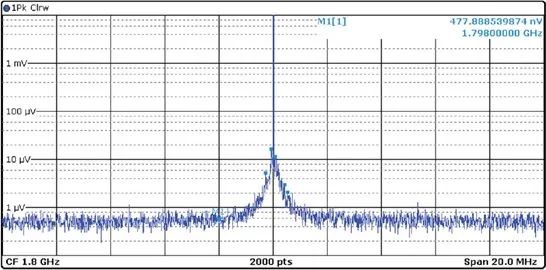

圖1.使用(a)干凈電源和(b)噪聲電源兩種情況下,AD9208高速ADC的SFDR。

SFDR可以相對于滿量程(dBFS)或載波信號(dBc)來指定。電源紋波耦合到載波信號可產生干擾雜散信號,這會降低SFDR。圖1比較了采用干凈電源和噪聲電源供電兩種情況下,AD9208高速ADC的SFDR性能。在這種情況下,當1 MHz電源紋波作為調制雜散出現在ADC的快速傅立葉變換(FFT)頻譜輸出的載波頻率附近時,電源噪聲會使SFDR降低約10 dB。

信噪比(SNR)

SFDR取決于頻譜中的最高雜散,而SNR則取決于頻譜內的總噪聲。SNR限制模擬信號處理系統識別低振幅信號的能力,并且理論上受系統中轉換器分辨率的限制。SNR在數學上定義為載波信號電平與所有噪聲頻譜分量(前五次諧波和直流除外)之和的比值,其中:

SNR = 信噪比(dB)

載波信號 = 載波信號的均方根值(峰值或滿量程)

頻譜噪聲 = 除前五次諧波之外的所有噪聲頻譜分量的均方根和

噪聲電源通過在載波信號中耦合并在輸出頻譜中添加噪聲頻譜分量,可降低SNR。如圖2所示,當1 MHz電源紋波在FFT輸出頻譜中產生頻譜噪聲分量時,AD9208高速ADC的SNR從56.8 dBFS降低到51.7 dBFS。

相位噪聲(PN)

相位噪聲是衡量信號頻率穩定性的參數。理想情況下,振蕩器應能夠在一定時間段內產生一組特定的穩定頻率。但是在現實世界中,信號中總是存在一些小的干擾幅度和相位波動。這些相位波動或抖動分布在頻譜中的信號兩側。

相位噪聲可采用多種方式定義。在本文中,相位噪聲定義為單邊帶(SSB)相位噪聲,這是一種常用定義,其使用載波信號偏移頻率的功率密度與載波信號總功率的比值,其中:

SSB PN = 單邊帶相位噪聲(dBc/Hz)

邊帶功率密度 = 載波信號偏移頻率下每1 Hz帶寬的噪聲功率(W/Hz)

載波功率 = 總載波功率(W)

圖2.使用(a)干凈電源和(b)噪聲電源兩種情況下,AD9208高速ADC的SNR。

圖3.(a) 輸出噪聲量有顯著差異的兩個不同電源。(b) 分別由這兩個電源供電時,ADRV9009產生的相位噪聲性能。

對于模擬信號處理器件,通過時鐘電源電壓耦合到器件時鐘中的電壓噪聲會產生相位噪聲,進而影響內部本振(LO)的頻率穩定性。這擴大了頻譜中LO頻率的范圍,增加了與載波相對應的偏移頻率下的功率密度,從而增加了相位噪聲。

圖3比較了由兩個不同電源供電時ADRV9009 收發器的相位噪聲性能。圖3a顯示兩個電源的噪聲頻譜,圖3b顯示產生的相位噪聲。兩個電源都基于采用展頻(SSFM)的 LTM8063 μModule 穩壓器。SSFM的優勢在于,通過將基頻分布在一定范圍內,可改善轉換器的基波開關頻率及其諧波的噪聲性能。從圖3a中可以看出這一點 — 注意在1 MHz及其諧波處具有相對較寬的噪聲峰值。需要權衡考量的一點是,SSFM的三角波調制頻率會產生低于100 kHz的噪聲 — 注意峰值從2 kHz左右開始。

備用電源添加一個低通濾波器以抑制高于1 MHz的噪聲,添加一個 ADP1764 低壓差(LDO)后置穩壓器以減少整體本底噪聲,特別是低于10 kHz的噪聲(主要是SSFM產生的噪聲)。由于額外濾波,整體電源噪聲獲得改善,從而增強了10 kHz偏移頻率以下的相位噪聲性能,如圖3b所示。

模擬信號處理器件的電源噪聲靈敏度負載對電源紋波的靈敏度可以通過兩個參數來量化:

-

電源電壓抑制比(PSRR)

-

電源調制比(PSMR)

電源電壓抑制比(PSRR)

PSRR表示器件在一定頻率范圍內衰減電源引腳噪聲的能力。通常,有兩種類型的PSRR:靜態(直流)PSRR和動態(交流)PSRR。直流PSRR用于衡量直流電源電壓變化引起的輸出失調變化。這一點幾乎無需關注,因為電源系統應該會為負載提供穩定調節的直流電壓。另一方面,交流PSRR表示器件在一定頻率范圍內抑制直流電源中交流信號的能力。

交流PSRR通過在器件的電源引腳注入正弦波信號,并觀察在注入頻率下出現在數據轉換器/收發器輸出頻譜本底噪聲上的誤差雜散來確定(圖4)。交流PSRR定義為測得的注入信號幅度與輸出頻譜上相應的誤差雜散幅度之比,其中:

誤差雜散 = 注入紋波引起的輸出頻譜中的雜散幅度

注入紋波 = 在輸入電源引腳處耦合并測量的正弦波幅度

圖4.電源紋波引起的模擬信號處理器件輸出頻譜中的誤差雜散。

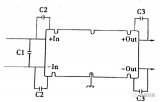

圖5所示為典型PSRR設置的方框圖。以AD9213 10 GSPS高速ADC為例,在1.0 V模擬電源軌上有源耦合1 MHz、13.3 mV峰峰值正弦波。在ADC的–108 dBFS FFT頻譜本底噪聲之上出現相應的1 MHz數字化雜散。1 MHz數字化雜散為–81 dBFS,對應的峰峰值電壓為124.8 μV,參考1.4 V峰峰值的模擬輸入滿量程范圍。使用公式4計算1 MHz的交流PSRR,得到1 MHz的交流PSRR為40.5 dB。圖6顯示了AD9213 1.0 V AVDD軌的交流PSRR。

圖5.PSRR/PSMR測試設置的簡化方框圖。

圖6.1.0 V AVDD軌的AD9213高速ADC交流PSRR。

電源調制比(PSMR)

PSMR對模擬信號處理器件的影響與PSRR不同。PSMR表示使用RF載波信號進行調制時,器件對電源噪聲的靈敏度。這種效應可以看作是施加于器件的載波頻率周圍的調制雜散,表現為載波邊帶。

電源調制通過使用線路注入器/耦合電路將輸入紋波信號與干凈的直流電壓相結合來實現。電源紋波作為正弦波信號從信號發生器注入電源引腳。調制到RF載波的正弦波產生邊帶雜散,其偏移頻率等于正弦波頻率。雜散水平受正弦波幅度和器件靈敏度的影響。簡化的PSMR測試設置與PSRR的相同,如圖5所示,但輸出主要顯示載波頻率及其邊帶雜散,如圖7所示。PSMR定義為電源注入紋波幅度與載波周圍調制邊帶雜散幅度的比值,其中:

調制雜散 = 注入紋波引起的載波頻率邊帶雜散幅度

注入紋波 = 在輸入電源引腳處耦合并測量的正弦波幅度

圖7.電源紋波引起的載波信號中的調制邊帶雜散。

假設AD9175 12.6 GSPS高速DAC在100 MHz載波下工作,在1.0 V AVDD軌上有源耦合約3.05 mV峰峰值的10 MHz電源紋波。載波信號的邊帶中出現相應的24.6 μV峰峰值調制雜散,偏移頻率等于約10 MHz的電源紋波頻率。使用公式5計算10 MHz的PSMR,得到41.9 dB。圖8顯示通道DAC0在各種載波頻率下的AD9175 1.0V AVDD軌PSMR。

圖8.1.0 V AVDD軌(通道DAC0)的AD9175高速DAC PSMR。

確定最大允許電源紋波PSMR可與受電器件的基準閾值相結合,用于確定模擬信號處理器件的每個電源域的最大允許電壓紋波。基準閾值本身可以是幾個值之一,代表器件可容忍而不會顯著影響其動態性能的允許雜散電平(由電源紋波引起)。此雜散電平可以是無雜散動態范圍(SFDR),最低有效位(LSB)的百分比或輸出頻譜本底噪聲。公式6顯示最大允許輸入紋波(VR_MAX)與PSMR和各器件測得的本底噪聲呈函數關系,其中:

VR_MAX = 在輸出頻譜本底噪聲中產生雜散之前各個電源軌上的最大允許電壓紋波

PSMR = 目標電源軌的噪聲靈敏度(dB)

閾值 = 預定義的基準閾值(本文中為輸出頻譜本底噪聲)

例如,AD9175的輸出頻譜本底噪聲約為1 μV峰峰值。1800 MHz載波在10 MHz紋波下的PSMR約為20.9 dB。使用公式6,器件電源引腳中可容忍而不會降低其動態性能的最大允許紋波為11.1 μV峰峰值。

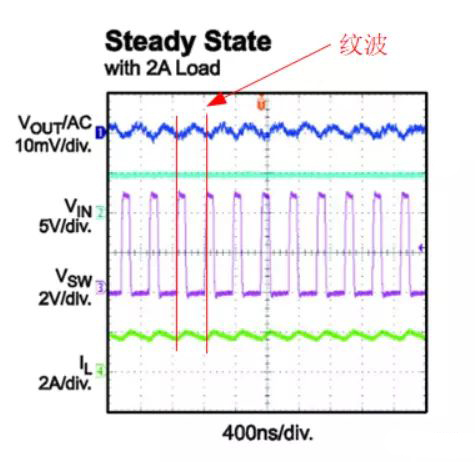

圖9顯示LT8650S 降壓型Silent Switcher 穩壓器(帶和不帶輸出LC濾波器)的頻譜輸出和AD9175 1.0 V AVDD軌的最大允許紋波的組合結果。穩壓器頻譜輸出包含基波開關頻率及其諧波處的雜散。直接為AD9175供電的LT8650S產生超過最大允許閾值的基頻,導致在輸出頻譜中產生調制邊帶雜散,如圖10所示。只需添加一個LC濾波器就可以將開關雜散降至最大允許紋波以下,如圖11所示。

圖9.LT8650S在1.0 V AVDD軌上的電源頻譜輸出和最大允許電壓紋波的關系。

圖10.AD9175 DAC0在1800 MHz載波頻率下的輸出頻譜(使用LT8650S DC-DC Silent Switcher轉換器直接輸出到AVDD軌)。

圖11.AD9175 DAC0在1800 MHz載波頻率下的輸出頻譜(使用帶LC濾波器電源的LT8650S)。

結論高速模擬信號處理器件出色的動態性能很容易被電源噪聲削弱。為了避免系統性能下降,必須充分了解信號鏈對電源噪聲的靈敏度。這可通過設定最大允許紋波來確定,最大允許紋波對于配電網絡(PDN)設計至關重要。知道最大允許紋波閾值后,就可以采用各種方法來設計優化電源。如果最大允許紋波具有良好的裕度,則PDN不會降低高速模擬信號處理器件的動態性能。

-

亞德諾

+關注

關注

6文章

4680瀏覽量

16279

原文標題:對你來說,多少電源噪聲是可以接受的?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

普源MSO8000示波器電源噪聲測試設置方法詳解

頻域示波器在電源噪聲分析中的應用

EMC測試中的環境噪聲控制:為什么6dB是關鍵?

通過AD芯片的哪些參數可以推算出對AD芯片供電的電源的紋波和噪聲的要求啊?

GND與電源噪聲隔離技術 如何監測GND電壓變化

干貨分享!電源紋波、噪聲及測試

DCDC電源輸出噪聲大的原因

電源濾波器是如何降低電源噪聲的

對你來說,多少電源噪聲是可以接受的?

對你來說,多少電源噪聲是可以接受的?

評論