目前市面上能支持HDL語言聯(lián)合仿真的電源仿真軟件并不多,能支持VHDL聯(lián)合仿真的就更少了,PSIM軟件支持VHDL及verilogHDL聯(lián)合仿真,這樣對于快速驗(yàn)證HDL實(shí)現(xiàn)的新想法是十分便捷的。

PSIM中VHDL代碼仿真,是通過調(diào)用QuestaSim/ModelSim,兩款軟件協(xié)同完成的,本質(zhì)屬于不同軟件的聯(lián)合仿真。

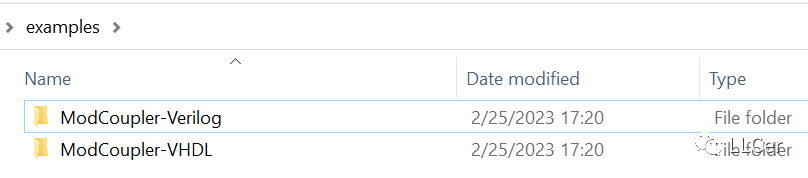

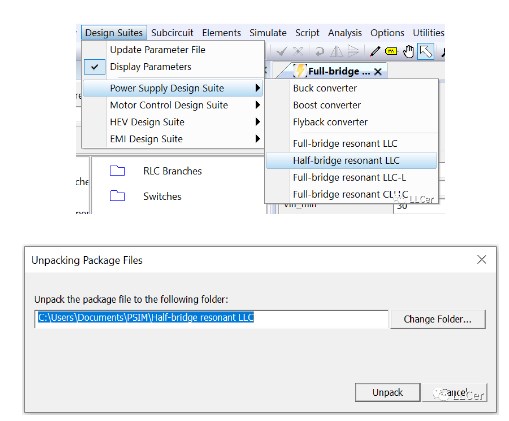

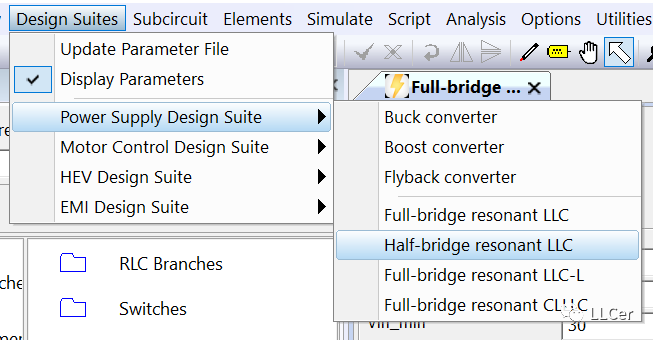

下圖是PSIM軟件自帶的例子,運(yùn)行此例子需要安裝QuestaSim/ModelSim軟件。

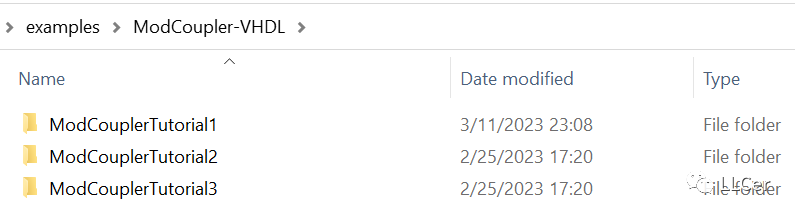

VHDL例子有3個(gè),Tutorial1是3相兩電平逆變器,Tutorial2是同步buck,Tutorial3是單相全橋逆變器。

一,

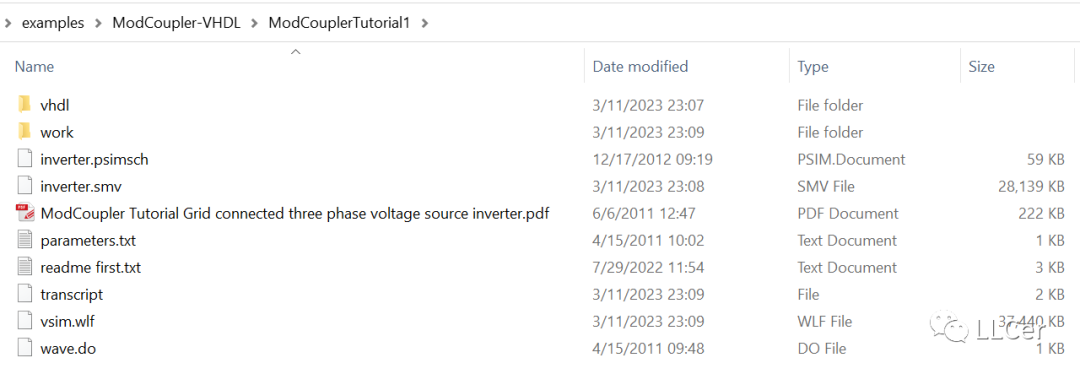

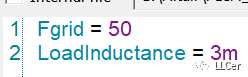

打開Tutorial1文件夾,內(nèi)容如下,下級vhdl文件夾中是8個(gè).vhd源文件和1個(gè)compile.bat(調(diào)用VHDL編譯及仿真),下級work文件夾就是vhdl的工作文件夾(work庫)。

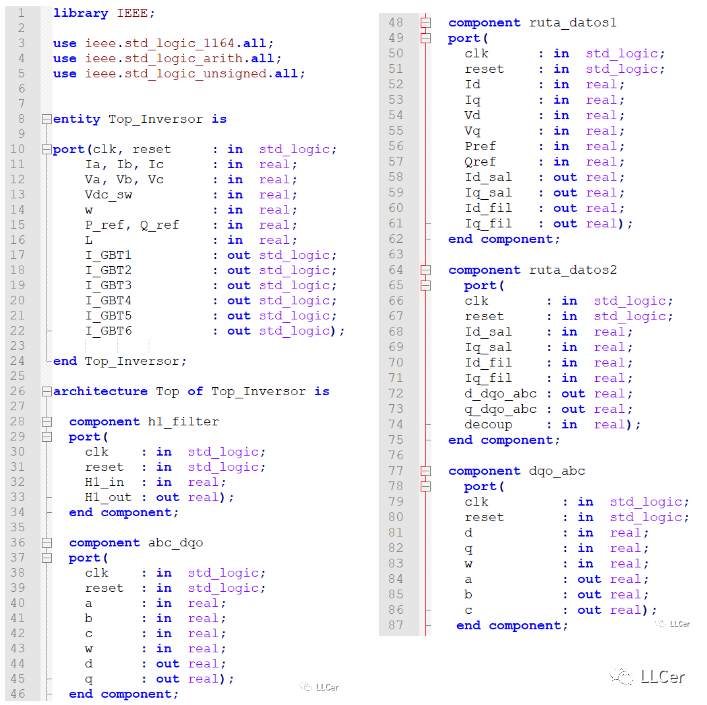

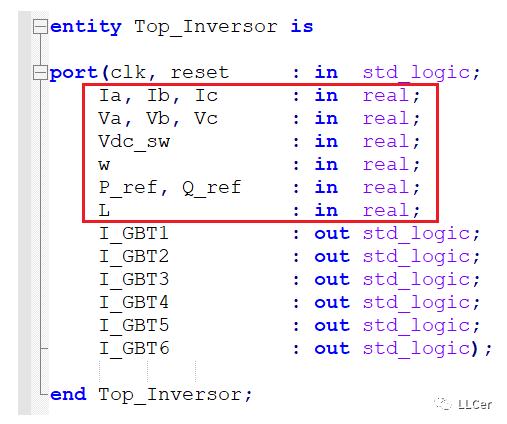

簡單分析下此例子vhdl代碼的構(gòu)成,采用自頂向下的設(shè)計(jì)方法,頂層entity是Top_Inversor,7輸入6輸出,輸入分別是3相電壓、3相電流、直流母線電壓、角頻率、有功和無功給定、電感量,輸出分別是6個(gè)管驅(qū)動(dòng)。

Top_Inversor由5個(gè)子元件h1_filter、abc_dqo、ruta_datos1、ruta_datos2、dqo_abc構(gòu)成(其中Ruta_Datos2下層會調(diào)用h2_filter),使用4個(gè)進(jìn)程P_WT、P_BIEST、CMP、GEN并行運(yùn)行。(vhdl文件夾中還有一個(gè)ModCouplerTemporaryFile.vhd,此文件與該例子運(yùn)行無關(guān)。)

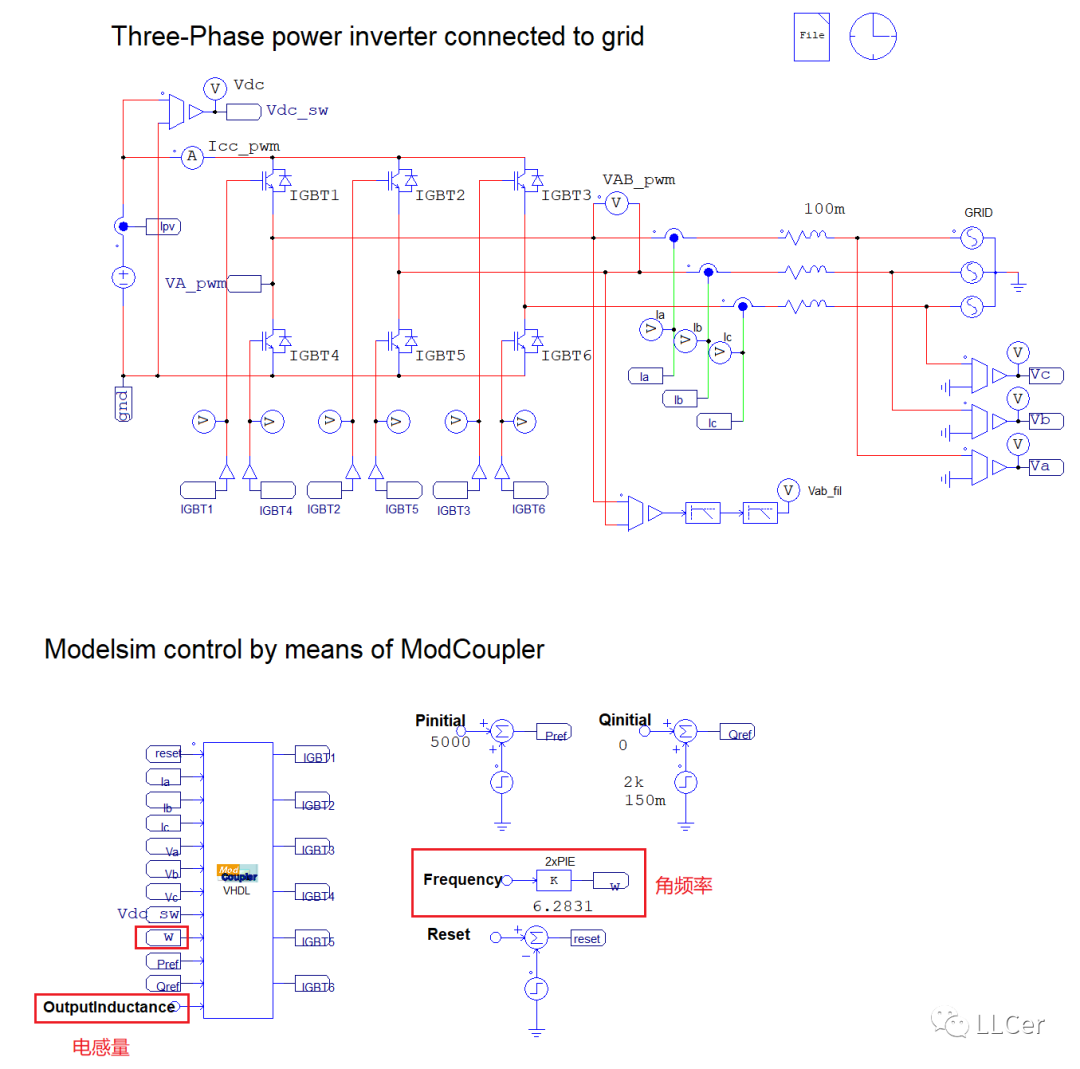

打開PSIM模型文件inverter.psimsch后,顯示如下

VHDL模塊在左下角,控制部分全VHDL實(shí)現(xiàn),電流環(huán)為dq0坐標(biāo)下帶耦合的配置,其需要的輸入?yún)?shù)角頻率和電感量,由右上角File提供。

該例子是有點(diǎn)特殊的,無ADC,浮點(diǎn)類型的模擬量直接作為輸入經(jīng)過一階數(shù)字濾波器h1_filter后直接參與控制運(yùn)算,數(shù)據(jù)類型均為浮點(diǎn)。 這在仿真中是無問題的。

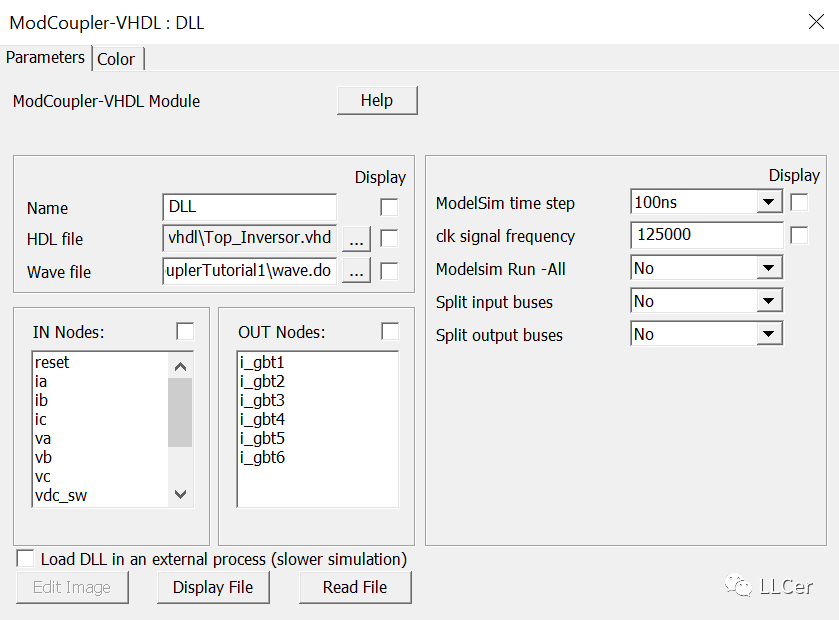

雙擊打開VHDL模塊,得到如下窗口,HDL file是指定頂層實(shí)體.vhd文件,Wave file 是指定wave.do文件(在例子文件夾內(nèi)),右側(cè)需要設(shè)置ModelSim仿真步長。

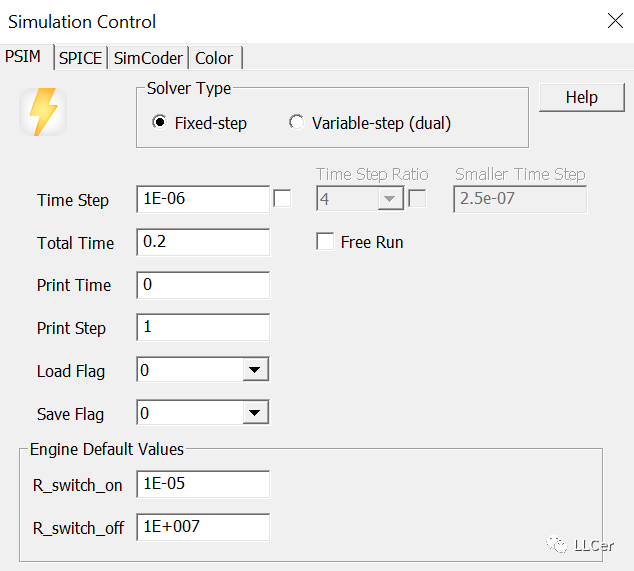

雙擊PSIM模型界面右上角的鐘表圖標(biāo),得到如下窗口,仿真參數(shù)設(shè)置。

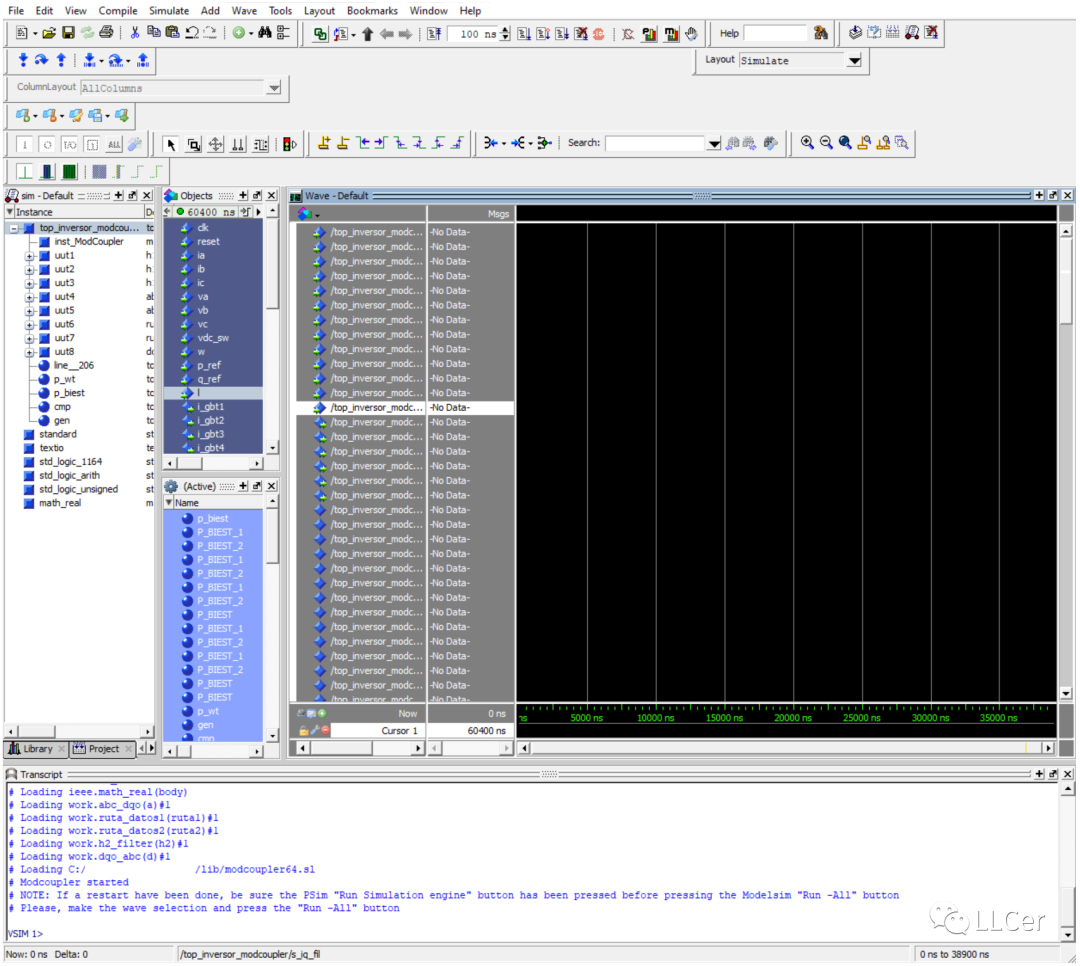

保持原有參數(shù)及設(shè)置不變,接下來看下運(yùn)行過程及結(jié)果。點(diǎn)擊PSIM運(yùn)行圖標(biāo)后,稍等幾秒,會自動(dòng)調(diào)用QuestaSim/ModelSim軟件

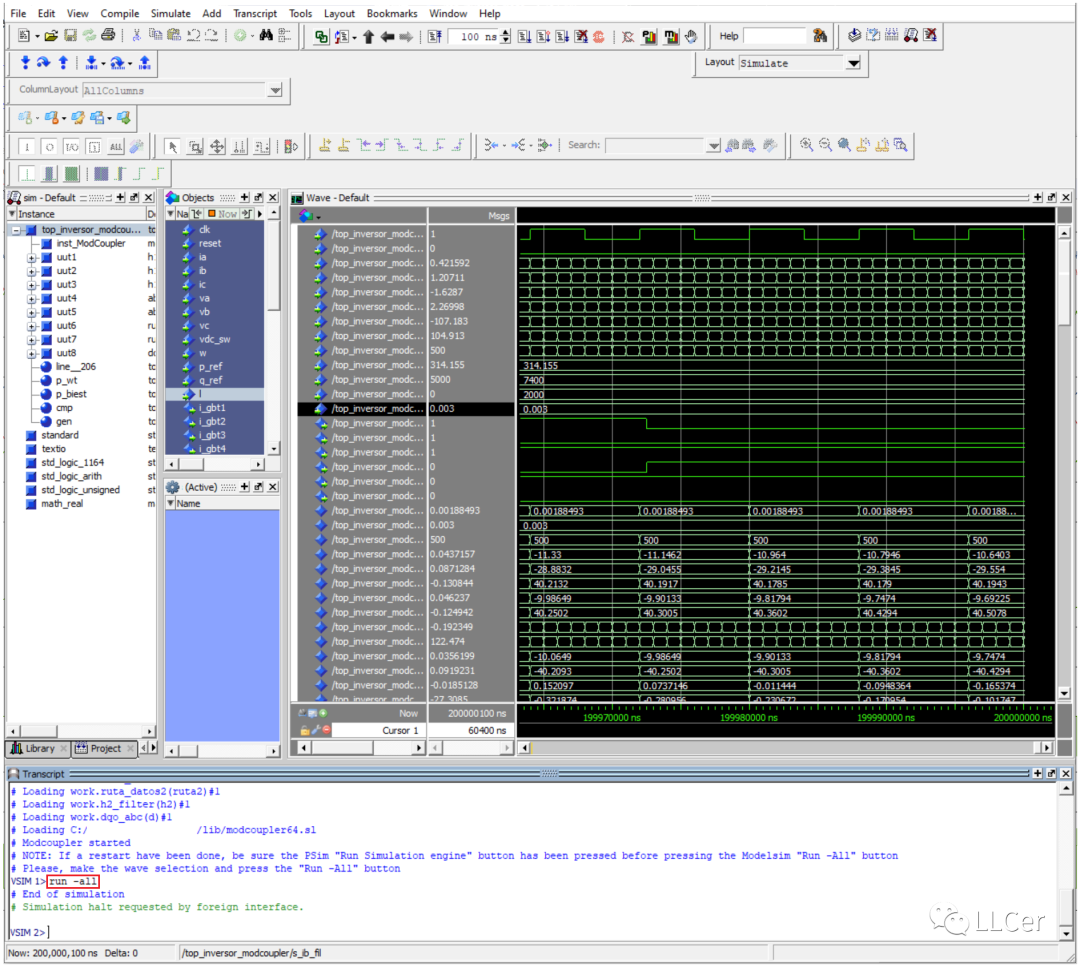

需要在QuestaSim/ModelSim命令行輸入run -all啟動(dòng)ModelSim仿真,同時(shí)PSIM也開始真正運(yùn)行。ModelSim環(huán)境下各輸入輸出變量中間量是自動(dòng)添加的,運(yùn)行完后可在ModelSim窗口進(jìn)行波形操作和變量查看,操作和ModelSim完全一樣。

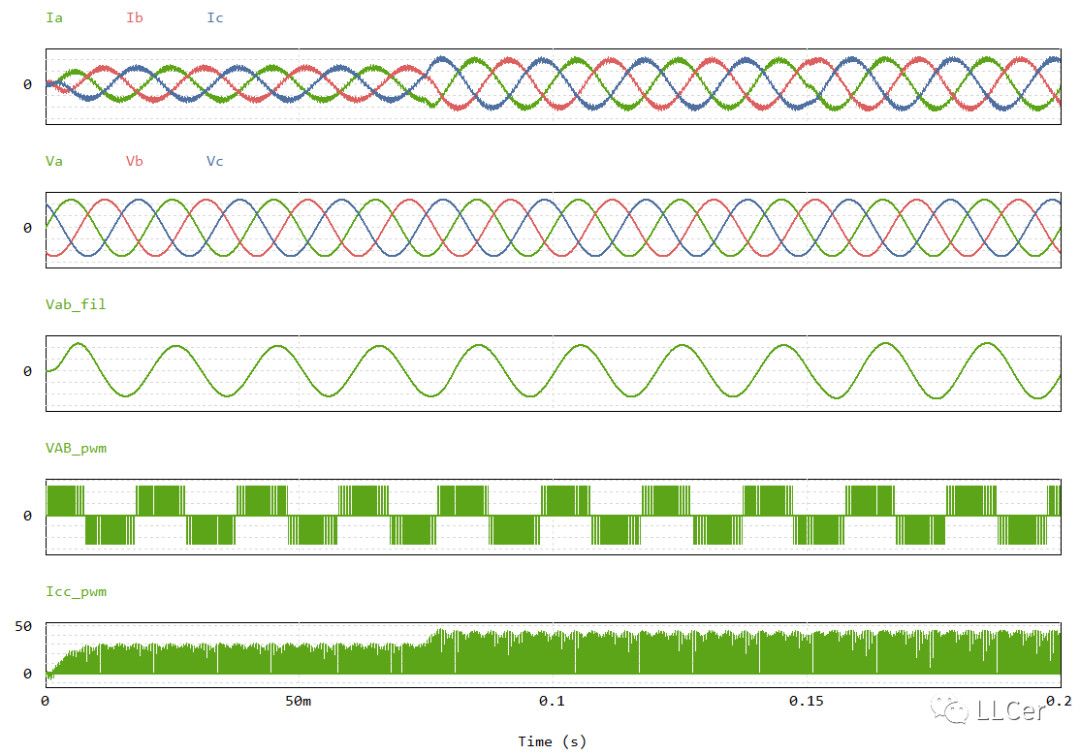

仿真時(shí)間200ms,得到如下PSIM結(jié)果

二,

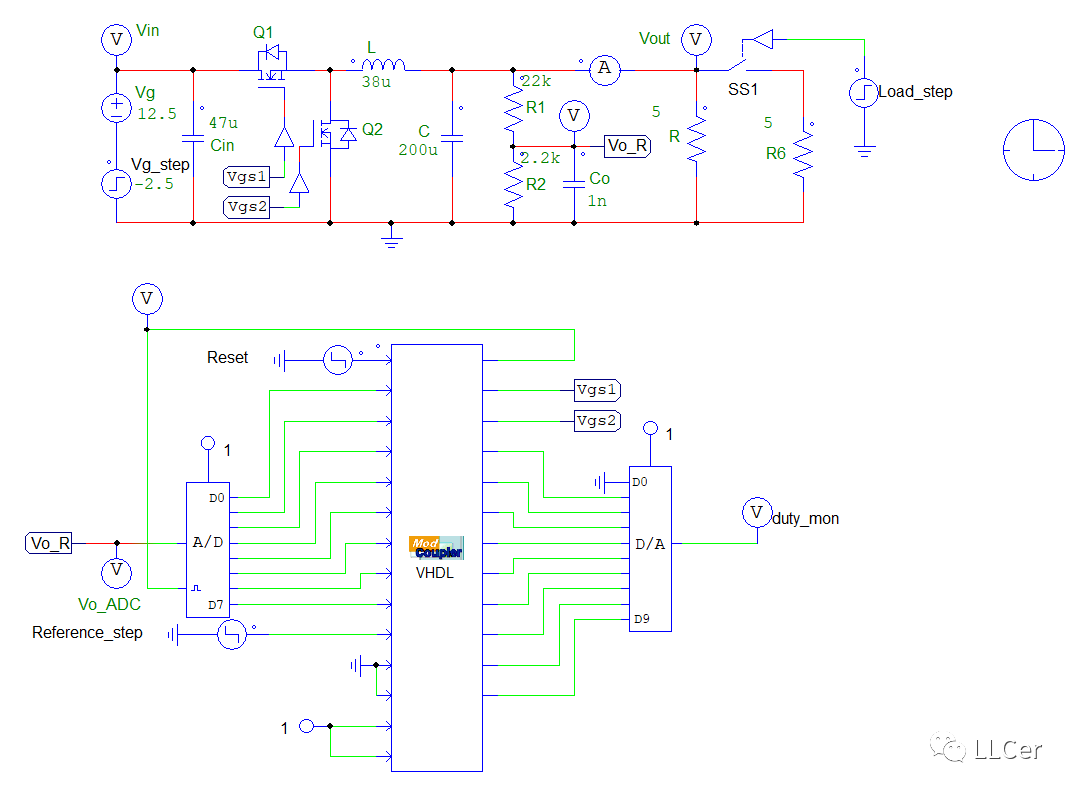

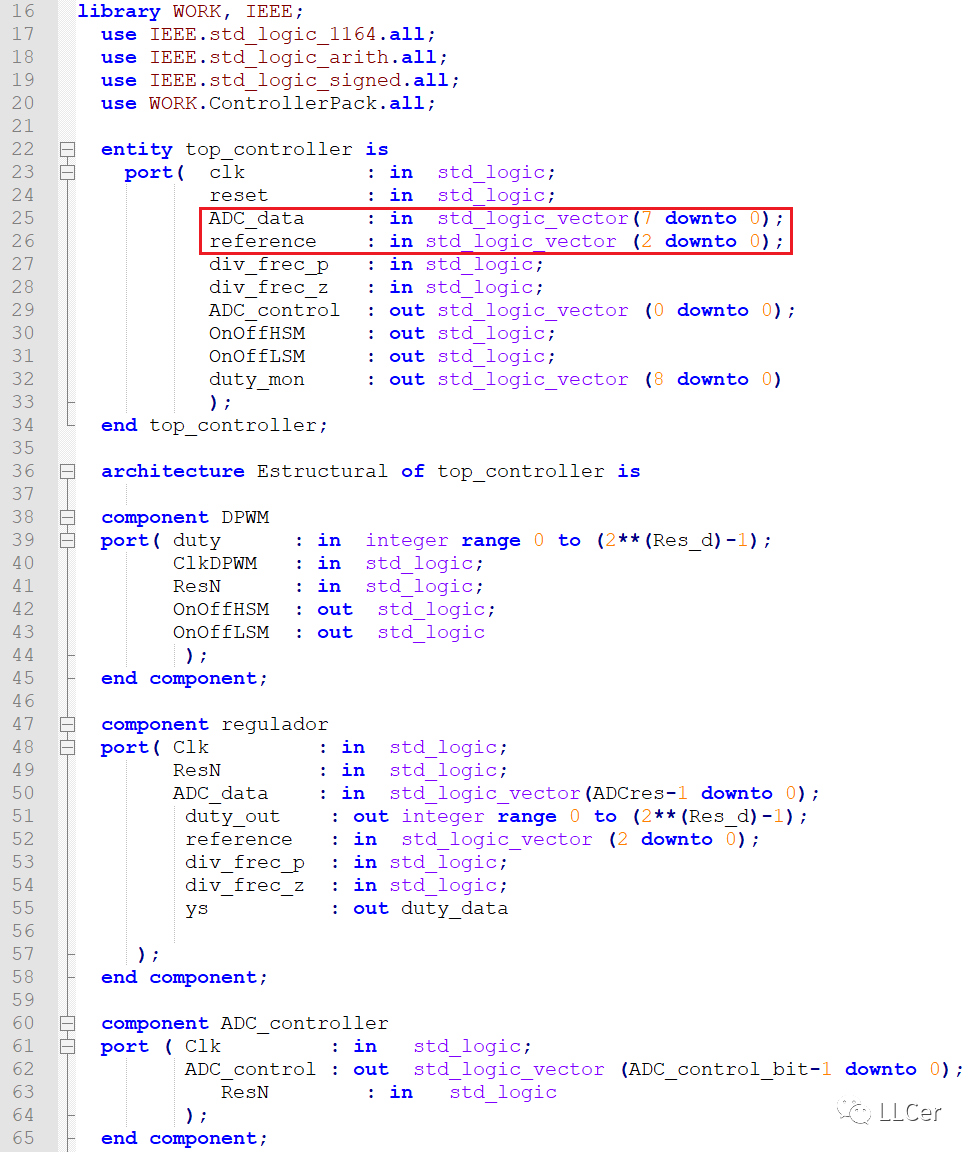

現(xiàn)在打開Tutorial2文件夾,看下同步buck的例子,使用了PSIM自帶的ADC模塊,vhdl代碼結(jié)構(gòu)為頂層實(shí)體top_controller,由ADC_controller、regulador、DPWM子元件構(gòu)成。

此例是真正的數(shù)字控制。ADC_controllerwei ADC模塊的時(shí)序控制器,regulador(文件名compensator)是控制計(jì)算單元,包含誤差項(xiàng)計(jì)算、環(huán)路補(bǔ)償計(jì)算等,DPWM是發(fā)波單元,輸出同步buck的上下管驅(qū)動(dòng)信號。compensator_pack.vhd是用戶程序包,里面是用戶數(shù)據(jù)類型定義和一些常數(shù)定義。

三,

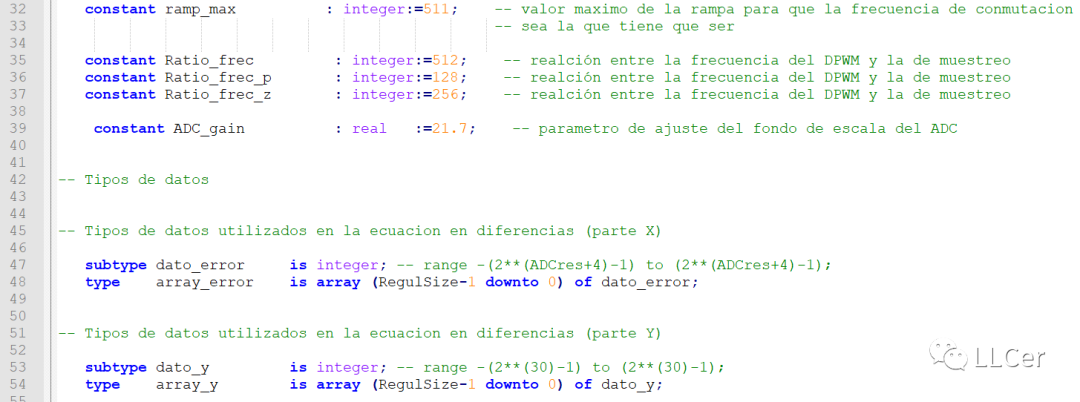

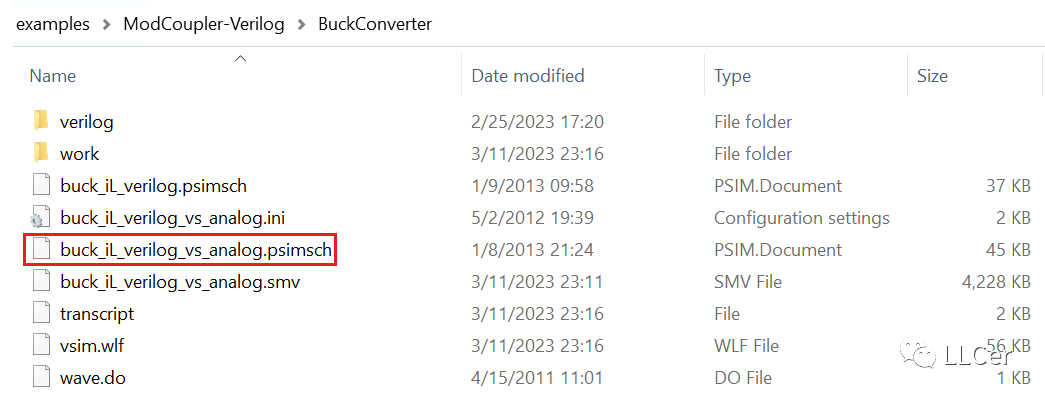

再來看下verlogHDL例子,軟件自帶一個(gè)buck,文件夾內(nèi)容如下

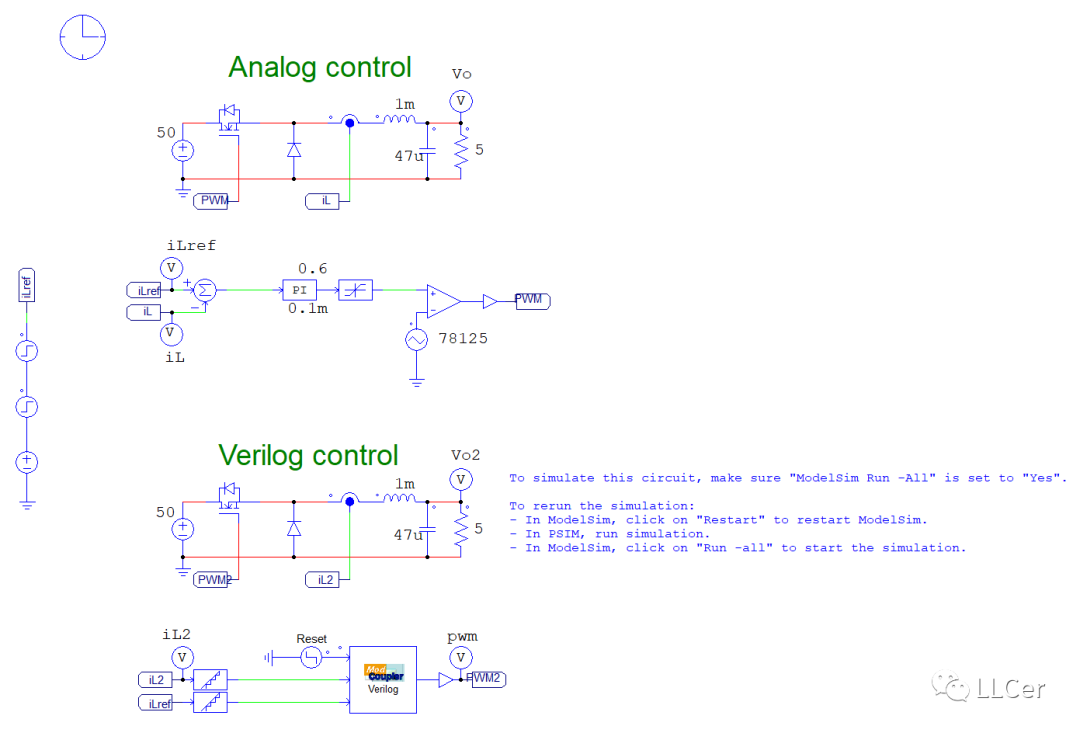

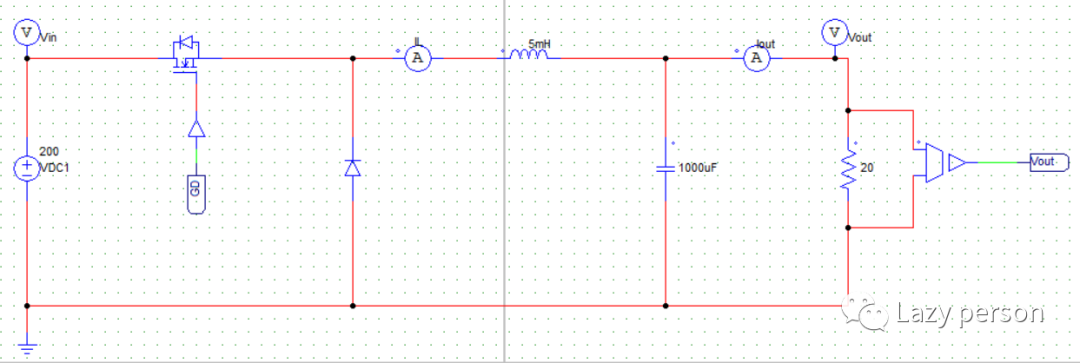

雙擊打開buck_iL_verilog_vs_analog.psimsch,其中包含兩個(gè)buck,上部分為模擬實(shí)現(xiàn)的,下半部分是verilogHDL實(shí)現(xiàn)的。

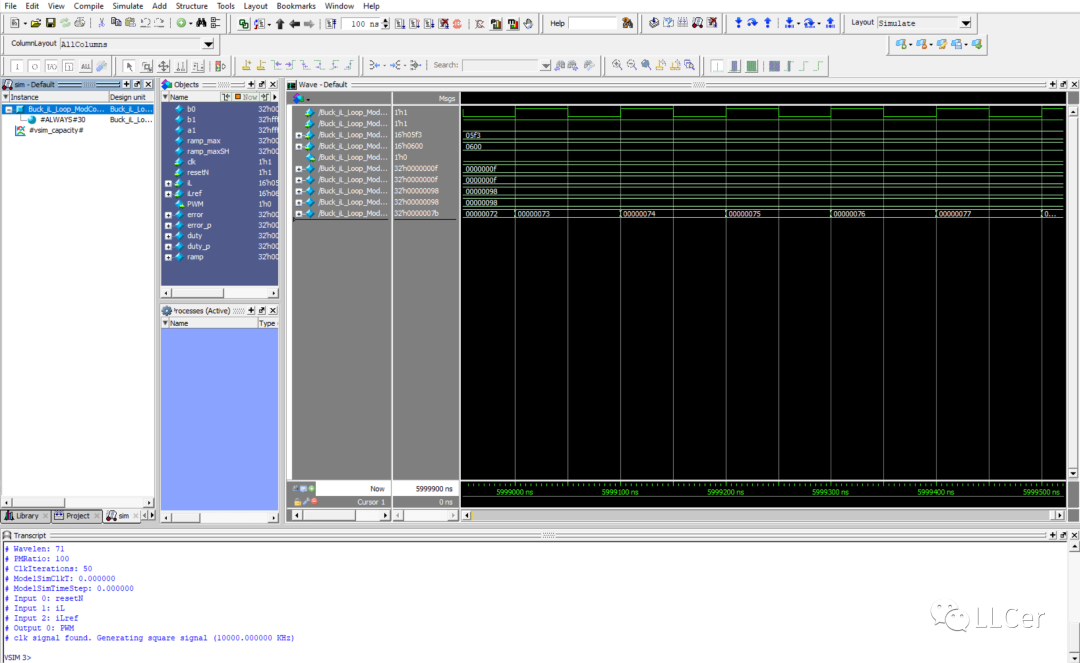

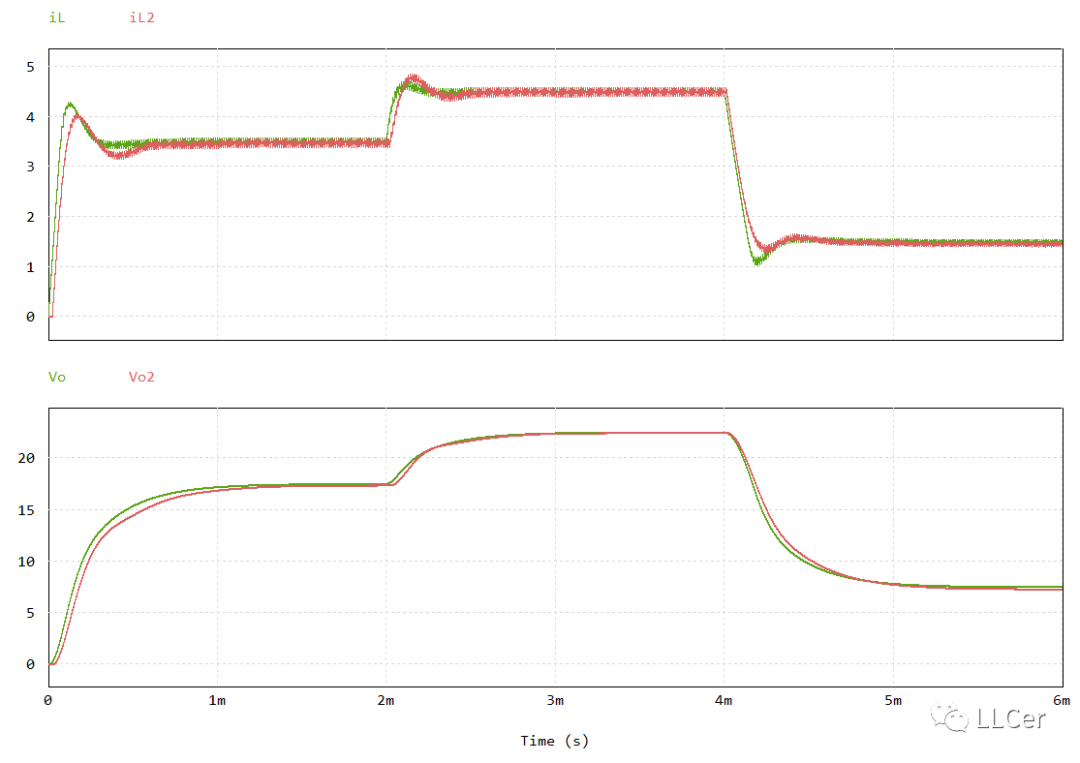

點(diǎn)擊PSIM運(yùn)行按鈕后,同樣是調(diào)用ModelSim,此例的ModelSim是自動(dòng)運(yùn)行的,仿真完成后結(jié)果如下

紅色線(后綴2)是verilog實(shí)現(xiàn)的結(jié)果

四,PSIM的其他功能

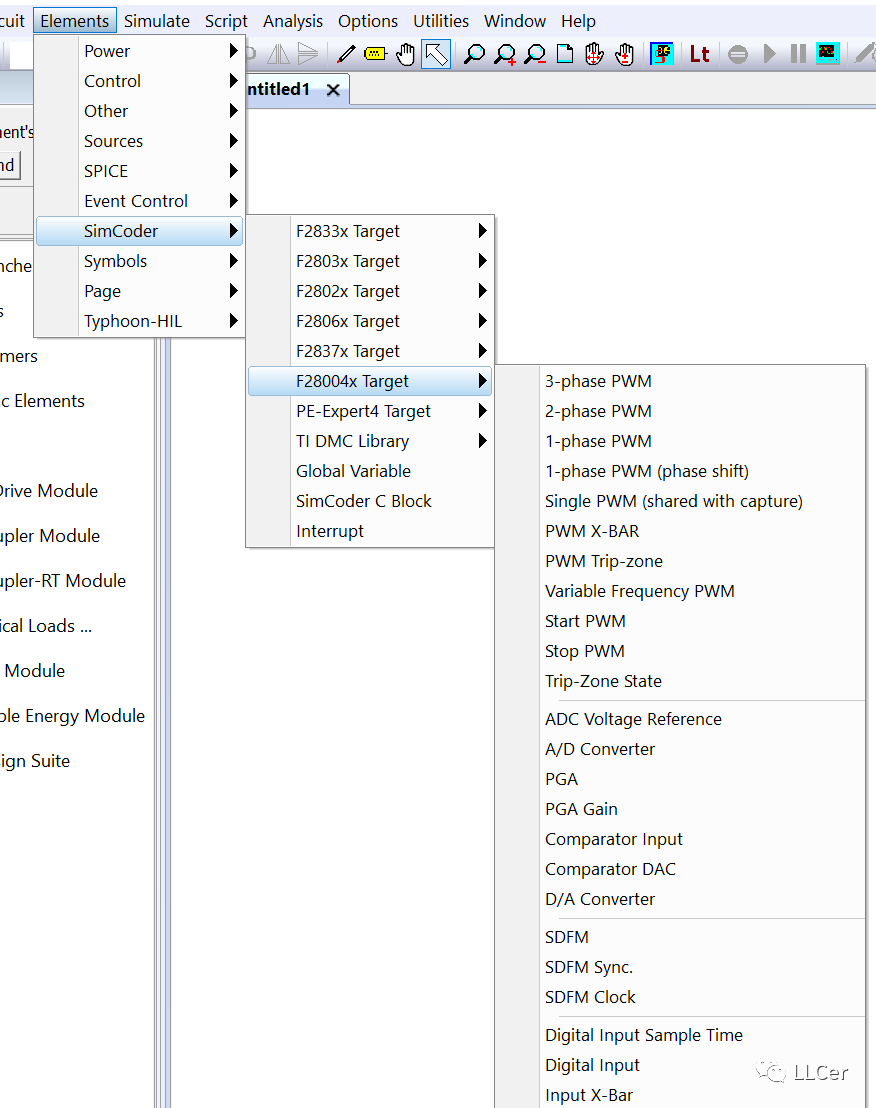

1,C2000 DSP的聯(lián)合仿真及代碼自動(dòng)生成,PSIM提供可在圖形界面下交互參數(shù)的DSP外設(shè)模塊,同時(shí)支持這些外設(shè)模塊及完整工程的C代碼自動(dòng)生成。

C2000 DSP外設(shè)模塊的位置

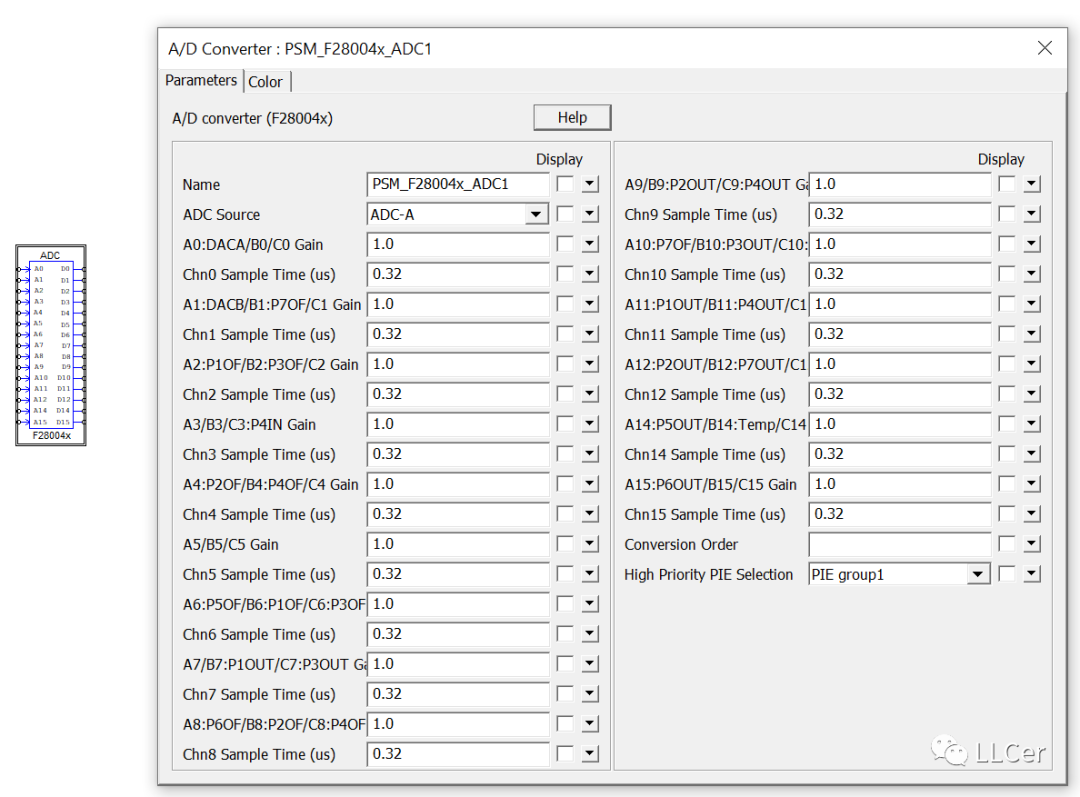

F280049的ADC用戶界面

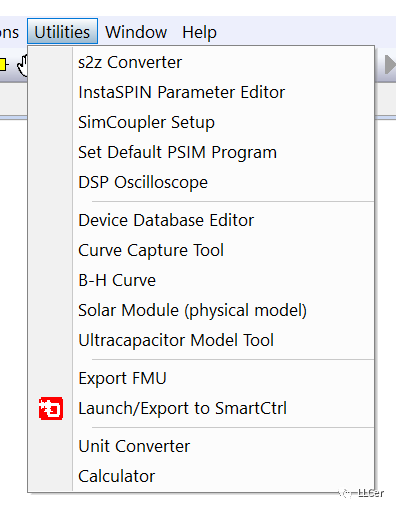

2,Utilities菜單

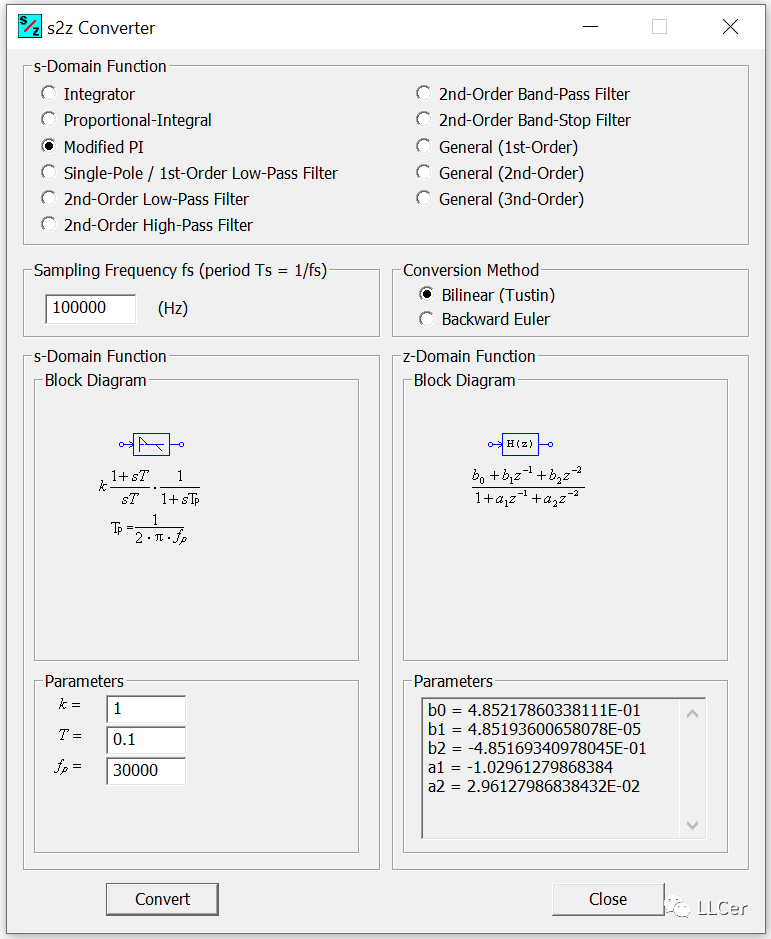

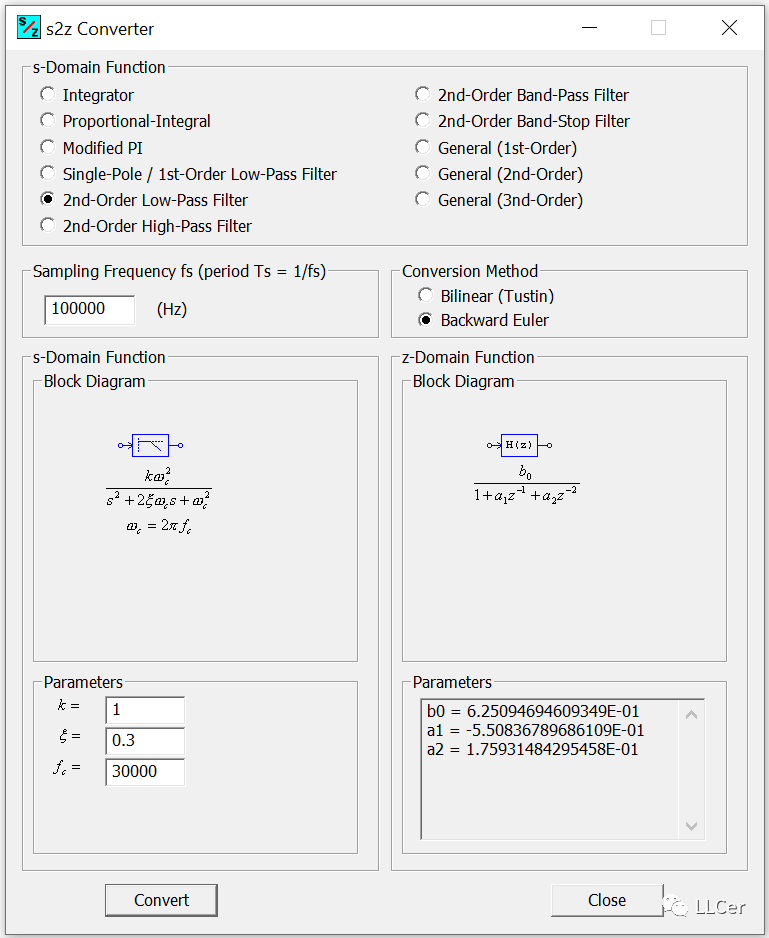

s2z轉(zhuǎn)換工具,提供了常用濾波器/補(bǔ)償器的s2z轉(zhuǎn)換功能,z系數(shù)14位小數(shù),雙線性和后向差分兩種變換方法

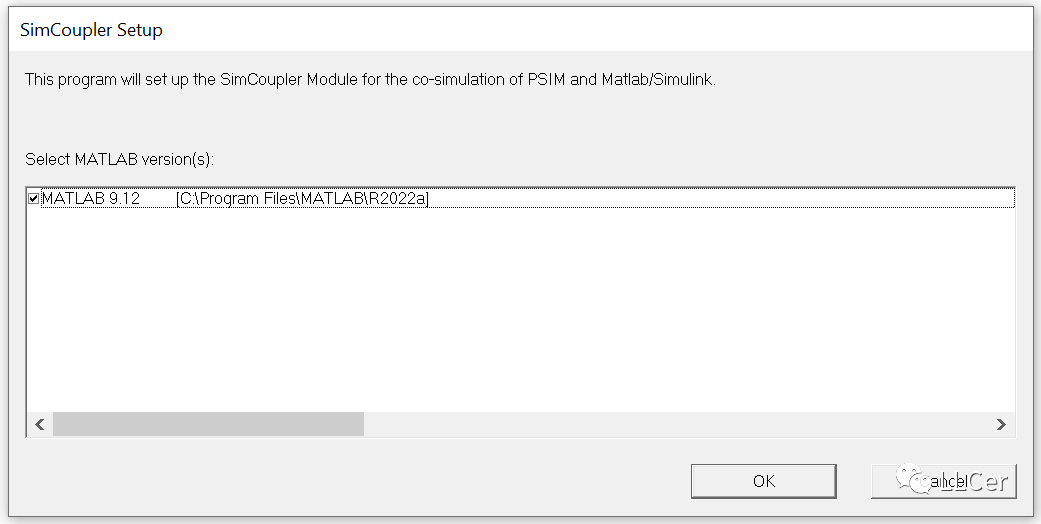

SimCoupler目錄設(shè)置工具,雙擊打開時(shí)PSIM自動(dòng)檢測其他安裝環(huán)境,打開后可選擇其他環(huán)境的安裝目錄。

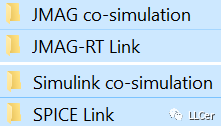

PSIM目前支持JMAG(電磁有限元軟件)、matlab/simulink、SPICE仿真器聯(lián)合仿真。需要注意的是上述HDL聯(lián)合仿真中QuestaSim/ModelSim不需要在此處設(shè)置,調(diào)用ModelSim仿真器是通過運(yùn)行compile.bat批處理來實(shí)現(xiàn)的。

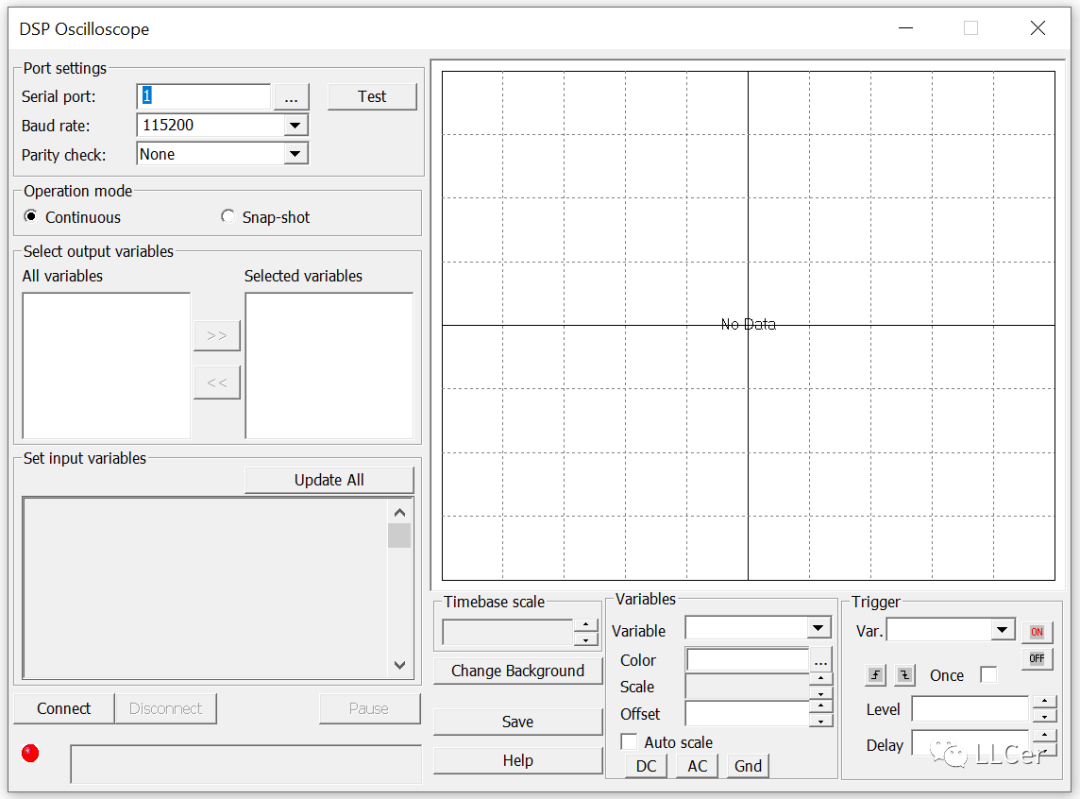

DSP示波器工具

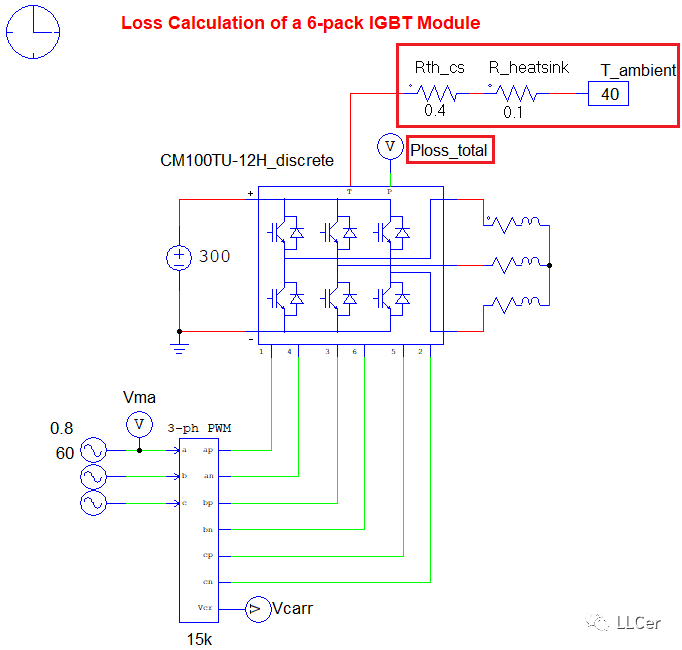

功率管參數(shù)編輯工具,PSIM支持功率器件參數(shù)編輯及新增,此模型支持功率管的結(jié)溫仿真,基于Eon、Eoff的查表,結(jié)合功率管的熱阻網(wǎng)絡(luò)模型,可在時(shí)域仿真的同時(shí)得到損耗和結(jié)溫結(jié)果。

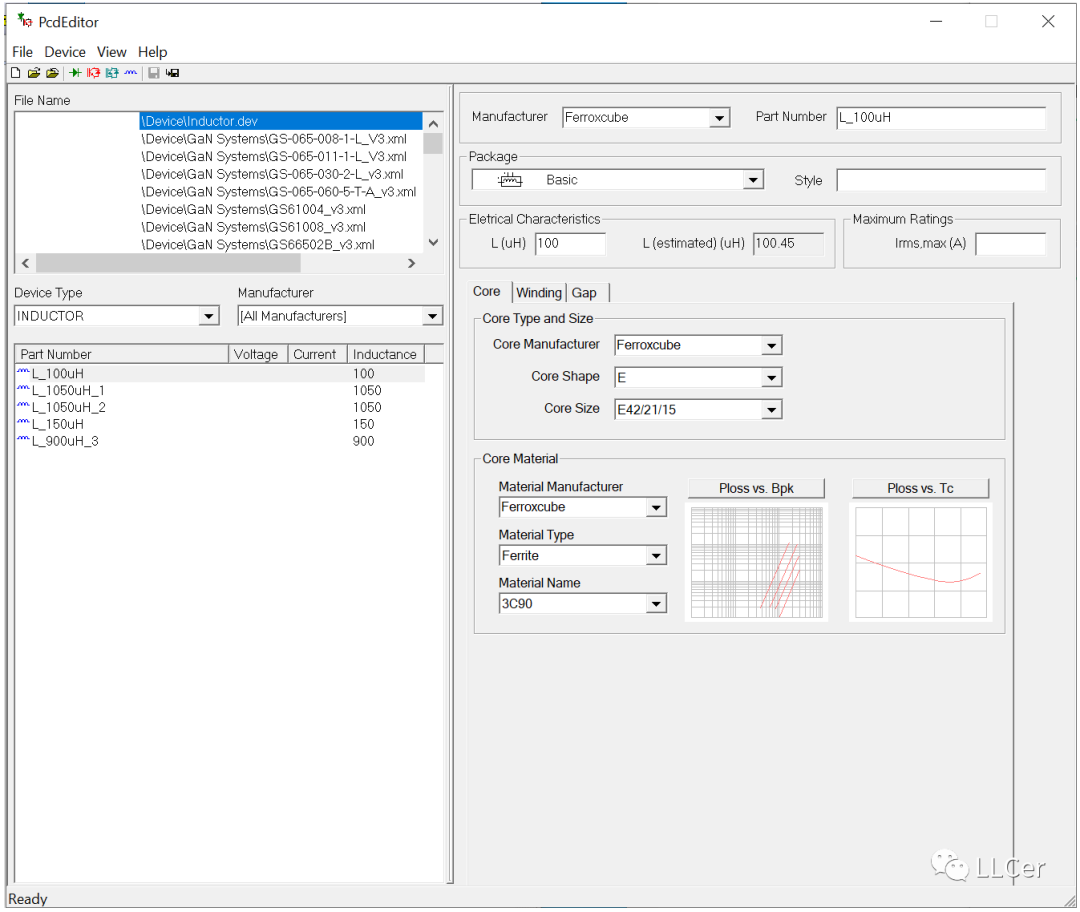

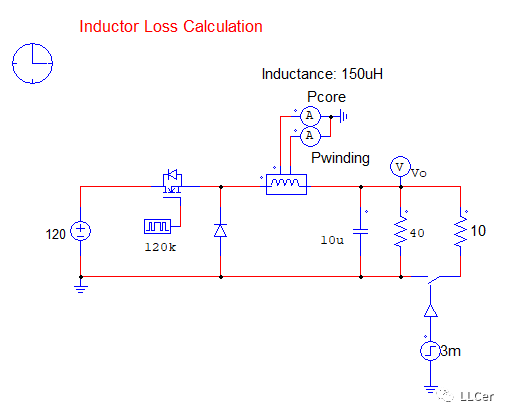

也支持電感損耗

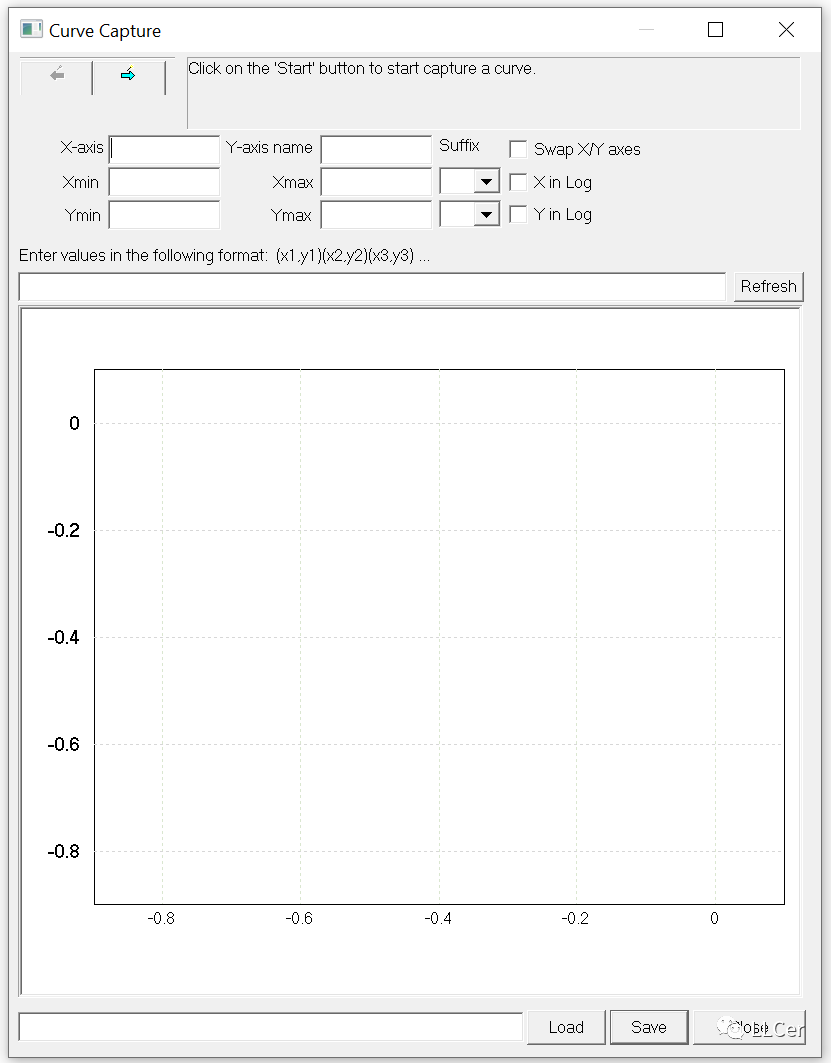

圖片曲線捕獲工具,提取元器件規(guī)格書中曲線上的數(shù)據(jù),可配合功率管參數(shù)編輯工具使用

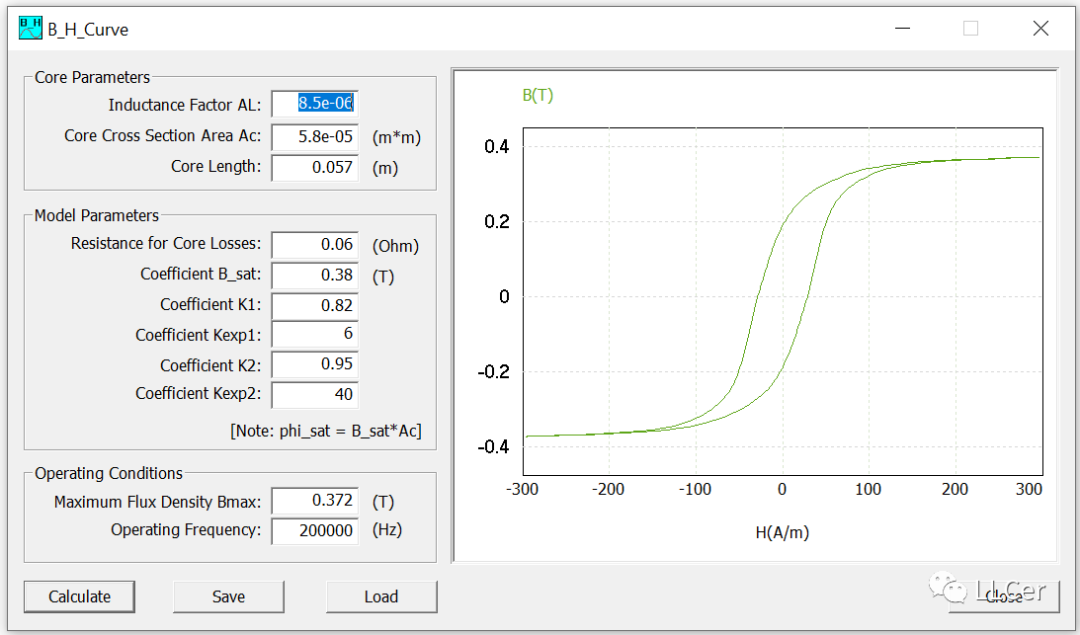

BH曲線編輯工具,對磁芯損耗進(jìn)行建模,可配合功率管參數(shù)編輯工具中電感模型使用

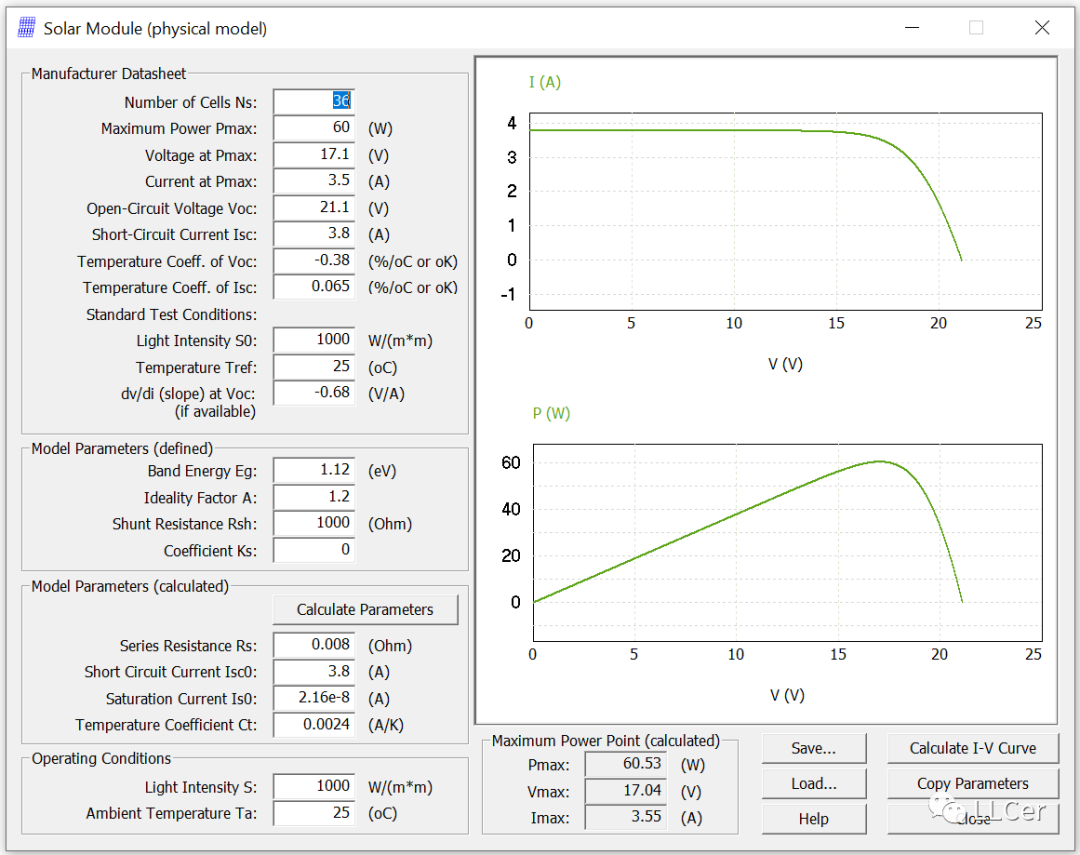

光伏板模擬工具,可配合PSIM仿真

超級電容模擬工具,,可配合PSIM仿真

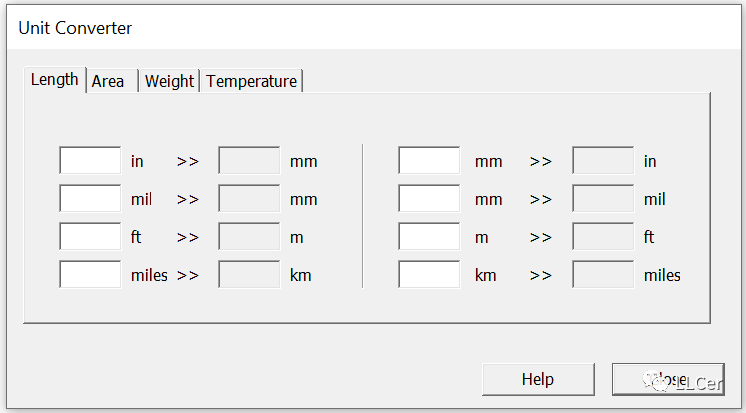

單位轉(zhuǎn)換工具

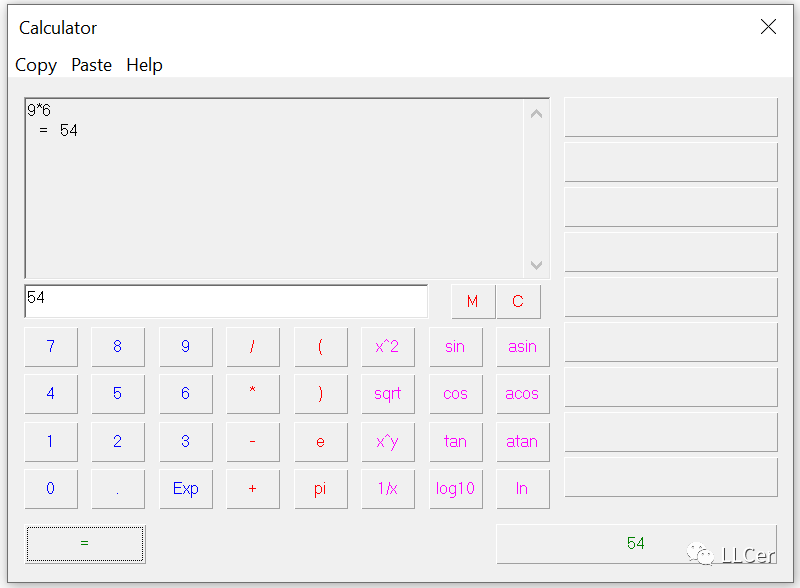

計(jì)算器

-

逆變器

+關(guān)注

關(guān)注

293文章

4863瀏覽量

210176 -

PSIM

+關(guān)注

關(guān)注

24文章

41瀏覽量

27012 -

時(shí)序控制器

+關(guān)注

關(guān)注

0文章

19瀏覽量

11297 -

HDL語言

+關(guān)注

關(guān)注

0文章

48瀏覽量

9111 -

ADC模塊

+關(guān)注

關(guān)注

1文章

19瀏覽量

11206

發(fā)布評論請先 登錄

基于PSIM的電壓型BUCK仿真

psim中可以用dll和f28335模塊聯(lián)合仿真嗎?

TEXTIO及其在VHDL仿真中的應(yīng)用

在Altium Designer的Protel中進(jìn)行混合信號

在Protel DXP中進(jìn)行FPGA設(shè)計(jì)和仿真

VHDL-AMS格式熱電聯(lián)合仿真

基于PSIM軟件的BUCK仿真研究

在PSIM軟件中進(jìn)行LLC設(shè)計(jì)驗(yàn)證的方法

如何使用PSIM進(jìn)行電子電路仿真?

在PSIM軟件中進(jìn)行LLC設(shè)計(jì)驗(yàn)證

基于PSIM的Buck模型數(shù)字化仿真

在PSIM中進(jìn)行VHDL的聯(lián)合仿真

在PSIM中進(jìn)行VHDL的聯(lián)合仿真

評論