FinFET工藝的復雜工藝和布局規則對合成過程中的決策有很大的影響。

多年來,從一家主要的硅代工廠發布新的工藝節點需要您更新合成流程的想法是不可能實現的。綜合使用了庫中可用的時序、面積和功率模型,這是討論的開始和結束。

隨著物理合成的到來,在合成流程中可以考慮物理效應,前端設計人員開始詢問發布新工藝節點時會發生什么變化。

物理合成的好處是改進了基于合成中實際物理信息的時序相關性,包括粗略放置和平面圖。合成中的這種附加信息可實現準確的時序估計,使優化引擎能夠專注于正確的路徑,并在整個流程中提供更好的相關性和收斂性。隨著物理合成的占據主導地位并成為主流合成流程,這在幾個方面顯著改變了用戶的期望。現在,用戶期望輸出網表的質量在性能、功耗和面積(PPA)方面會更好。他們希望它更適合物理實現,使用合成提供的放置種子來減少路由擁塞。布局優化后與結果的相關性在時序、面積、布線和功耗方面將更加緊密。放置和布線的交接目標是實現更好的 PPA 和收斂設計流程。理想情況下,除非實際設計規范發生變化,否則移交給物理實現團隊的網表不應返回給 RTL 設計人員。

隨著FinFET工藝節點進入主流生產用途,復雜的工藝和布局規則對合成過程中的決策有更大的影響。綜合解決方案和用戶改進 PPA 的新選擇包括層感知時序優化、通過支柱插入實現的性能和 EM、使用非默認布線規則以及旨在改善高利用率區域的引腳可訪問性等指標的特殊單元。物理合成現在需要了解工藝技術參數以及布局和布線規則,以便為物理實現生成更好的網表。因此,在針對不同的工藝節點進行合成時,物理合成需要了解并以不同的方式操作。

設計編譯器 圖形化前饋設計實施指南,以推動逐步收斂最終 PPA 目標的物理實現流程。最新版本的Design Compiler Graphic可以在具有更好PPA特性的單元與具有更好的擁塞和引腳可訪問性的單元之間進行權衡,將網絡分配給不同的布線層以管理關鍵時序路徑,添加電遷移和性能通孔,導出非默認布線規則和無數其他技術,以提出滿足所需目標的設計。當設計網表和物理引導傳遞到布局和布線工具時,生成的設計PPA與綜合工具的預測非常匹配。

從 7nm 開始,在較小的節點上繼續,設計編譯器圖形由硅代工廠驗證,以便在每個新工藝節點上進行部署準備。這意味著綜合工具已得到增強,以支持最新的工藝規則、布局、布線、功率和時序要求,并且了解并考慮了新節點的物理影響。

那么,回到最初的問題,每個高級節點設計都需要這種在綜合過程中考慮所有物理實現因素的新流程嗎?答案是肯定的。對于最新工藝節點上的設計,您需要習慣于為每個新工藝節點更新工具版本和合成流程/腳本,以實現最佳的PPA和最快的收斂。

審核編輯:郭婷

-

布線

+關注

關注

9文章

797瀏覽量

85092 -

編譯器

+關注

關注

1文章

1661瀏覽量

50185 -

FinFET

+關注

關注

12文章

257瀏覽量

91138

發布評論請先 登錄

模塊是否獨立于運行程序?

獨立于內核的fireflyP GPIO使用方法介紹

S32G3 ASIL性能內核和實時內核是否可以視為獨立于ASIL-B?在什么條件下?

Xilinx A7芯片內部獨立于邏輯單元的專用存儲器

eVTOL飛行器滿足航空運輸需求的獨立于跑道技術解決方案

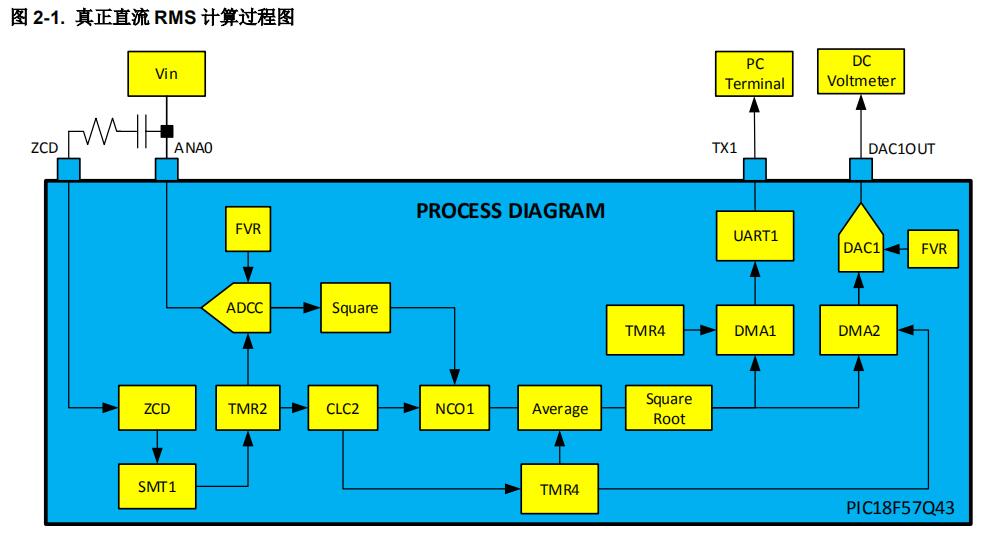

采用獨立于內核的外設實現真正的直流RMS測量

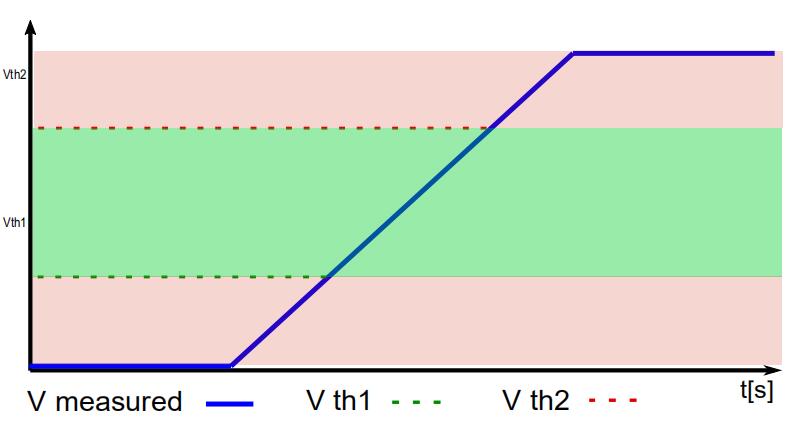

使用單個比較器實現獨立于內核的電壓窗口信號檢測

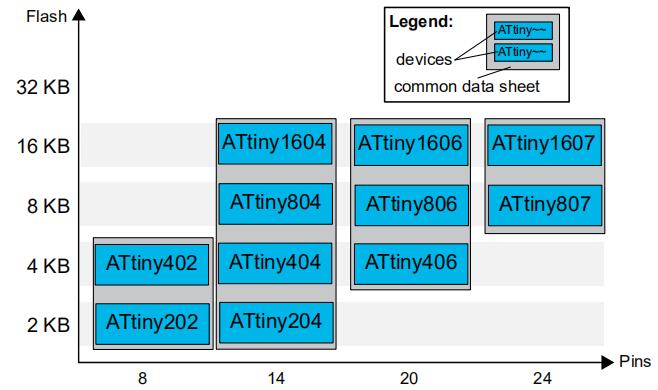

AVR單片機上的獨立于內核的外設入門指南

AN4889-使用獨立于內核的外設實現Peltier冷卻金屬板

合成是否仍然獨立于工藝

合成是否仍然獨立于工藝

評論