跨時鐘域是FPGA設計中最容易出錯的設計模塊,而且一旦跨時鐘域出現問題,定位排查會非常困難,因為跨時鐘域問題一般是偶現的,而且除非是構造特殊用例一般的仿真是發現不了這類問題的。

優秀的FPGA工程,系統工程師一定會進行合理的時鐘域劃分,理想的情況是整個工程只有一個時鐘,完全不考慮跨時鐘域的問題,但是實際的工程中一般是不存在的,因此合理的跨時鐘域設計是很有必要的。

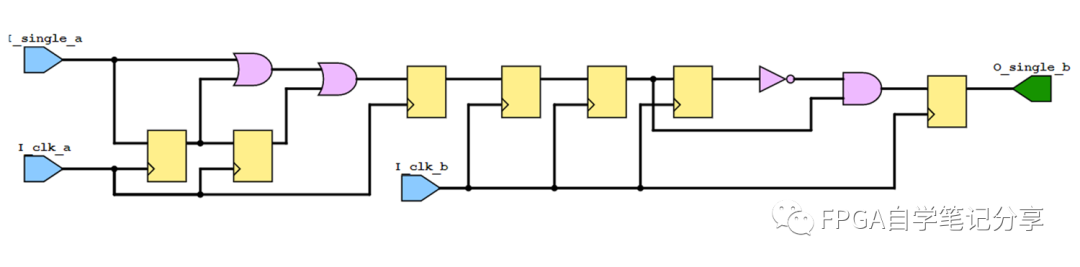

單bit慢變信號跨時鐘域方法:

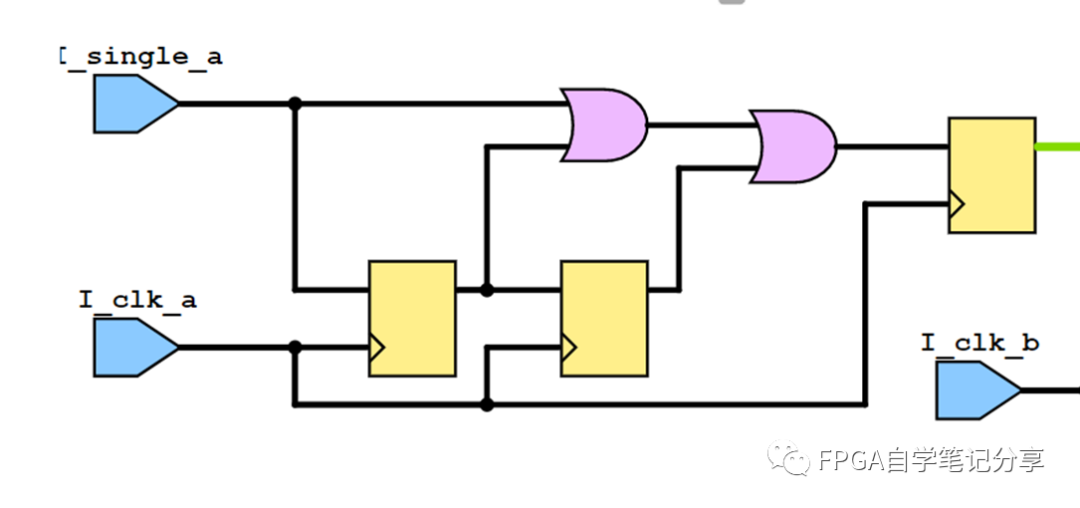

1、信號展寬

2、跨時鐘打兩拍

3、取沿

// ============================================================

// File Name: cm_cdc_1bit

// VERSION : V1.0

// DATA : 2022/9/28

// Author : FPGA干貨分享

// ============================================================

// 功能:單bit慢變信號跨時鐘域模塊

// ============================================================

`timescale 1ns/1ps

module cm_cdc_1bit (

input wire I_clk_a , ///輸入時鐘a

input wire I_clk_b , ///輸入時鐘b

input wire I_single_a , ///a時鐘輸入信號

output reg O_single_b ///b時鐘輸出信號

);

// ============================================================

// wire reg

// ============================================================

reg S_clr_flag_a_d0 ;

reg S_clr_flag_a_d1 ;

reg S_clr_flag_a_all ;

reg S_clr_flag_b_d0 ;

reg S_clr_flag_b_d1 ;

reg S_clr_flag_b_d2 ;

reg S_clr_b_posedge ;

// ============================================================

// a時鐘域

// ============================================================

always @(posedge I_clk_a)

begin

S_clr_flag_a_d0 <= I_single_a;

S_clr_flag_a_d1 <= S_clr_flag_a_d0;

end

///跨時鐘域之前先擴展

always @(posedge I_clk_a)

S_clr_flag_a_all <= I_single_a|S_clr_flag_a_d0|S_clr_flag_a_d1 ;

// ============================================================

// b時鐘域

// ============================================================

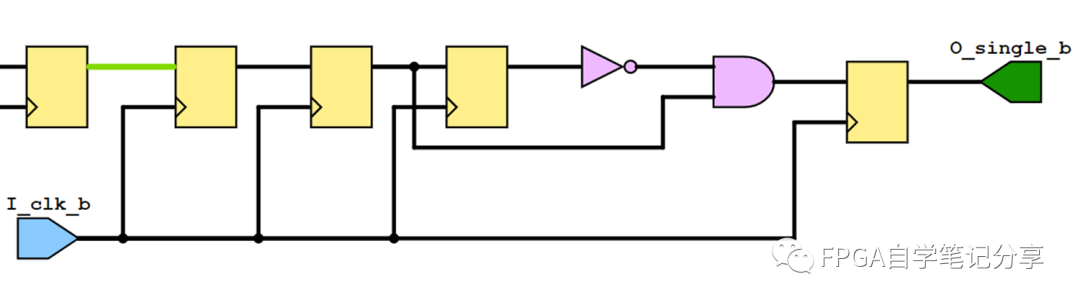

///使用第二個時鐘進行打拍

always @(posedge I_clk_b)

begin

S_clr_flag_b_d0 <= S_clr_flag_a_all;

S_clr_flag_b_d1 <= S_clr_flag_b_d0 ;

S_clr_flag_b_d2 <= S_clr_flag_b_d1 ;

end

//打兩拍之后的信號進行處理

always @(posedge I_clk_b)

O_single_b <= (!S_clr_flag_b_d2)&(S_clr_flag_b_d1);

endmodule

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615324 -

FPGA設計

+關注

關注

9文章

428瀏覽量

27199 -

信號

+關注

關注

11文章

2846瀏覽量

77996 -

bit

+關注

關注

0文章

48瀏覽量

32396 -

時鐘域

+關注

關注

0文章

53瀏覽量

9753

發布評論請先 登錄

相關推薦

熱點推薦

FPGA跨時鐘域處理方法(一)

FPGA跨時鐘域處理方法(一)

評論