2021 年,PCI-SIG? 發布了最新版本的 PCI Express? 規范 PCIe? 6.0。PCIe 6.0 的原始數據速率為 64 GT/s,帶寬是 PCIe 5.0 (32GT/s) 的兩倍,可滿足行業對高速、低延遲互連的需求。它是一種可擴展的互連解決方案,適用于數據中心、AI/ML、高性能計算 (HPC) 和汽車等數據密集型市場。

在本博客中,我們將討論 PCIe 6.0 中的前向糾錯 (FEC) 機制、為什么需要它,以及 Synopsys 提供哪些驗證解決方案來涵蓋此功能。

什么是 PAM-4?

PCIe 6.0 使用數據速率為 4GT/s 的 PAM-64 信令,而不是以較低數據速率使用的不歸零 (NRZ) 信令。這意味著發送和接收的信號現在將在一個單位間隔內具有四個不同的電壓電平(2位)編碼,從而產生三個眼睛。這是因為 64GT/s 的 NRZ 信令會導致 32GHz 的奈奎斯特速率增加,此時信道損耗可能很大;因此,PAM-4 以 64GT/s 的速度使用以減少信道損耗,因為它具有與 16GT/s 數據速率相同的奈奎斯特速率 (32GHz)。

然而,這需要權衡,因為眼睛高度和眼睛寬度會減小,這使得接收器容易出錯。預計誤差在車道中以突發形式發生,并且預計車道之間也會有一定程度的相關性。因此,與PAM-4信令相關的誤碼率(BER)預計將遠高于較低數據速率的10^-12目標。

為什么需要 FEC 以及如何完成?

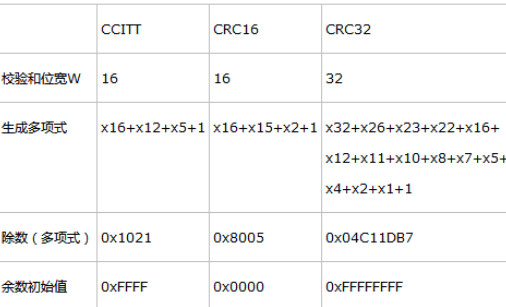

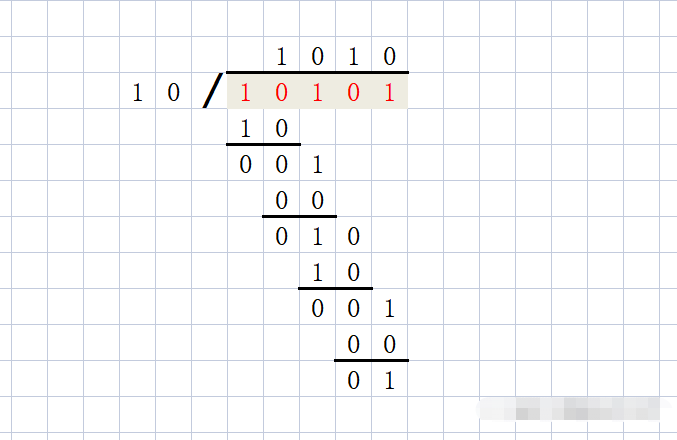

FEC 用于緩解數據流中的高 BER。由于 FEC 在固定代碼大小上工作,因此 FLIT 用于傳輸數據流中的 TLP 和 DLP。FEC 的延遲和復雜性隨著要更正的字節數呈指數級增長。為了保持較低的延遲(<2ns)和復雜性,使用了輕量級FEC,它可以糾正單字節錯誤。這與用于錯誤檢測的強循環冗余校驗 (CRC) 相結合,以產生高可靠性結果。此外,預編碼可用于最大限度地減少突發中的錯誤。

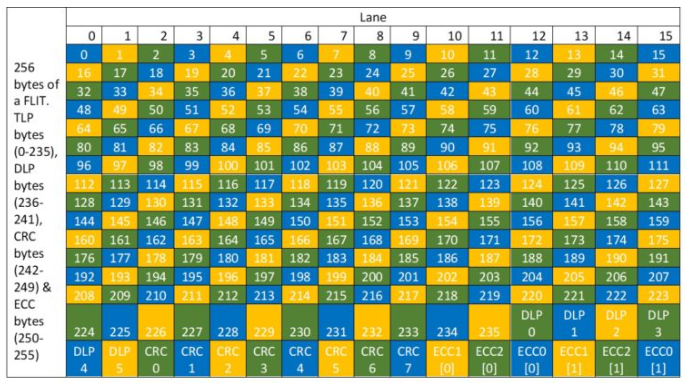

FLIT 的大小為 256 字節,其中 236 字節用于 TLP,6 字節用于 DLP,8 字節用于 CRC,6 字節用于錯誤檢查和糾正 (ECC)。CRC 的 8 個字節保護 TLP 和 DLP 字節,但不保護 ECC 字節。6 字節的 ECC 保護整個 FLIT,包括 CRC 字節。

FEC 代碼是 3 路交錯的,如下表所示。每種顏色代表一個 ECC 組,其字節以相同的顏色標記。因此,一個通道中的三個連續字節屬于三個不同的 ECC 組。因此,通道中長度為 <=16 的突發誤差不會影響每組中的多個字節,并且每個 ECC 可以糾正單個字節錯誤。

表 1:x16 鏈路上的 FLIT 交錯

在接收器上,ECC 解碼器對其相應的代碼組執行校正,并根據需要報告錯誤狀態。然后進行CRC檢查,以確定是否接受收到的FLIT。如果 CRC 檢查失敗,FLIT 將重放并得到糾正。

如果檢測到無法糾正的錯誤,CRC 檢查將失敗并導致否定確認 (NAK),然后重播。優化是可能的,例如,可能無法重放具有僅 NOP TLP 的 FLIT,也可以僅重放錯誤 FLIT。

可糾正和不可糾正的錯誤:

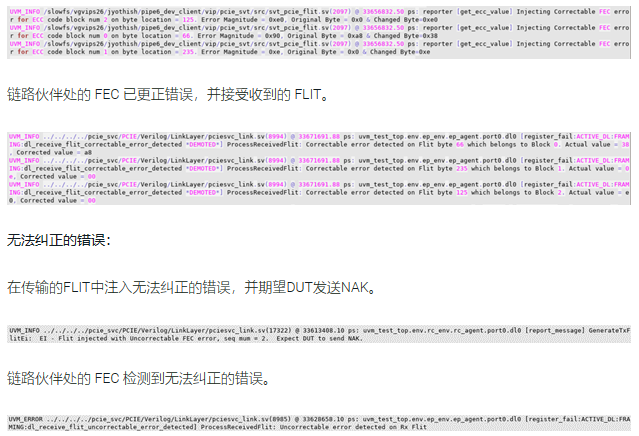

以下是 Synopsys 驗證 IP for PCIe 6.0 成績單的快照,說明了 FLIT 中可糾正和不可糾正的錯誤。

可糾正的錯誤:

在傳輸的FLIT中注入可糾正的錯誤。

驗證可糾正和不可糾正的錯誤以確保 FEC、CRC 和重放機制正常工作非常重要。

最終,輕量級 FEC 與強大的 64 位 CRC 相結合,適用于 10^-6 的 FBER,即使具有高通道相關性。每個 FLIT 的重試概率約為 5×10^-6,時間失敗 (FIT) 幾乎為 0。

適用于 PCIe 6.0 的 Synopsys 驗證 IP 旨在解決關閉 SoC 數據可靠性方面所需的所有驗證復雜性。 數據可靠性是一個非常理想的系統方面,PCIe 6.0 的目標用戶正在尋找在系統級別驗證其 SoC 的解決方案。在 SoC 上運行系統級有效負載需要更快的基于硬件的預硅解決方案。基于 Synopsys IP 的 Synopsys 事務處理器可實現快速驗證硬件解決方案,包括用于驗證用例的 Synopsys ZeBu? 仿真系統和 Synopsys HAPS? 原型系統。

Synopsys 協議驗證解決方案與 Synopsys 驗證系列產品原生集成,包括 Synopsys Verdi? 調試器以及使用 Synopsys VC Execution Manager 進行回歸管理和自動化。

Synopsys 一直是 PCIe 規范的主要貢獻者之一,并繼續為 PCIe 6.0 和 Testsuite 提供業界首個采用 Synopsys 驗證 IP 的驗證解決方案。

此外,適用于 PCIe 6.0 的 Synopsys DesignWare IP 包括控制器和 PHY 解決方案,支持早期開發 PCIe 6.0 片上系統 (SoC) 設計。

審核編輯:郭婷

-

解碼器

+關注

關注

9文章

1153瀏覽量

40998 -

crc

+關注

關注

0文章

200瀏覽量

29626 -

PCIe

+關注

關注

15文章

1270瀏覽量

83357

發布評論請先 登錄

相關推薦

PSoC 4 循環冗余校驗 (CRC)

基于FPGA的循環冗余校驗實驗系統

驗證PCIe 6.0中的輕量級前向糾錯和強循環冗余校驗功能

驗證PCIe 6.0中的輕量級前向糾錯和強循環冗余校驗功能

評論