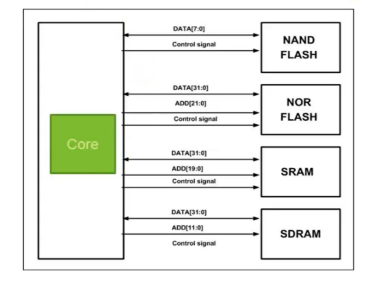

Soc芯片的片外存儲器

FLASH設計實例

**NOR FLASH **

NAND FLASH

主存儲器的主要技術指標

- 存儲容量

存儲器可以容納的二進制信息量(尋址空間,由CPU的地址線決定) - 實際存儲容量: 在計算機系統中具體配置了多少內存。

- 存取速度: 存取時間是指從啟動一次存儲器操作到完成該操作所經歷的時間,也稱為讀寫周期;

- 可靠性: 用平均故障間隔時間來衡量MTBF(mean time between failure)

- 功耗: 每個存儲元消耗功率的大小

DRAM :

SRAM : 地址、數據和控制信號在同一上升沿變化

外部存儲器控制器

連接在AHB總線上,管理片外存儲器,如FLASH、SRAM、DDR等;

EMI在SOC芯片中的位置:

EMI控制器

片選信號和地址范圍,普通SRAM接口

- 提供6個可配置的片選信號:CSA、CSB、CSC、CSD、CSE、CSF,用來實現對ROM、SARM、NOR FLASH 的片選。其中CSE、CSF與SDRAM片選信號復用;

- 每個片選支持的最大尋址范圍為64M

- 每個片選可配的起始地址

- 啟動片選可選配16位總線或者32位總線

支持SDRAM接口

- 提供2個相互獨立的與SRAM復用的片選信號:SD_CSF,SD_CSF,作為SDRAM的片選,與SRAM、ROM、FLASH的片選CSE CSF復用

- 每個片選支持有4個bank的SDRAM,支持同時激活active最多達4個bank

- 提供選用的SDRAM型號,tRC,tRP,tRCD,CAS latency可配置

支持NAND FLASH接口

- 提供一個片選:nand_cs

- 只支持整個pape的操作,也就是每次讀寫都是一個pape。通過配置地址寄存器,控制字寄存器,然后對數據寄存器進行訪問,從而完成對NAND FLASH的操作

- 支持從NAND FLASH直接進行系統啟動

- 支持ECC校驗的一位糾錯

- 只支持8位數據線的NAND FLASH

SRAM控制器IP的設計

接口信號:

- AHB slave接口信號

- 輸出給SRAM的控制器

AHB接口(標準slave)

片外SRAM存儲器接口

SRAM控制器結構

SRAM控制器模塊劃分

- **BUS **接口

- 處理AHB接口信號

- 區分寄存器操作,存儲器操作

- 寄存器

- 控制存儲器地址范圍、位寬

- 控制存儲器訪問方式

- **SRAM **狀態機

- 處理有效的存儲器操作

- 考慮各種傳輸類型:Burst長度、數據位寬、讀寫操作

- 控制輸出信號的時序

- **SRAM **接口

- 根據狀態機的控制輸出相應的信號給SRAM

- 匹配總線位寬和SRAM位寬

SRAM控制器狀態機的設計

- IDLE狀態

- 讀數據準備狀態

- 寫數據狀態

- 寫數據準備狀態

- 寫數據狀態

EMI模塊設計小結

- 掛在AHB總線上

- 接口信號

- AHB總線接口信號

- 片外存儲器SRAM控制信號

- 子模塊劃分

- 總線接口模塊

- SRAM接口模塊

- SRAM狀態機:控制寄存器的訪問方式、時序、傳輸類型等

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

存儲器

+關注

關注

38文章

7599瀏覽量

165696 -

cpu

+關注

關注

68文章

10995瀏覽量

214853 -

soc

+關注

關注

38文章

4284瀏覽量

220829 -

計算機系統

+關注

關注

0文章

290瀏覽量

24442

發布評論請先 登錄

相關推薦

如何實現嵌入式ASIC和SoC的存儲器設計?

基于傳統六晶體管(6T)存儲單元的靜態RAM存儲器塊一直是許多嵌入式設計中使用ASIC/SoC實現的開發人員所采用的利器,因為這種存儲器結構非常適合主流的CMOS工藝流程,不需要增添任

發表于 08-02 06:49

哪種類型的同步SRAM用于外部存儲器?

,ADSC引腳做什么。所有同步SRAM存儲器將具有這些引腳。從數據表中,我知道,例如,直接訪問與處理器或DMA控制器的使用。除了QDR、DDR存儲器

發表于 08-15 07:02

外部數據存儲器的擴展實驗

外部數據存儲器的擴展一、實驗目的二、實驗內容三、實驗步驟四、C代碼如下五、實驗結果六、實驗體會一、實驗目的掌握單片機系統外部存儲器電路的擴展方法掌握單片機

發表于 12-07 11:24

如何選擇DSP芯片的外部存儲器?

如何選擇DSP芯片的外部存儲器?DSP的速度較快,為了保證DSP的運行速度,外部存儲器需要具有一定的速度,否則DSP訪問外部

發表于 04-07 08:45

?2026次閱讀

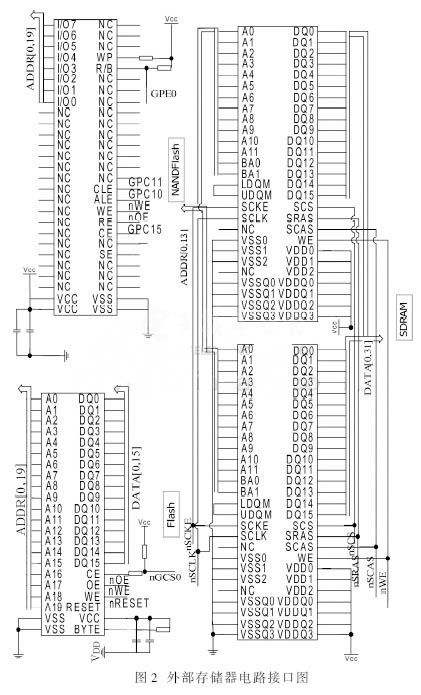

外部存儲器電路接口電路圖

外部存儲器

為了滿足物流PDA的應用需要,本系統采用Flash、SDRAM、NAND Falsh存儲器。

閃速存儲器(Flash Memory)的主要特點是掉電保存信息。它

發表于 11-13 14:52

?3176次閱讀

存儲器之外 東芝還有哪些值得關注的地方?

受到眾多買家競購東芝存儲器業務的影響,近段時間以來東芝公司的媒體曝光率極高。如果拋去對于東芝存儲器業務將花落誰家的紛擾猜測,將目光對準市場與產品技術,可以發現近年來東芝公司除去存儲器之外

發表于 04-26 10:36

?1498次閱讀

什么是外部存儲器

磁表面存儲器——磁表面存儲器,它們都是利用涂敷在載體表面薄層磁性材料來記錄信息的,載體和表面磁性材料統稱為記錄介質。

存儲密度——磁表面存儲器單位長度或單位面積磁層表面所能

外部存儲器是ROM還是RAM

外部存儲器通常指的是計算機系統中除了主存(RAM)以外的存儲設備,如硬盤、固態硬盤(SSD)、USB閃存驅動器、光盤等。它們主要用于長期存儲

外部存儲器有哪些

外部存儲器是指用于存儲數據的獨立設備,它們通常與計算機或其他電子設備連接,并提供額外的存儲空間,允許用戶在不改變主設備內部存儲的情況下保存和

SOC設計之外部存儲器

SOC設計之外部存儲器

評論