1 UVM中引入phase的原因

代碼的書寫順序會影響代碼的實現(代碼之間存在依賴關系,如代碼B依賴于代碼A),所以區分出build_phase、connect_phase等,讓被依賴的phase(代碼A)先執行,依賴的phase(代碼B)后執行,這樣可以解決因代碼順序雜亂可能會引發的問題。

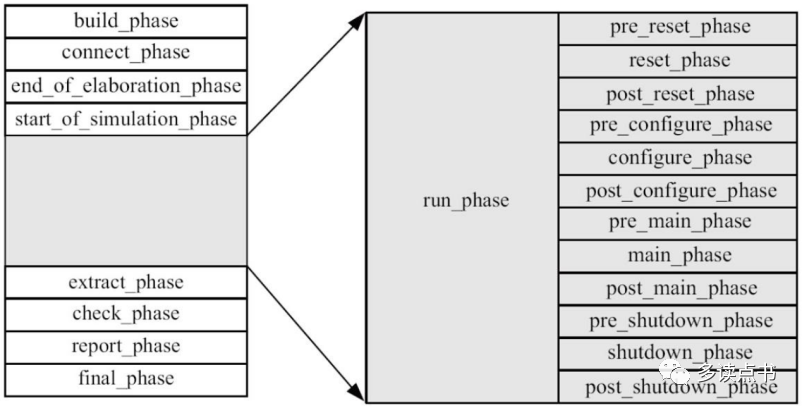

2 UVM中phase的執行順序

- 按上圖所示順序自上而下執行不同phase,且同類phase執行完后, 需要進行等待同步 ,然后才能執行下一類phase。而同類phase中不同component在UVM樹種執行順序如下:

- build_phase:在UVM樹中依據自上而下的順序啟動,順序運行

- 除了build_phase之外的function phase:在UVM樹中依據自下而上的順序啟動,順序運行

- task_phase:在UVM樹中依據 自下而上的順序啟動,同時運行 (通過fork...join_none多線程方式)

- 直系關系的component

- 兄弟關系的component:在UVM樹中依據字典序

- 叔侄關系的component:在UVM樹中依據深度優先(即優先侄component執行)

3 UVM中引入objection的原因

上文提到代碼會依據不同phase的順序自上而下執行,且同類phase執行完后, 需要進行等待同步 。而引入objection就是為了更好的控制同類phase中執行代碼的同步用的。

4 UVM中引入domain的原因

體現不同component的獨立性。例如,把兩個時鐘域隔開, 這樣兩個時鐘域內的各個動態運行( run_time) 的phase就可以不必同步了。使用該機制可以搭建多時鐘域DUT的UVM仿真平臺。

注意:domain 只能隔離run-time的phase , 對于其他phase, 其實還是同步的, 即兩個domain的run_phase依然是同步的, 其他的function phase也是同步的。

-

UVM

+關注

關注

0文章

182瀏覽量

19468 -

時鐘域

+關注

關注

0文章

53瀏覽量

9751 -

DUT

+關注

關注

0文章

190瀏覽量

12875

發布評論請先 登錄

IC驗證"UVM驗證平臺加入factory機制"(六)

IC驗證“UVM驗證平臺加入objection機制和virtual interface機制“(七)

數字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

什么是uvm?uvm的特點有哪些呢

談談UVM中的uvm_info打印

UVM中seq.start()和default_sequence執行順序

UVM驗證平臺執行硬件加速

Modelsim uvm庫編譯及執行

UVM中phase的執行順序

UVM中phase的執行順序

評論