端口

端口是模塊與外界交互的接口,對外部環境而言,模塊內部是不可見的,對模塊的調用只能通過端口連接進行

端口基本語法約定如下:

端口必須被聲明

端口聲明不可重復

端口聲明既可在端口列表內也可在列表外

模塊間的數據只能通過端口進行

端口聲明

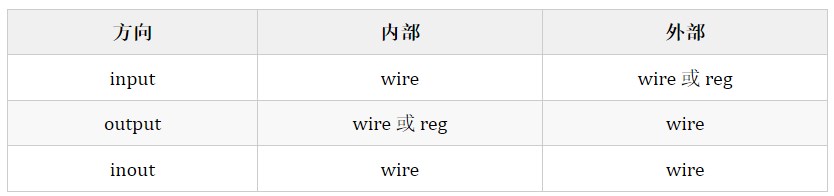

根據端口的方向,端口類型有3種:輸入(input)、輸出(output)和雙向端口(inout)

- input 和 output 只能是

wire型 - output 既可以是

wire也可以是reg- 需要保存數值時,用

reg - 不需要保存數值時,用

wire

- 需要保存數值時,用

reg類型是用于保存數值的,而輸入端只能反映與其相連的外部信號的變化,并不能保存這些信號的值

端口連接規則

對于inpu和output我是這樣理解的,內部是reg外部就應該是wire

就比如input這一端,外部是reg,內部是wire,在這個一端,已經有一個reg類型可以用來保存數據,不需要用到兩個reg來保存數值

端口連接方式

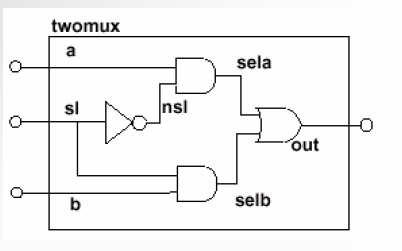

端口連接的方式有兩種:按位置連接 和 按名稱連接

- 按位置連接

調用模塊的端口名必須與被調用模塊端口列表中的位置保持一致//調用模塊 module name(……); //端口定義 //端口描述 /*a, b, c, d分別對用調用模塊 中的in1, in2, sel, dout*/ mux u1(a, b, c, d); endmodule //調用模塊 module mux (in1, in2, sel, dout); //端口定義 //端口描述 //邏輯描述 endmodule - 按名稱連接

格式為:模塊名 模塊實例化名 (.被調用模塊端口名(調用模塊端口名));

其中,模塊實例化名是自己隨意定的一個名字,方便記憶就好//調用模塊 module name(……); //端口定義 //端口描述 //模塊調用,也叫實例化 //對應方式和上一個相同 mux u1(.in1(a), .in2(b), .sel(c), .dout(d)); endmodule //被調用模塊 module mux(in1, in2, sel, dout); //端口定義 //端口描述 //邏輯描述 endmodule

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog設計

+關注

關注

0文章

20瀏覽量

6640 -

verilog接口

+關注

關注

0文章

2瀏覽量

4543

發布評論請先 登錄

相關推薦

熱點推薦

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

在實例化模塊時,使用Verilog時有兩種常用的方式來進行模塊端口的信號連接:按端口順序以及按端口名稱連

SDI_OUT端口與屏幕連接后顯示噪音該怎么辦?

mvisdi_viodc_2VP7.bit從'viodc_sdi_verilog \ Bit Files'目錄復制到fpga芯片。但它不起作用。板的SDI-IN端口與視頻信號連接,SDI_OUT

發表于 08-14 07:15

Verilog 模塊與端口

:輸入、輸出端口可以采用向量的方式表示,例如:4輸入端a0,a1,a2,a3,與4輸入端b0,b1,b2,b3, 一一對應相與,其結果賦給對應的c0,c1,c2,3;Verilog 的描述如下

發表于 07-23 23:08

Verilog代碼命名六大黃金規則

電子發燒友網核心提示: 關于Verilog代碼中命名的六大黃金規則。 1. 系統級信號的命名。 系統級信號指復位信號,置位信號,時鐘信號等需要輸送到各個模塊的全局信號;系統信號以字

發表于 09-04 14:40

?6430次閱讀

Verilog HDL的基礎知識詳細說明

硬件描述語言基本語法和實踐

(1)VHDL 和Verilog HDL的各自特點和應用范圍

(2)Verilog HDL基本結構語言要素與語法規則

(3) Verilog HDL組

發表于 07-03 17:36

?54次下載

Verilog系統函數和邊沿檢測

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括Verilog仿真時常用的系統任務、雙向端口的使用(inout)、邊沿檢測”

System Verilog的概念以及與Verilog的對比

Verilog模塊之間的連接是通過模塊端口進行的。 為了給組成設計的各個模塊定義端口,我們必須對期望的硬件設計有一個詳細的認識。 不幸的是,在設計的早期,我們很難把握設計的細節。 而且

verilog雙向端口的使用

在Verilog硬件描述語言中,端口是指連接模塊(Module)與其他模塊、寄存器或是物理設備的輸入或輸出接口。單向端口可以作為輸入或輸出使用,而雙向

verilog調用模塊端口對應方式

Verilog是一種硬件描述語言(HDL),廣泛應用于數字電路設計和硬件驗證。在Verilog中,模塊是構建電路的基本單元,而模塊端口對應方式則用于描述模塊之間信號傳遞的方式。本文將介紹

verilog中端口類型有哪三種

在 Verilog 中,端口類型有三種:輸入端口(input)、輸出端口(output)和雙向端口(inout)。 輸入

Verilog表達式的位寬確定規則

很多時候,Verilog中表達式的位寬都是被隱式確定的,即使你自己設計了位寬,它也是根據規則先確定位寬后,再擴展到你的設計位寬,這常常會導致結果產生意想不到的錯誤。

Verilog端口連接規則

Verilog端口連接規則

評論