作者:Narasimha Babu G V L、Udit Kumar 和 Anand Shirahatti

我們中許多主要從事數字驗證和設計工作的人都不受物理層細節的影響。只有少數專家密切關注這些細節。因此,對于我們其他人來說,驗證和調試擴頻時鐘(SSC)可能是一項艱巨的任務。

這篇博文是一個快速的問答,讓您快速開始了解PCI Express(PCIe)擴頻時鐘(SSC)技術的一些復雜性。

在這里,您可以了解有關適用于第 4 代就緒 PCIe 和 PCIe 測試套件的 Synopsys VC 驗證 IP 的更多信息。

什么是擴頻時鐘?為什么使用它?

擴頻時鐘是以受控方式對系統時鐘進行抖動以降低峰值能量含量的過程。SSC技術用于最小化電磁干擾(EMI)和/或通過聯邦通信委員會(FCC)的要求。

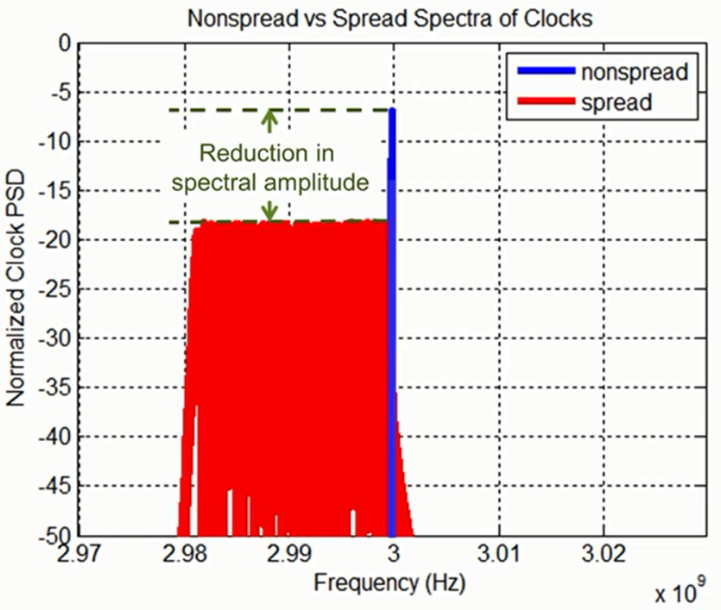

如果將時鐘信號轉換為頻域,則會在時鐘頻率處發現高能量尖峰(下圖3中1GHz處的非擴展藍色尖峰)。擴頻是一種將此尖峰分布在頻帶上以降低信號頻率處的功率的方法(圖1中的紅色擴展)。

圖 1:采用擴頻時鐘的 3GHz 時鐘的頻譜幅度降低

擴頻時鐘是如何實現的?

擴頻時鐘使用調制來實現頻譜功率的擴展。載波信號通常是高頻時鐘信號,與低頻調制器信號進行調制。雖然整體能量不變,但峰值功率降低。峰值能量色散量取決于調制帶寬、擴頻深度和擴頻曲線。

由此產生的SSC調制載波信號最終的抖動比未調制載波信號高得多。

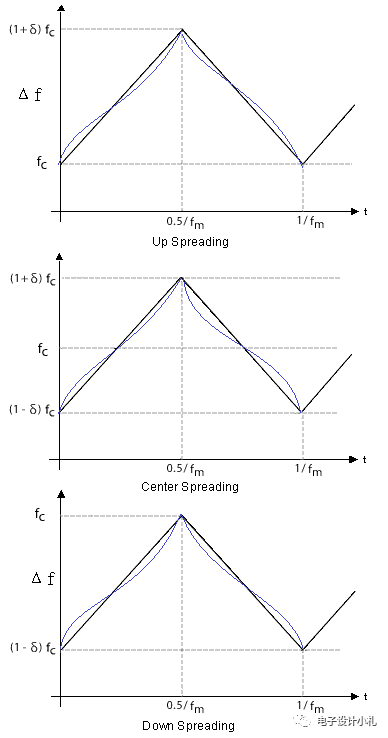

最常見的調制技術是下擴頻和中心擴頻:

下擴頻:載波按指定的百分比調制至低于標稱頻率,而不是更高

中心擴展:載波按指定百分比調制高于和低于標稱頻率

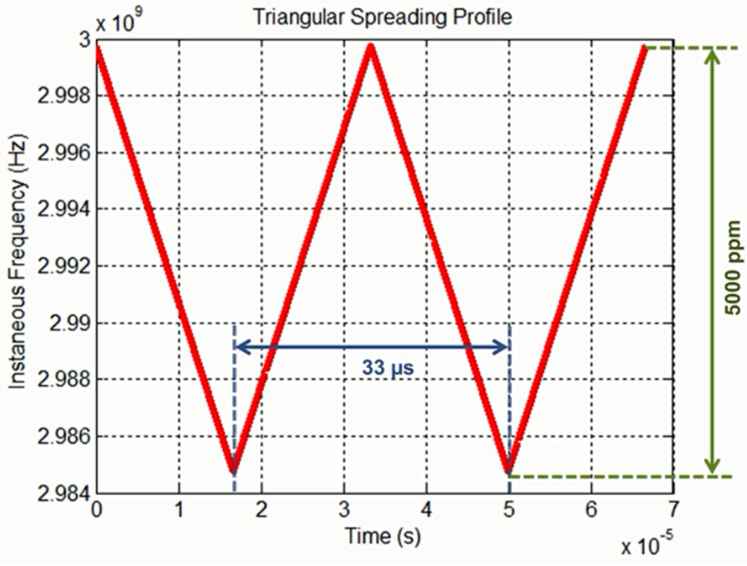

下面的圖2顯示了一個3Ghz載波時鐘信號,使用0KHz三角波時下行擴展5.30%。在Y軸上,您可以看到載波頻率的上升和下降。所有擴頻載波頻率值仍低于 3 GHz。

圖 2:3GHZ 載波信號頻率變化,下行擴展 SSC 時鐘為 0.5%

PCIe 支持哪些不同的時鐘架構?它們都支持 SSC 嗎?

PCIe 支持三種不同類型的時鐘架構:

公共參考時鐘(公共參考時鐘)

數據時鐘

單獨的參考時鐘(單獨的參考時鐘)

通用 Refclk 是商用設備中支持最廣泛的架構。但是,必須將相同的時鐘源分配給每個 PCIe 設備,同時將設備之間的時鐘到時鐘偏斜保持在 12 ns 以下。這可能是大型電路板的問題,或者將背板連接器交叉到另一個電路板時。

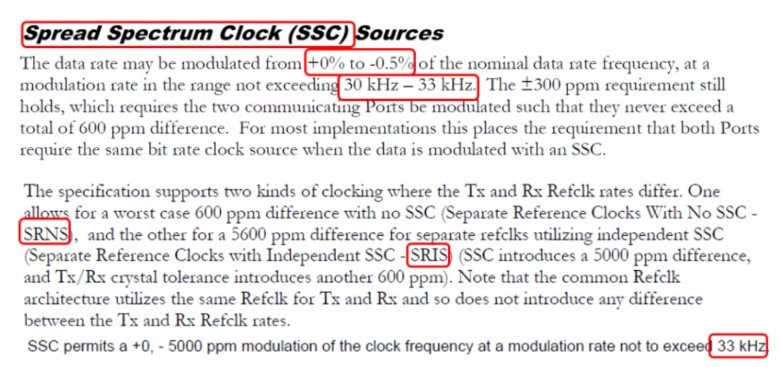

如果低偏斜配置不可行,例如在長電纜實現中,則可以使用兩端具有獨立時鐘的獨立 Refclk 架構。但是 Gen 2.0 基本規范不允許在單獨的 Refclk 實現上使用 SSC。它僅在 2013 年通過 ECN:獨立的 Refclk 獨立 SSC (SRIS) 架構啟用,該架構成為 3 年 1 月發布的 2013.<> 基本規范的一部分。

數據時鐘 Refclk 架構是最簡單的,因為它只需要一個時鐘源,位于發射器上。接收器提取并同步到嵌入在傳輸數據中的時鐘。數據時鐘架構是在 2 年發布 PCIe 0.2007 標準時引入的。

您可以在此處了解有關時鐘架構的更多信息。

要了解有關SRIS的更多信息,以下是Synopsys研究員John Stonick的另一個富有洞察力的短視頻。

SSC 是否在所有速度下都受支持?

是的。所有四種速度 2.5 GT/s(第 1 代)、5 GT/s(第 2 代)、8 GT/s(第 3 代)和 16 GT/s(第 4 代)均可支持 SSC。相同的擴頻時鐘參數適用于所有四種速度。

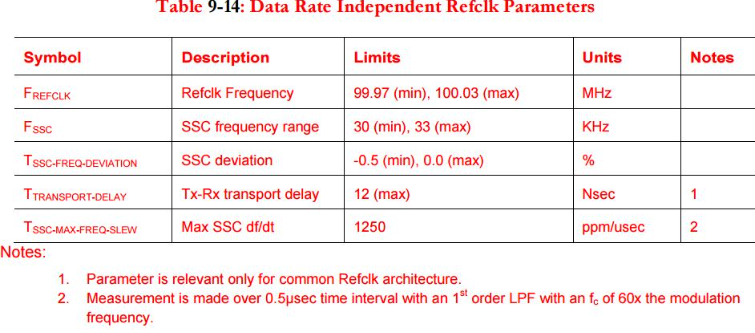

圖 3:第 4 代 PCIe 基本規范中的 Refclk 參數快照(來源:PCI-SIG)

上表中我們需要注意的一些關鍵參數:

FREFCLK:參考頻率可以有 +/-300 PPM 的變化。對于單獨時鐘架構,接收器必須容忍600 PPM的最壞情況抖動。

FSSC:這是調制波的頻率。這通常是三角形的。

TSS-FREQ-DEVIATION: 這表示 PCIe 使用向下傳播的 SSC。應用此點差可將攜帶頻率降低 -0.5%。這意味著額外的 5000 PPM 抖動。因此,啟用擴頻的獨立時鐘的總抖動將為5600 PPM。

擴頻時鐘的驗證提供的價值是多少?

從被測設計(DUT)的角度來看,主要價值在于驗證接收器的時鐘數據恢復建模,以處理抖動的巨大變化(高達5600 ppm),尤其是在SRIS模式下。

如何目視驗證 SSC 是否真的發生?

有多種方法。最簡單的方法是,您可以將“時鐘周期信號”可視化,通常是浮點數據類型(SystemVerilog 中的實際類型),如果它可以在波形查看器中作為模擬信號訪問。

如果無法訪問,則通過簡單的監視器收集以線速運行的Refclk或內部生成的傳輸位時鐘的時間戳和周期,假設您使用33Khz調制,則至少為30us。在 X 軸上繪制時間戳,在 Y 軸上繪制時鐘的持續時間。您應該能夠看到與圖 2 中所示的配置文件匹配的配置文件。

為了成功驗證擴頻時鐘,您使用的 PCIe 驗證 IP 需要支持 SSC。它應該為您提供以不同速度打開或關閉擴頻的可編程性。此外,它還應支持規范定義的SSC配置文件,用于0.5%的下行傳播。它還應該允許在30Khz(最小)和33Khz(最大)范圍內的調制信號頻率方面進行編程。Synopsys PCIe VIP 加載了所有這些功能以及更多功能。

審核編輯:郭婷

-

emi

+關注

關注

53文章

3661瀏覽量

129662 -

擴頻時鐘

+關注

關注

0文章

9瀏覽量

10673 -

ssc

+關注

關注

0文章

25瀏覽量

11397

發布評論請先 登錄

相關推薦

擴頻時鐘技術分享:SSC技術是什么、SSC對測試高速總線信號的影響

面向驗證工程師的PCIe擴頻時鐘(SSC)

面向驗證工程師的PCIe擴頻時鐘(SSC)

評論