一實驗目的

熟悉 HME FPGA PLL IP 的使用,實現 LED 流水燈功能

二實驗環境

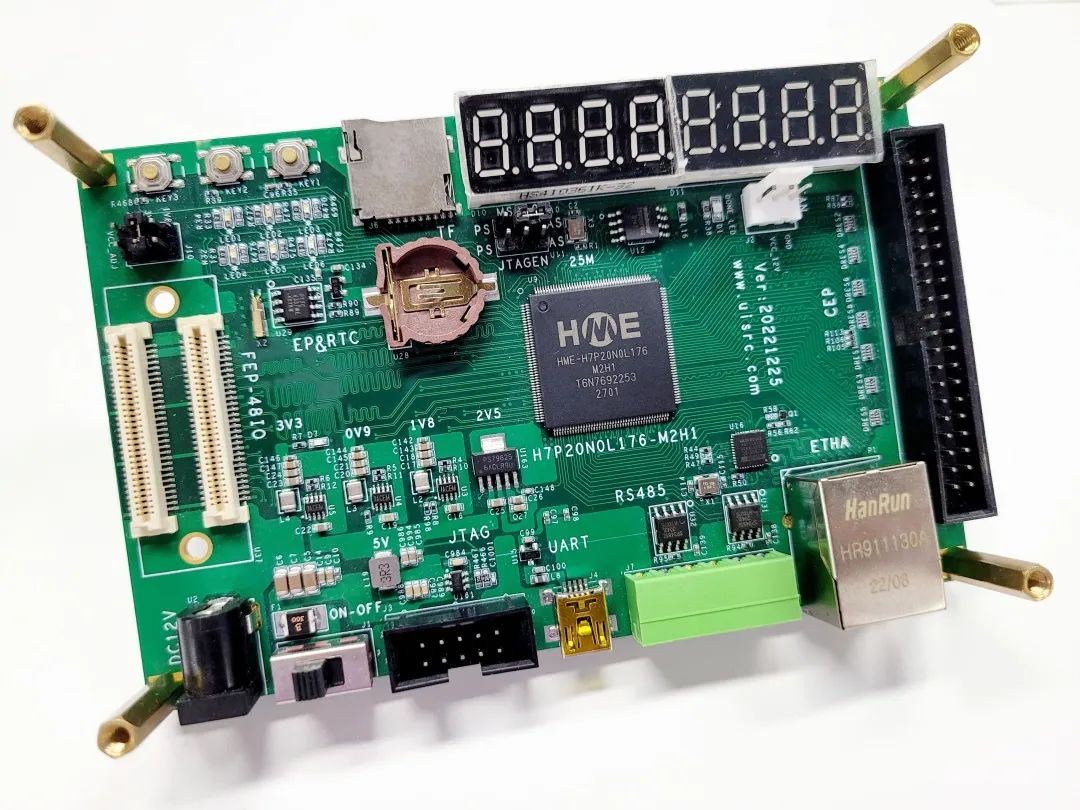

IDE:福晞Fuxi、開發板:P0 176

HME_P0 176 開發板

三實驗原理

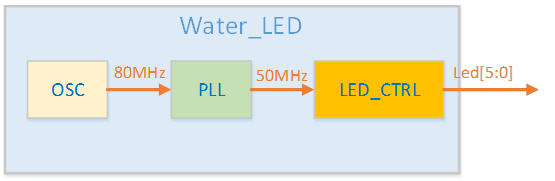

3.1 實現框架

3.2 實驗功能分析

使用 P0 內部 OSC 作為時鐘源,通過 PLL 鎖相環輸出 50MHz 的時鐘作為 LED 的控制時鐘,依次點亮板載的 6 個 LED 燈,實現流水燈的效果。

每個 LED 燈一次點亮持續時間 0.5s,通過分時控制每個連接到 LED 燈的 I/O 電平的高低來實現。如 LED 的控制時鐘是 50MHz(T=20ns),需要通過一個計數器來計數,當計數器的值是25000000時改變 LED 亮滅狀態。

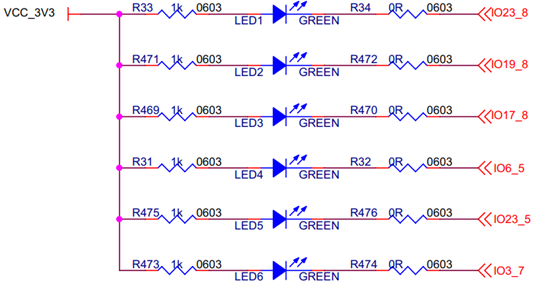

LED 部分原理圖如下:

四OSC 與 PLL 使用

4.1 P0 OSC 使用

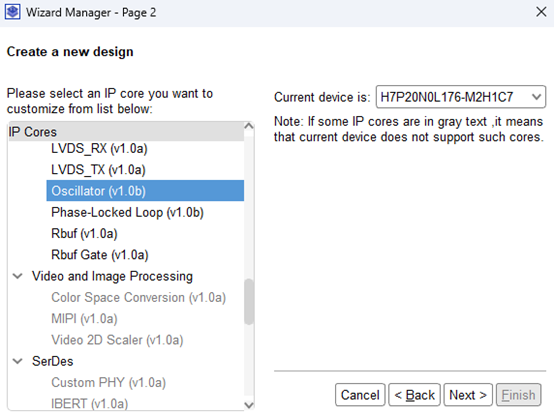

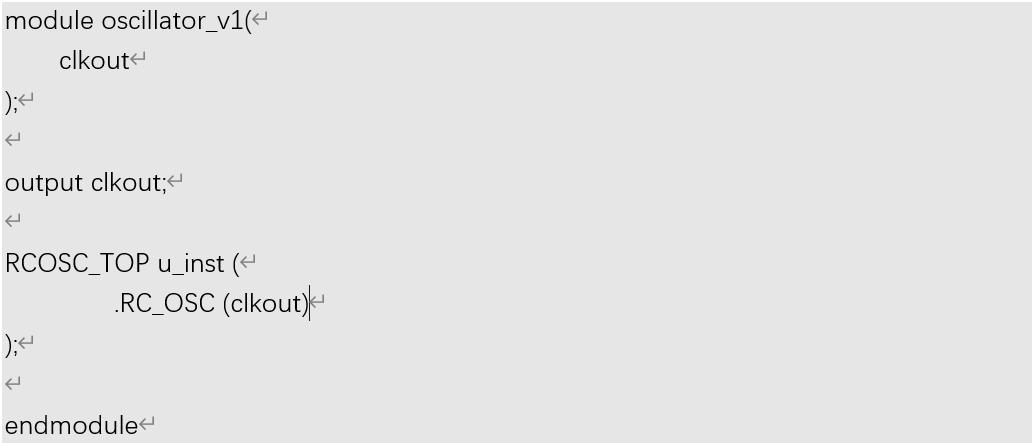

P0 內部有精準的 RC-OSC 時鐘發生器,輸出 80MHz 可作為系統的時鐘源。rtl 代碼可通過 Fuxi IP Wizard 將其例化出來使用,如下圖:

創建出IP的代碼如下:

4.2 P0 PLL 鎖相環簡介

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-locked Loop)。利用外部輸入的參考時鐘信號控制環路內部振蕩信號的頻率和相位。

HME 系列產品的 PLL 模塊能夠提供可以綜合的時鐘頻率,通過配置不同的參數可以進行時鐘的頻率調整(倍頻和分頻)、相位調整、占空比調整等功能。

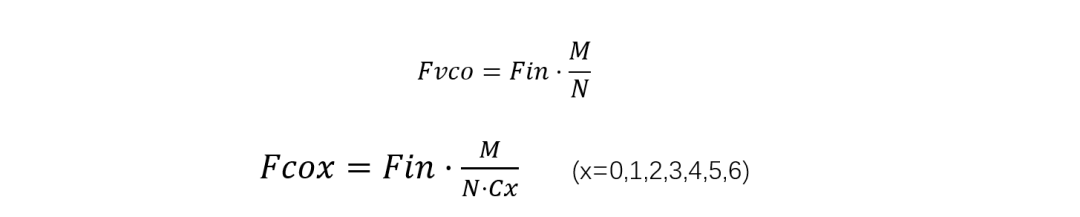

PLL 可對輸入時鐘 CLKIN 進行頻率調整(倍頻和分頻),計算公式如下:

FIN=輸入時鐘,可以是外部時鐘,也可是芯片內部的 osc 時鐘;后面會講述內部 osc 的使用方法。

N=CFG_DIVN [6:0]+1

M=CFG_DIVM [6:0]+1

Cx=CFG_DIVCX[6:0]+1

N、M、Cx 為 PLL 的參數,IP 會自行推到計算。

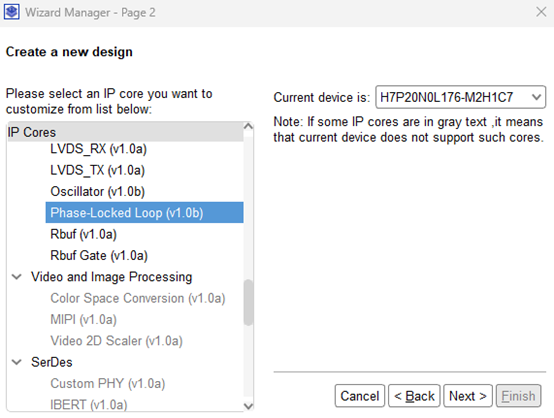

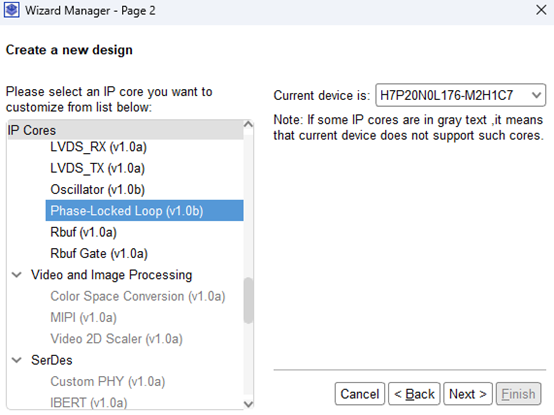

4.3 PLL IP 使用

通過 IP Wizard 創建 PLL

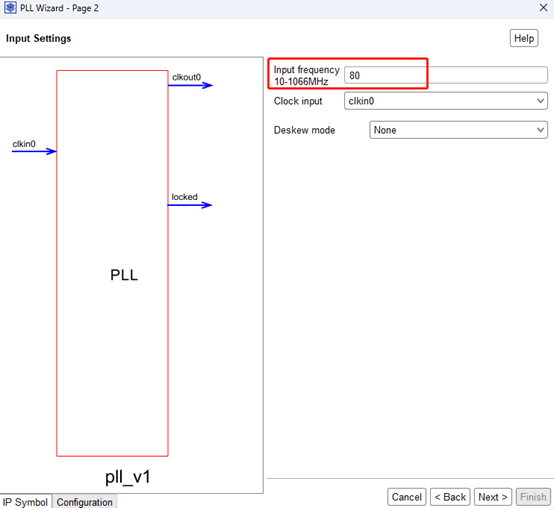

Input Frequency 是 PLL 的輸入頻率,這里配置為 80MHz,是因為這里將 oscillator_v1 IP 實例的 clkout 80MHz 作為 PLL 的輸入時鐘。

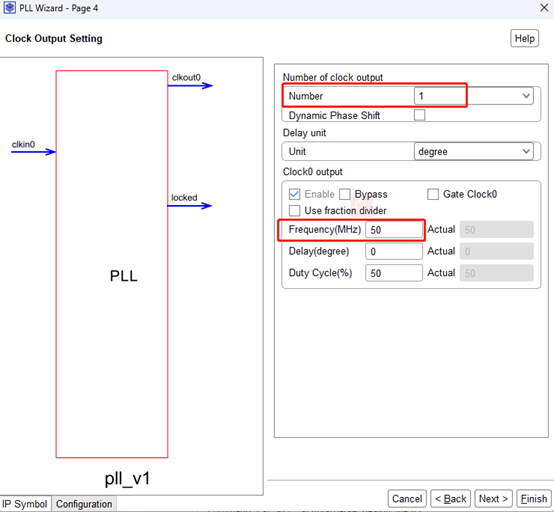

如下圖所示,選擇了1個時鐘輸出通道,輸出頻率 clkout0 為 50MHz,將該時鐘作為邏輯的系統時鐘;locked 信號一開始為低電平,當各輸出通道的時鐘穩定后變為高電平;可利用該特性將 locked 信號作為系統的復位信號。

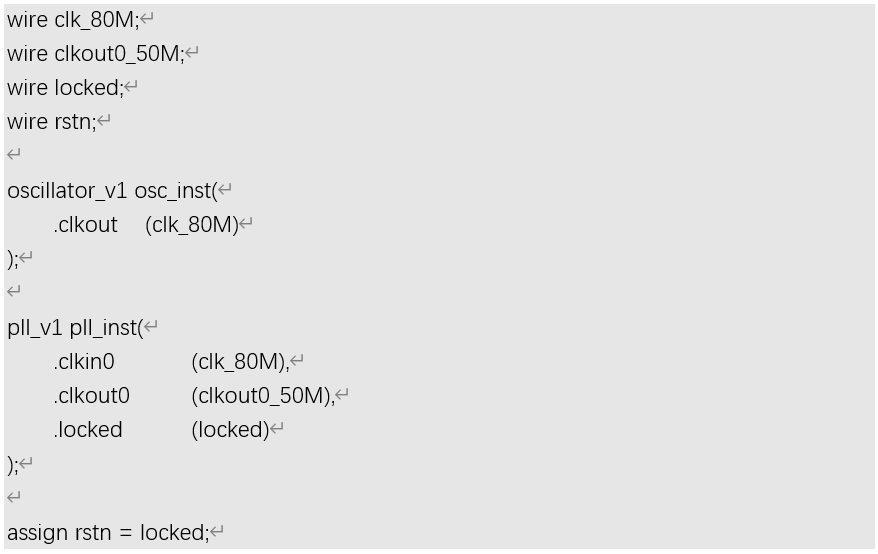

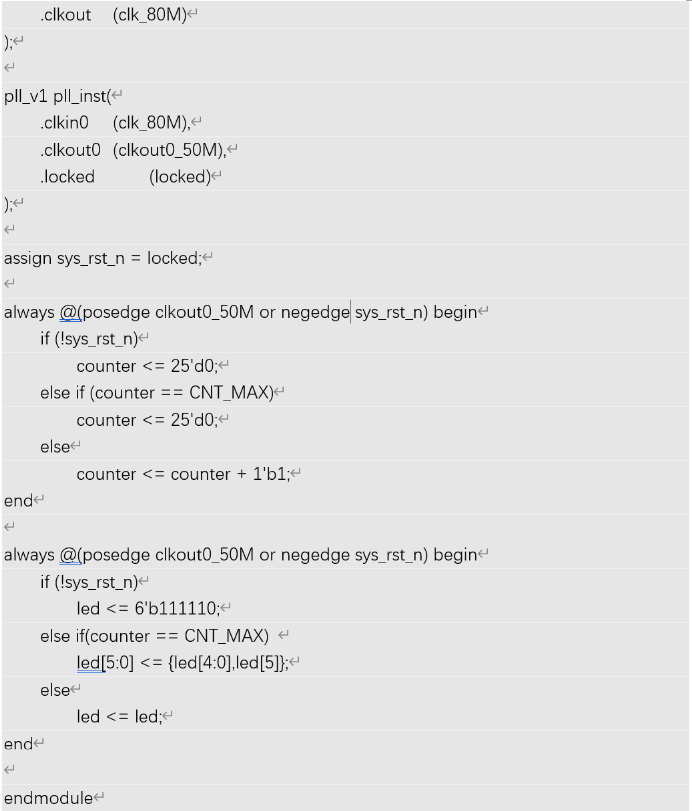

實例化 PLL 的 rtl 代碼如下:

五RTL 功能實現

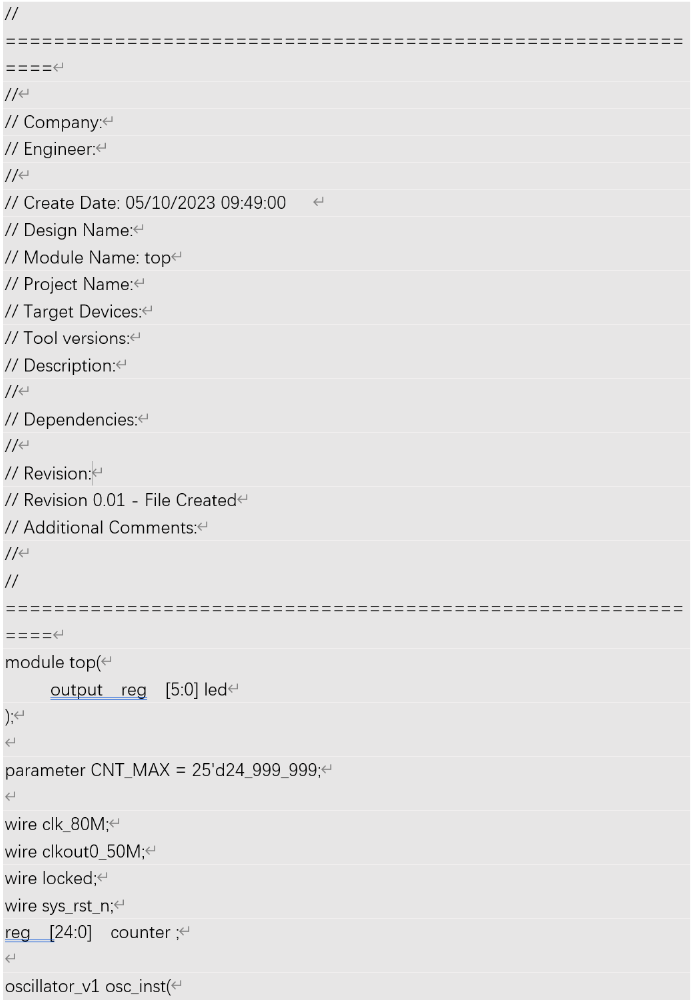

時鐘源使用 P0 內部 osc 時鐘 80MHz,osc 時鐘作為 PLL 的輸入,PLL clkout0 輸出50MHz 時鐘作為邏輯設計的系統時鐘。通過計數器控制每個 LED 點亮持續 0.5s 并形成流水效果。

5.1 RTL Design

5.2 實驗現象

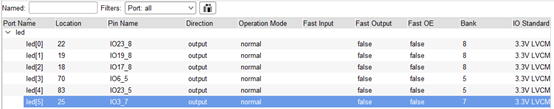

5.2.1 I/O 約束

綜合編譯檢查是否存在語法問題;通過后進行I/O約束;

如下圖:

5.2.2 生成碼流與下載

然后執行 Generate Bitstream 生成碼流文件,下載至 P0 開發板進行驗證。

6 個 LED 燈按照設定的順序和時間依次點亮和熄滅,說明 PLL 輸出時鐘和邏輯設計符合預期。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615350 -

led

+關注

關注

242文章

23770瀏覽量

671787 -

流水燈

+關注

關注

21文章

433瀏覽量

60366 -

開發板

+關注

關注

25文章

5589瀏覽量

103126 -

HME

+關注

關注

0文章

3瀏覽量

7370

原文標題:HME FPGA 入門指導:HME-P(飛馬)系列開發板實驗教程——LED 流水燈

文章出處:【微信號:HME-FPGA,微信公眾號:HME京微齊力】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

國產FPGA簡介

【Runber FPGA開發板】配套視頻教程——LED流水燈實驗

【Runber FPGA開發板】配套視頻教程——鍵控流水燈實驗

51單片機流水燈實驗報告.doc

紫光同創FPGA入門指導:鍵控流水燈——紫光盤古系列50K開發板實驗教程(2)

實驗教程:LED 流水燈 ——紫光盤古系列高性能入門級2K開發板

【紫光同創國產FPGA教程】【PGC1/2KG第二章】LED 流水燈實驗例程

京微齊力HME-P1P60 FPGA榮獲年度最佳處理器/FPGA獎項

CVI實驗指導(八)Lab WindowsCVI制作流水燈

HME FPGA入門指導:HME-P(飛馬)系列開發板實驗教程——LED流水燈

HME FPGA入門指導:HME-P(飛馬)系列開發板實驗教程——LED流水燈

評論