高速先生成員--姜杰

關于DDR的案例,高速先生已經分享過很多期的文章了,有通過修改主控芯片的驅動解決問題的,有通過修改PCB走線的拓撲來解決問題的,也有通過調節端接電阻來解決問題的,相對于下面即將登場的解決方法而言,上述的方式都突然顯得很復雜了。不信?那我們一起往下看唄!

又是一個睡眼朦朧的下午,雷豹最近剛結束掉手上的所有項目,在公司美美的睡上一個午覺醒來后,正值百無聊賴之際,師傅Chris為了防止雷豹繼續“頹廢”,剛好手上接到了一個DDR的debug項目,因此毅然決然的分配給了雷豹,這突如其來的“鍋”讓雷豹瞬間驚醒。

這個DDR有問題的板子是我們設計的,但是并沒有進入到仿真部門去做仿真,客戶的描述也非常的直擊問題點,就是。。。DDR4跑不到額定的2400M的速率!

只想板子跑到額定2400M的速率,客戶這個要求一點也不過分,但是我們的設計工程師看了看之前的板子,也找不到太多的優化方案。因為本來就只有1拖2的2個DDR顆粒的拓撲,正常來說都比較好做,工程師在走線上也參考了之前內部培訓的設計方法,照道理不應該出問題啊!

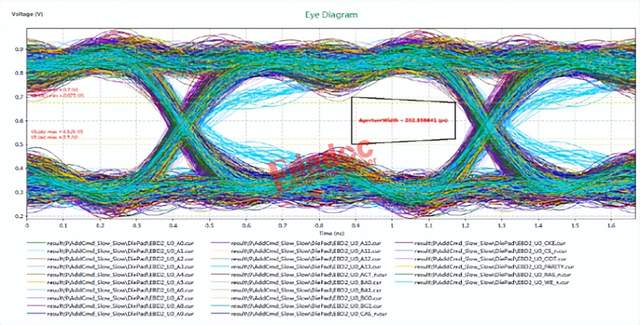

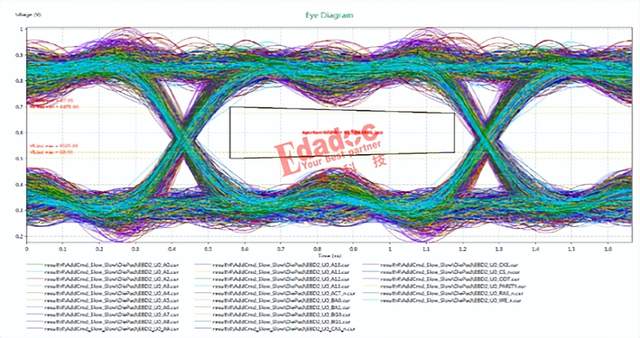

雷豹是個直直的仿真愛好者,這時候他也先不管怎么去優化,也沒去找原因,就先拿到主控和顆粒的模型先按照這個版本做了個通道的仿真,不得不說雷豹的仿真技術是真的牛叉,很快就仿真出了也是fail的,能夠和測試情況相對應。

他很自豪的和師傅Chris匯報,只見Chris淡淡的一笑,反問到雷豹,那是哪里出了問題呢,又應該這么去從PCB設計上去優化呢?雷豹雖然在和Chris匯報仿真結果之前其實也有想過師傅會這樣問,奈何雷豹也打開PCB文件去看了,重點關注了走線的拓撲結構,對比和我司設計部之前做過的類似設計的方案,兩者在走線上是長度,拓撲結構上都是非常接近的。一句話,也就是找不到問題點唄。。。

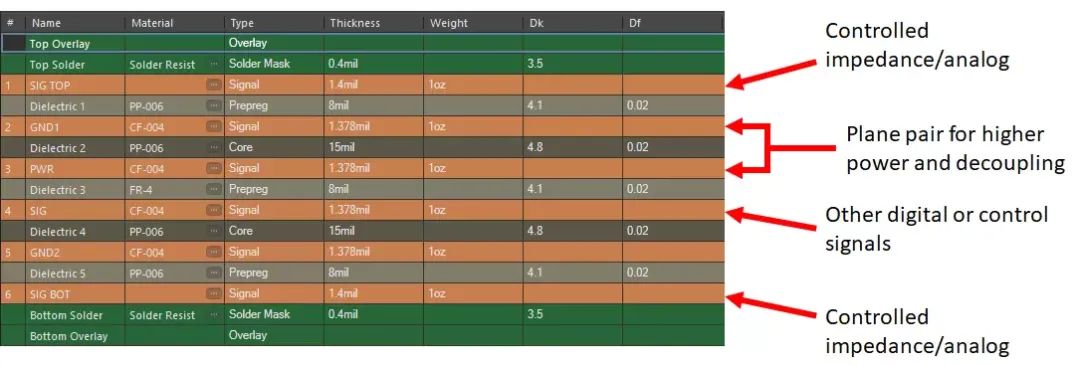

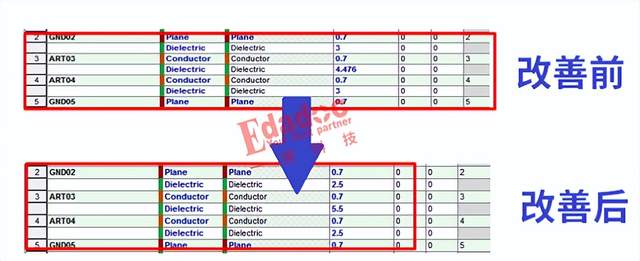

Chris看雷豹好像沒轍了,那就只能給雷豹一點暗示了。只見Chris不慌不忙的打開PCB文件,雷豹見Chris直接跳過了檢查PCB上的走線這一步,徑直的打開了疊層設置,然后給雷豹指一下這個地方,沒錯,指的就是下面這個紅框框的地方。

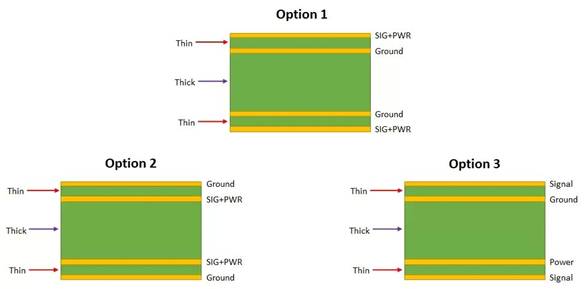

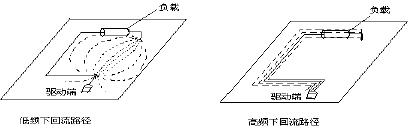

雷豹感覺好像懂了一點了,原來該客戶為了比demo板有更好的成本優勢,在設計上使用了相鄰層走線的這個方法,也就是我們所說的GSSG的疊層結構,這樣的話的確在層數上可以省下幾層,但是就會帶來其他方面的一些壞處。雷豹一直都是在關注走線是怎么怎么走的,和demo板是如何如何相似,卻沒注意到疊層設計本身已經有這么大的差別了。

這時既然客戶要省成本嘛,高速先生肯定還是尊重客戶的這個意愿的,就在客戶這個省成本的設計中去想辦法改善信號質量,從而達到要求。鑒于雷豹已經隱約知道了問題的原因了,Chris也不立馬點破,還是希望讓雷豹自己能獨立解決。之前已經說了,要保持這個省成本的層數不變,在這個前提的下去解決問題。

雷豹左想右想了半天,突然靈機一動,只見他對了疊層設置一頓調節,又相應的通過改變線寬來保證原有的走線阻抗不變。之前是12層板,現在也還是12層板,總體的板厚也沒發生變化。然后雷豹帶著他自己優化后的仿真結果再和Chris匯報,這次雷豹帶來的仿真結果果然有了明顯的優化,從仿真驗證上,已經能把信號質量變成PASS了!

Chris看看雷豹優化后的PCB文件,發現走線的拓撲長度都沒有變化,只是從疊層上做了下文章,這也和Chris預想的方案是一樣的,然后就給雷豹點了一個大大的贊,雷豹尋思這一路debug過來,雖然最后想到的方案不難,但是發現和解決debug問題的過程卻是艱辛的,不過總算自己解決掉了,也積累了一個新的技術點!

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52308瀏覽量

437888 -

DDR

+關注

關注

11文章

731瀏覽量

66522 -

疊層

+關注

關注

0文章

29瀏覽量

10078 -

PCB

+關注

關注

1文章

2082瀏覽量

13204

發布評論請先 登錄

6層PCB疊層設計指南

DDR跑不到速率,調整下PCB疊層就搞掂了?

DDR跑不到速率后續來了,相鄰層串擾深度分析!

為什么要進行PCB疊層

DDR跑不到速率后續來了,相鄰層串擾深度分析!

DDR電路的疊層與阻抗設計

如何正確的對PCB疊層進行構建

DDR跑不到速率,調整下PCB疊層就搞掂了?

DDR跑不到速率,調整下PCB疊層就搞掂了?

評論