無源器件在電路中一直扮演著很重要的角色,同樣在ESD設(shè)計中也需要應(yīng)用無源器件,亦或是無源器件也同樣要承受ESD沖擊。所以這一期針對無源器件:電阻在ESD設(shè)計中的應(yīng)用與面對ESD的失效機理做一個討論。

1.1N-diffusion resistor的ESD應(yīng)用。

N-diffusion resistor在ESD防護電路中主要有如下應(yīng)用:

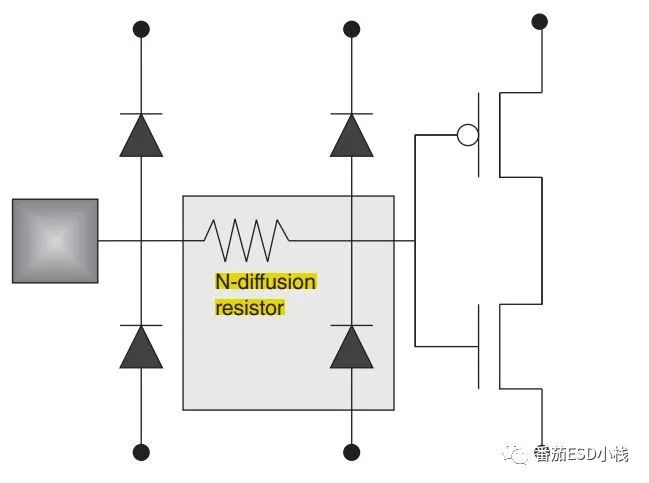

圖一.在HBM-CDM二級防護中的N-diffusion電阻。

在該結(jié)構(gòu)是最為常見的針對IO接口的ESD防護電路,該電路中靠近PAD端的二極其設(shè)計目的是針對HBM進行防護,所以尺寸很大,導(dǎo)通電阻較小。而后一級的二極管只需要針對CDM進行防護,所以尺寸較小。而兩級二極管之中的N-diffusion電阻的 作用一便是作為串聯(lián)電阻,確保HBM的ESD電流不會流入第二級中。 因為第二級的尺寸較小,過電流能力弱,所以需要N-diffusion電阻讓第二級在HBM中只分流較小的電流。(CDM和HBM的區(qū)別前面的文章已經(jīng)提到過,針對這種超高頻的靜電流,只需要寄生電容很小的二極管便能實現(xiàn)泄放)

作用二是N-diffusion與P-sub構(gòu)成了一個寄生二極管。 當(dāng)P-sub中集聚了大量電子且PAD接觸到導(dǎo)體后,P-sub中的電子利用該寄生二極管泄放CDM電流,從而實現(xiàn)對NMOS的CDM保護作用,避免Gate損壞。(目前這種設(shè)計比較少見)

圖二. N-diffusion電阻作為NMOS鎮(zhèn)流電阻。

圖三. N-diffusion電阻作為NMOS鎮(zhèn)流電阻。

無論是GGNMOS還是GCNMOS都需要NMOS的drain端直接承受ESD的沖擊,所以為了避免MOS管的損壞,需要在drain端設(shè)計鎮(zhèn)流電阻, 一方面能確保ESD電流的均勻分布,一方面能保護器件不在ESD中損壞 。除了用N-well resistor 作為NMOS鎮(zhèn)流電阻外,還可以將drain端拉寬,并進行salicide block處理。

1.2 N-WeLL resisitor的ESD作用。

N-Well電阻在ESD防護電路中主要起到的是鎮(zhèn)流電阻的作用。

圖四.N-well resistor 作為NMOS鎮(zhèn)流電阻。

這種設(shè)計的目的與N-diffusion電阻作為NMOS鎮(zhèn)流電阻的設(shè)計思路一致。但是N-Well鎮(zhèn)流有其獨特的優(yōu)勢:

1.因為N-Well的存在,ESD電流需要流過Nwell才能到達drain端,其鎮(zhèn)流效果更好,NMOS的drain端承受的靜電作用較少。

2.N-Well中載流子濃度較低,所以這種鎮(zhèn)流結(jié)構(gòu)中N-well與MOS中N+接觸面會存在異質(zhì)結(jié),該異質(zhì)結(jié)有利于GGNMOS中寄生三極管的擊穿。

3.不需要silicide block的mask。

4.與NMOS的集成度更高,能降低接觸電容。

圖五.N-well resistor 作為NMOS鎮(zhèn)流電阻。

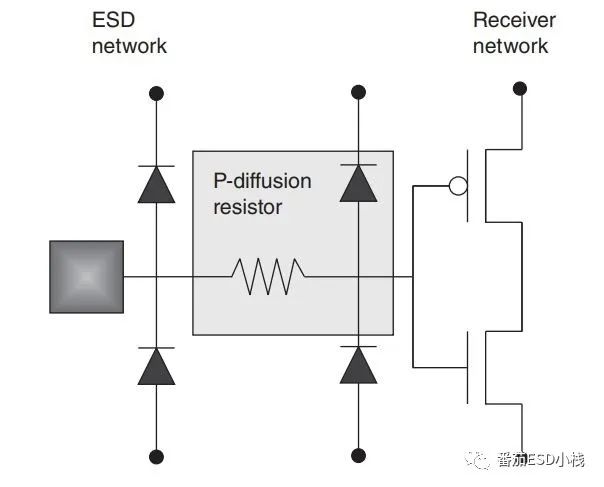

2. P-diffusion resisitor的ESD應(yīng)用

P-diffusion resisitor的應(yīng)用與N-diffusion resistor的應(yīng)用類似,主要作用于HBM-CDM二級防護中,一二級間的分流電阻, 避免二級保護被HBM所損壞 。同時P-diffusion resisitor中的 P+與PMOS中的N-Well形成一個寄生二極管,實現(xiàn)對N-WeLL中積聚的負(fù)電荷的泄放,實現(xiàn)對PMOS的CDM防護。 另外P-diffusion resisitor也可以實現(xiàn)對GDPMOS中PMOS源端的保護。

圖六.在HBM-CDM二級防護中的P-diffusion電阻。

3. POLY 電阻的ESD應(yīng)用

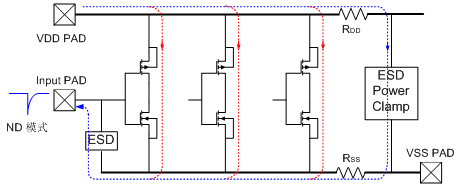

1.1與2.1已經(jīng)提到了diffusion電阻用于CDM防護,但是這兩種電阻有個明顯弊端,N-diffusion只能保護NMOS,P-diffusion只能保護PMOS,但是PMOS和NMOS都有CDM損壞風(fēng)險,diffusion電阻無法做到兩者兼顧。目前最主流的HBM-CDM二級防護的結(jié)構(gòu)如圖所示:

圖七.POLY電阻的ESD應(yīng)用。

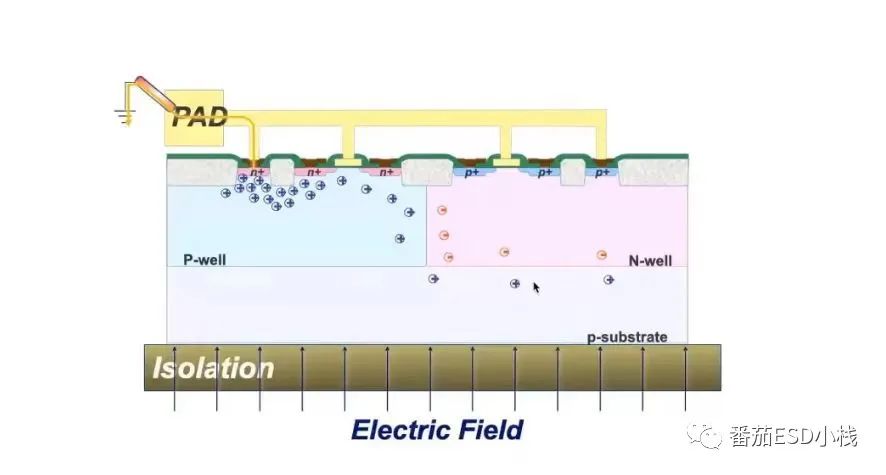

用POLY電阻作為二級防護的電阻,讓其只起到分流的作用。 把P-diode與PMOS做到同一個阱中,當(dāng)PMOS中的N-WeLL中因為外界電場積聚了很多負(fù)電荷后,負(fù)電荷可以通過P-diode與N-Well間的寄生二極管泄放到PAD,實現(xiàn)對PMOS的CDM防護。同理把N-diode與NMOS做到同一個阱中,當(dāng)在外界作用下NMOS中的P-Well積聚了大量正電荷,這些正電荷便可通過N-diode泄放,實現(xiàn)對NMOS的CDM防護。

圖八.N-diode實現(xiàn)NMOS的CDM防護機理示意圖。

POLY電阻用于二級防護,需要根據(jù)前后級的類型選擇阻值,如果前后級都是二極管,其阻值不需很大。如果前后級是GGNMOS等需要擊穿的器件,阻值就需要大一些。

有些設(shè)計會在ESD防護單元后加電阻,如圖所示。

圖九.ESD后置POLY電阻。

該電阻的作用是保護Input buffer的柵極。 ESD器件的Second break down Voltage 的電壓會分壓一部分到電阻上,從而保護了內(nèi)部電路的柵極。

POLY電阻還應(yīng)用于體鎮(zhèn)流電阻,用來提高器件的ESD魯棒性。

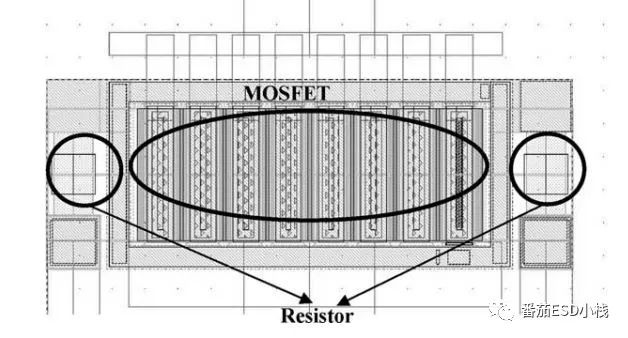

圖十.體鎮(zhèn)流電阻版圖。

體鎮(zhèn)流電阻的作用是通過鎮(zhèn)流電阻,促使體電位分布均勻,使得GGNMOS等器件在應(yīng)對ESD電流時均勻開啟,提高ESD過電流能力。 同時,該電阻能減少GGNMOS進入Holding Voltage后的開啟電阻。

圖十一.體鎮(zhèn)流電阻示意圖。

4.電阻的ESD失效分析

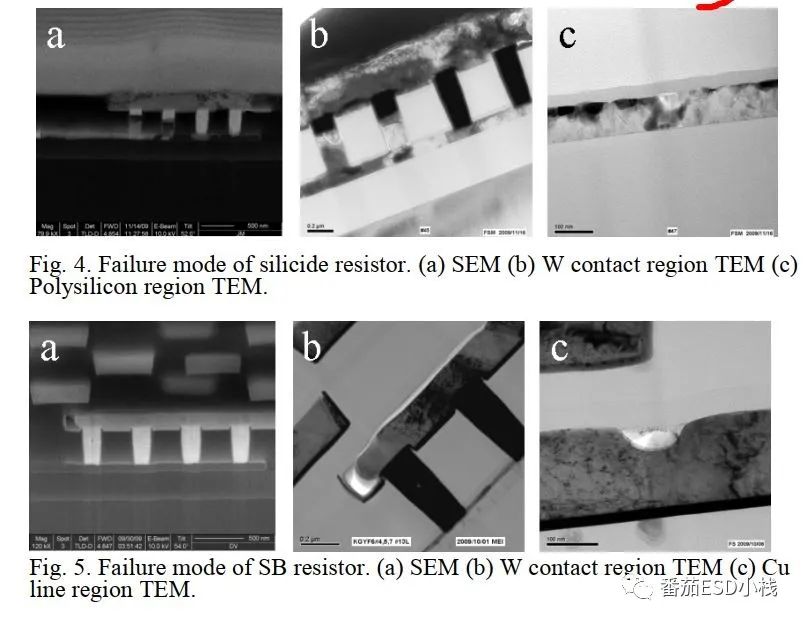

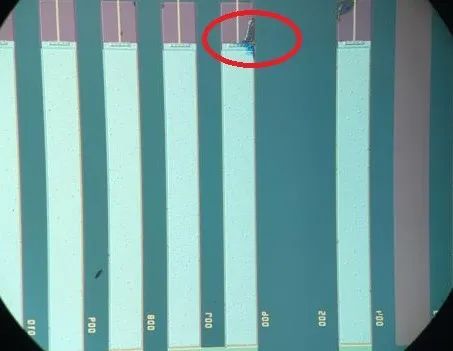

在電路中無論是ESD防護單元還是其他單元,都有承受ESD沖擊的風(fēng)險。這里討論下電阻在ESD下的失效機理。 電阻在面對ESD時的失效原因是由不同材料接觸面的熱失配梯度造成 (不同材料的接觸面產(chǎn)生熱力學(xué)梯度,時間一久或者梯度過大,就會造成失效)。目前主流工藝結(jié)點下,接觸孔主要是由鎢做成,互聯(lián)主要由Cu組成。Silicide電阻和Silicide Block電阻的失效位置和機理有所區(qū)別。 Silicide電阻的失效主要發(fā)生在接觸孔和poly的接觸面 ,因為鎢合金和poly上的NiSi緩沖層的方塊電阻差值較大,當(dāng)過大的電流通過時,poly接觸面與W接觸孔產(chǎn)生熱梯度,從而造成失效。S ilicide Block電阻主要失效點在Cu互聯(lián) ,因為Silicide Block電阻的電阻率更大,POLY和NiSi緩沖層的結(jié)溫度更高,而Cu互聯(lián)更易受高結(jié)溫的影響,該高溫會傳遞到Cu互聯(lián)上從而造成失效。

圖十二.兩種電阻失效后的SEM/TEM圖片。

可以看出Silicide電阻的失效主要發(fā)生在鎢合金的接觸孔和多晶硅處。而Silicide Block電阻的失效主要發(fā)生在Cu互聯(lián)上。

圖十三.兩種電阻電熱特性對比。

從圖中可以看出兩種電阻電熱特性差距較大。Silicide Block電阻阻值較大,但是節(jié)溫上升幅度大,ESD下容易失效。而Silicide電阻阻值較小,但是結(jié)溫度上升較慢,針對ESD的魯棒性較好。

之前我手頭一個項目就是IO接口處的電阻發(fā)生了失效,當(dāng)時出于面積的考慮選用了類似Silicide Block的High POLY電阻,所觀察的現(xiàn)象也是連接金屬出現(xiàn)問題。而出現(xiàn)該問題是因為ESD模塊與內(nèi)部器件不匹配,通過調(diào)整ESD模塊解決的這個問題。

-

串聯(lián)電阻

+關(guān)注

關(guān)注

1文章

202瀏覽量

14946 -

SEM

+關(guān)注

關(guān)注

0文章

248瀏覽量

14594 -

NMOS管

+關(guān)注

關(guān)注

2文章

121瀏覽量

5653 -

ESD設(shè)計

+關(guān)注

關(guān)注

0文章

10瀏覽量

3475 -

寄生二極管

+關(guān)注

關(guān)注

0文章

49瀏覽量

3260

發(fā)布評論請先 登錄

相關(guān)推薦

基于EMC的ESD防護設(shè)計分析

電路級靜電防護設(shè)計技巧與ESD防護方法

【轉(zhuǎn)】電路級靜電防護設(shè)計技巧與ESD防護方法

芯片IC可靠性測試、ESD測試、FA失效分析

電路級靜電防護設(shè)計技巧與ESD防護方法

TVS管和壓敏電阻ESD防護應(yīng)用原理

貼片電阻開路失效分析

ESD與EOS失效案例分享

ESD失效和EOS失效的區(qū)別

全芯片ESD防護網(wǎng)絡(luò)

ESD防護電阻的妙用與失效分析

ESD防護電阻的妙用與失效分析

評論