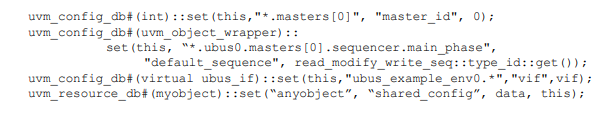

一些典型的驗證組件配置參數示例:

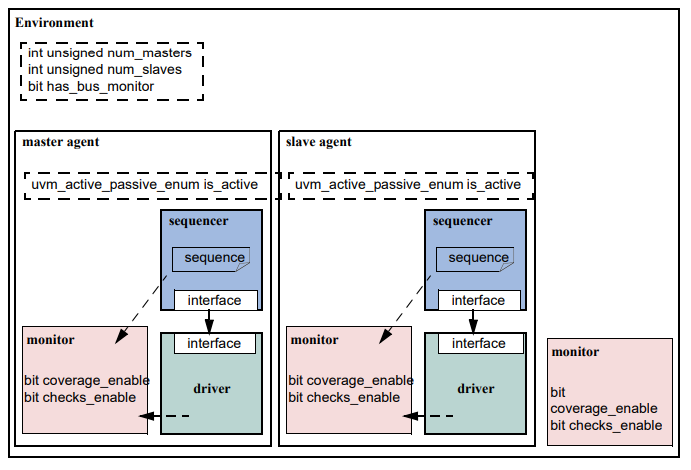

一個agent可以被配置為active或者passive模式。在active模式下agent驅動DUT,在passive模式下agent被動地檢查DUT的行為和收集DUT的覆蓋率。

monitor默認收集DUT覆蓋率和檢查DUT接口行為。用戶可以通過典型的 check_enable和coverage_enable參數禁用。

驗證組件配置機制

UVM提供了一種配置機制允許驗證環境集成者在不知道驗證組件的具體實現的條件下配置環境,示例:

uvm_config_db是一個type-specific的配置機制,配置層次化驗證環境中某個層級的參數。uvm_config_db建立在更通用的uvm_resource_db之上,uvm_resource_db提供全局非層次化的數據共享。上述:

第一個例子設置所有以masters[0]結尾的驗證組件實例的master_id參數。

第二個例子告訴masters[0].sequencer在進入main phase時執行 read_modify_write_seq 類 型的sequence。

第 三 個 例 子設置ubus_example_env0下的所有驗證組件中的vif指針變量。

最后一個例子將一些共享資源存儲到驗證層次結構中任何對象都可以訪問的位置。當uvm_resource_db::set()調用來自一個類時,最后一個參數應該是this,以允許調試信息顯示set的來源。

在uvm_resource_db和uvm_config_db之間做出選擇

uvm_config_db 和 uvm_resource_db 共 享 同 一 個 數 據庫,因此可以用uvm_config_db::set()寫數據庫,用uvm_resource_db::read_by_name()從數據庫檢索該配置。

選擇uvm_resource_db還是uvm_config_db的考量是層次路徑對參數設置是否重要。對于與層次路徑有關的配置屬性,例如,"為特定agent中的所有組件設置coverage_enable",uvm_config_db是 正 確 的 選 擇 。而如果希望配置參數被共享而不考慮層次路徑時,應該使用uvm_resource_db。

使用配置類

一些驗證組件會隨機一個配置類,這些參數配置之間的依賴關系是通過configuration object內的約束來實現的。在這種情況下,用戶可以擴展配置類以添加新的約束,在配置類被隨機化后使用uvm_config_db::set()將配置對象指針set給驗證環境。

責任編輯:彭菁

-

接口

+關注

關注

33文章

9005瀏覽量

153786 -

數據

+關注

關注

8文章

7257瀏覽量

91942 -

組件

+關注

關注

1文章

532瀏覽量

18432

原文標題:驗證組件配置

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體組件參數分析

如何通過代碼配置Delta Sigma ADC的所有組件參數

數字IC驗證之“構成uvm測試平臺的主要組件”(4)連載中...

參數化UVM IP驗證環境(上)

鴻蒙滑動拼圖驗證組件分享 已開源

鴻蒙第三方組件適配移植的滑動驗證碼教程

可重用的驗證組件中構建測試平臺的步驟

驗證組件配置參數

驗證組件配置參數

評論