樹形拓撲也是一種非常常見的拓撲,DDR2的內存條中地址控制信號經常使用這種拓撲。雖然現在信號的速率越來越高,DDR5的速率已經達到了6400Mbps,早已不再使用樹形拓撲。但學習樹形拓撲,了解其中的設計關鍵點也有助于我們分析解決其它信號完整性問題。

01

樹型拓撲介紹

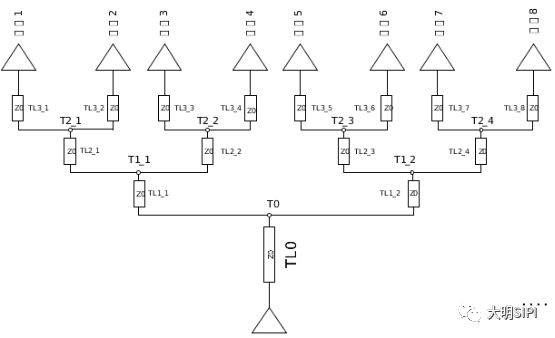

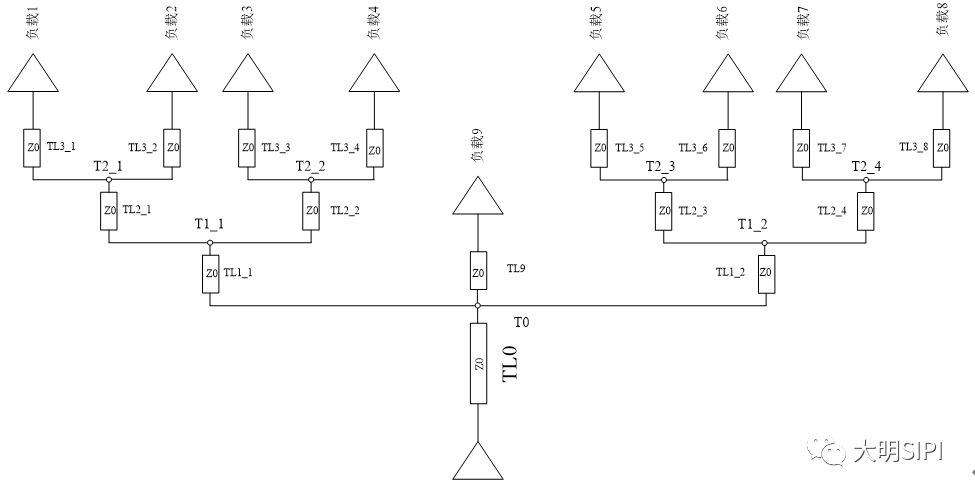

對于DDR2接口以及DDR2的DIMM設計中,地址控制信號通常使用的是樹型拓撲。如下圖所示即為樹型拓撲的示意圖,樹型拓撲也是一種對稱拓撲,相對于遠端簇拓撲來說樹型拓撲分支點處的阻抗突變要比較小。但是很明顯樹型拓撲的分支點要多很多,這就限制了樹型拓撲的應用。

下面以上圖所示的八個負載的拓撲為例對樹型拓撲結構特點做一個簡單的歸納:

(1)負載越多分支點越多,上圖鏈路中有T0、T1_1\\T1_2、T2_1~T2_4一共七個分支點為阻抗不連續點;

(2)假設所有傳輸線阻都為Z0,每個分支點前后的阻抗突變固定。分支點前阻抗為 ,信號到達分支點后感受到的阻抗為兩條分支線的并聯阻抗,即:

,信號到達分支點后感受到的阻抗為兩條分支線的并聯阻抗,即:

可以計算得到在分支點處入射波反射系數均為- 。

。

(3)此外,從各個負載反射回源端的反射信號到達各個分支點會發生反射,且各個分支點之間也會有反射信號。如果T0到T1_1\\T1_2的延時、T1_1\\T1_2到T2_1T2_4的延時以及T2_1T2_4到各個負載的延時過大(超過信號上升時間的1/3,體現明顯的傳輸線效應)都會導致信號質量的惡化。

(4)當T1_1和T1_2、T2_1~T2_4控制嚴格等長的情況下,拓撲結構對稱各個負載接收波形一致性很好。

02

樹型拓撲仿真分析

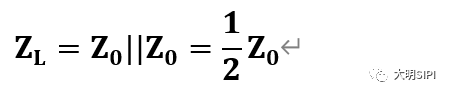

我們在ADS中搭建DDR2地址信號的仿真電路進行分析。驅動器和負載的選型與遠端簇仿真分析相同。對拓撲結構中的線長做如下設置:(1)TL0=2000mil,(2) TL1_1\\TL1_2長度為1000mil;(3)TL2_1TL2_4長度為700mil;(4)TL3_1TL3_8長度為500mil。

圖1.樹型拓撲ADS仿真電路

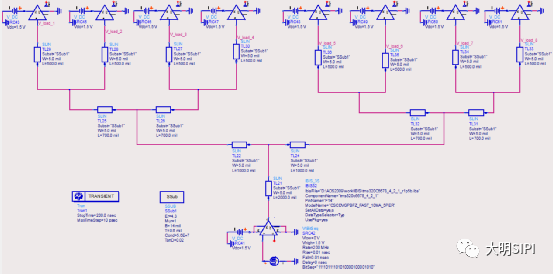

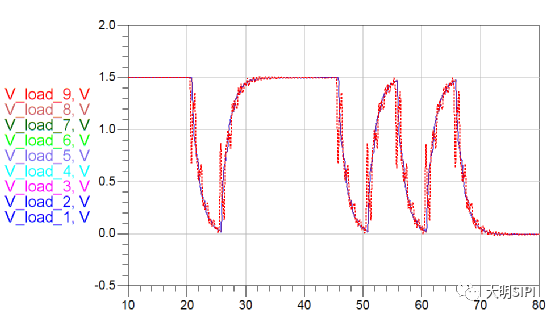

圖2. 速率400Mbps,各個負載的仿真波形

信號邊沿單調、但是由于負載過重負載端接收的信號邊沿過緩,這是由于樹型拓撲這種一分二、二分四的拓撲結構使得整個拓撲中布線的總長度會非常長也使布線引起的容性負載會非常大。如果PCB設計中允許雙面布局我們可以將負載1和2、3和4、5和6、7和8分別進行正反對貼布局,也就是top面布負載1、3、5、7,bottom面布局負載2、4、6、8。這樣的話可以極大地縮小布局面積和每一級分支的布線長度,減小布線的容性效益。

另外,同樣需要注意分支布線的延時過大會在信號邊沿產生回溝或者臺階影響數據信號的時序裕量和時鐘信號的邊沿單調性。尤其是TL3_1~TL3_8的布線長度對信號質量的影響非常大,有興趣的讀者可以自行驗證。樹型拓撲結構的設計規則也更加復雜,信號完整性工程師需要綜合器件的布局和層疊設置等因素給出信號質量滿足設計要求的拓撲結構,并對線路各個部分的阻抗、分支長度等作出詳細的約束規則,否則很容易導致設計的失敗。

02

樹型拓撲的變型

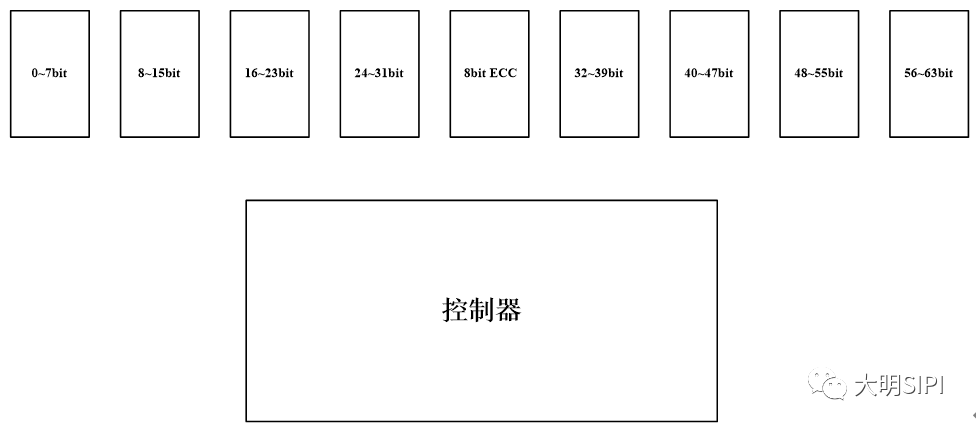

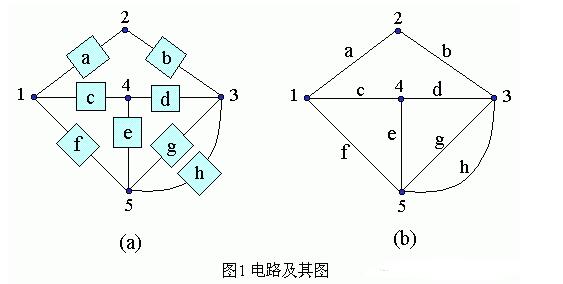

樹型拓撲的一分二、二分四的拓撲結構使得負載的數量必須是2、4、8、16等值,也就是 2的n次方(n為正整數)。但在實際的應用中通常會遇到負載的個數不是 的情況。比如說帶有ECC功能的DDR2接口。對于一個64位的DDR2總線需要8片8位的DDR2顆粒組成,但如果要增加ECC功能就需要再增加一片DDR,此時整個拓撲的負載個數就是9個。那么我們應該為地址控制信號選擇什么樣的拓撲結構以使信號質量達到最優。在控制器和內存顆粒的布局時,我們通常是將ECC DDR2顆粒布局在最中間的位置。如下所示:

的情況。比如說帶有ECC功能的DDR2接口。對于一個64位的DDR2總線需要8片8位的DDR2顆粒組成,但如果要增加ECC功能就需要再增加一片DDR,此時整個拓撲的負載個數就是9個。那么我們應該為地址控制信號選擇什么樣的拓撲結構以使信號質量達到最優。在控制器和內存顆粒的布局時,我們通常是將ECC DDR2顆粒布局在最中間的位置。如下所示:

此時我們在布線時最容易選擇的一種拓撲結構就是將ECC芯片的fanout過孔作為地址控制信號樹型拓撲的第一個分支點。這種拓撲結構看起來似乎很是最合理的,相對于樹型拓撲改動很小,并不會改變原有的布線層疊設置,不會因為多出的一片DDR導致布線層數的增加,而且拓撲對稱性好。但事實上這種拓撲是否能夠滿足信號完整性要求呢?

圖3.一驅九的DDR2拓撲

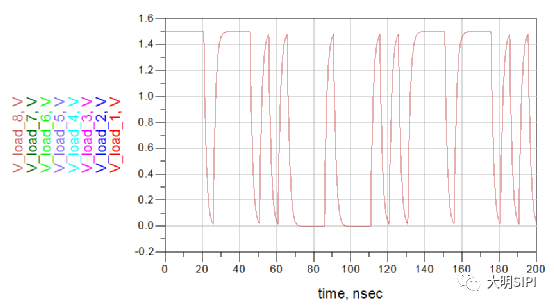

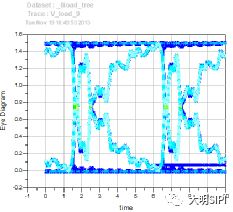

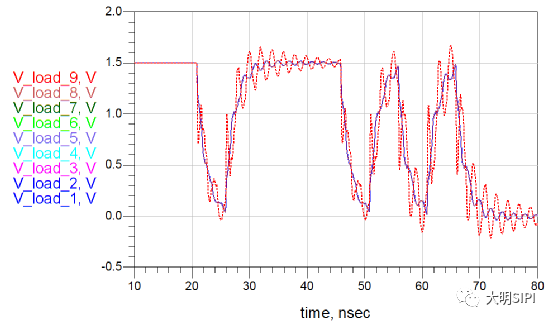

在圖.3樹型拓撲的基礎上按照圖.3樹型拓撲變型所示的方式增加一個ECC DDR負載9,設置TL9布線長度為100mil進行仿真(僅為fanout線長度)。仿真的結果顯示負載1~8的接收波形完全一致能夠滿足信號質量的要求,但是負載9的接收波形無論是信號的邊沿還是高低電平處都存在著很多的回溝振蕩嚴重影響信號的噪聲裕量和時序裕量。

圖4.樹型拓撲變型仿真結果(TL9 = 100mil)

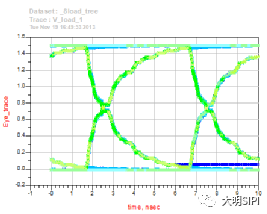

圖5.(左)負載9的接收眼圖;(右)負載1的接收眼圖

負載1~8的波形非常一致而且信號質量非常好這并不難理解,但為什么負載9接收的信號質量最差呢?

其實無論拓撲中有沒有負載9在第一個分支點T0處信號波形都是很差的,我們可以在8個負載的樹型拓撲結構中進行驗證觀測一下T0點的信號波形。究其原因就是因為T0點作為第一個分支點是拓撲的主干路上的分支點,所有負載、以及其它分支點處發生的反射都會匯聚到這一點,從而對這一點附近的負載接收信號的信號質量產生影響。

如果這樣的話是否可以考慮將TL9的長度設置為2300mil(TL3+TL2+TL1)這樣負載9到分支點的延時從表面上來看就和其它負載一致了。我們再來看一下仿真結果,點虛線為負載9接收波形、實線為其它負載接收波形。

圖6.樹型拓撲變型仿真結果(TL9 = 2300mil)

調整TL9長度后并沒有使負載9的信號質量好轉,反而使其它負載的信號質量也惡化了。由此我們可以得出結論:將ECC芯片放在拓撲結構的中間并不合適,我們需要重新設計地址控制線的拓撲結構。

有人可能會提出我們可以采用一分三、三分九的拓撲這樣應該可以解決現在的問題。但需要注意這樣做會導致PCB設計難度甚至PCB板成本的提高,如果有興趣可以自行驗證一下。

-

驅動器

+關注

關注

54文章

8646瀏覽量

149260 -

DDR2

+關注

關注

1文章

104瀏覽量

41908 -

信號完整性

+關注

關注

68文章

1438瀏覽量

96499 -

ADS仿真

+關注

關注

1文章

71瀏覽量

10801 -

DIMM

+關注

關注

0文章

30瀏覽量

9759

發布評論請先 登錄

labview樹形結構問題

樹形結構輸出數值

ddr3菊花鏈拓撲結構是什么

什么是電路拓撲結構_多種pfc電路的拓撲結構介紹

PROFINET網絡支持星型、樹型、總線型、環形和混合型網絡拓撲結構

ZigBee模塊通信協議的樹形拓撲組網結構

樹形拓撲結構的設計關鍵點

樹形拓撲結構的設計關鍵點

評論