David Skolnick 和 Noam Levine

如果您已經(jīng)閱讀了本系列的第1部分(或者已經(jīng)熟悉DSP處理實(shí)際信號(hào)的一些方法),您可能想詳細(xì)了解如何使用DSP實(shí)現(xiàn)數(shù)字濾波器(如第1部分中描述的濾波器)。本文是系列文章的第二篇,介紹以下 DSP 主題:

建模過濾器變換函數(shù)

將模型與 DSP 架構(gòu)相關(guān)聯(lián)

嘗試使用數(shù)字濾波器

本系列旨在從希望將DSP添加到其設(shè)計(jì)庫中的模擬系統(tǒng)設(shè)計(jì)人員的角度來描述這些主題。使用本系列文章中的信息作為介紹,設(shè)計(jì)人員可以就何時(shí)DSP設(shè)計(jì)可能比模擬電路更高效做出更明智的決策。

建模過濾器轉(zhuǎn)換函數(shù)

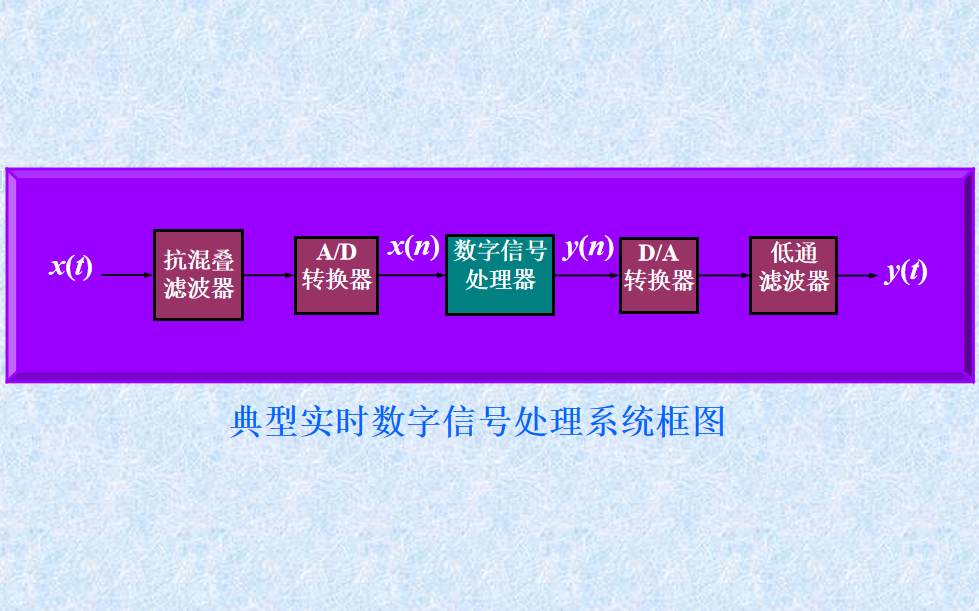

第1部分比較了模擬和數(shù)字濾波器的特性,并提出了為什么可以通過數(shù)字方式(使用DSP)實(shí)現(xiàn)這些濾波器;本部分重點(diǎn)介紹數(shù)字濾波器應(yīng)用的一些機(jī)制。

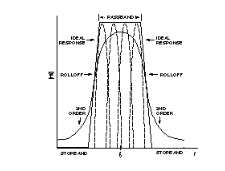

使用數(shù)字濾波的三個(gè)主要原因是(1)更接近理想濾波器近似值,(2)能夠在軟件中調(diào)整濾波器特性,而不是通過物理調(diào)諧,以及(3)濾波器響應(yīng)與采樣數(shù)據(jù)的兼容性。第1部分介紹的兩個(gè)最著名的濾波器是有限脈沖響應(yīng)(FIR)和無限脈沖響應(yīng)(IIR)類型。FIR 濾波器響應(yīng)稱為有限響應(yīng),因?yàn)樗妮敵鰞H基于一組有限的輸入樣本;它是非遞歸的,沒有極點(diǎn),在其S平面上只有零。另一方面,IIR濾波器的響應(yīng)可以無限期地持續(xù)(并且可能不穩(wěn)定),因?yàn)樗沁f歸的,即其輸出值受到輸入和輸出的影響。它的 s 平面上有極點(diǎn)和零點(diǎn)。圖 1 顯示了第 1 部分中出現(xiàn)的典型濾波器架構(gòu)和求和公式。

圖1.濾波器方程及其延遲線模型。

要對(duì)這些過濾器進(jìn)行數(shù)字建模,可能需要兩個(gè)步驟。首先,將這些公式視為在計(jì)算機(jī)上運(yùn)行的程序。此步驟包括將公式分解為數(shù)學(xué)步驟(例如,乘法和加法),并確定計(jì)算機(jī)執(zhí)行所需的所有其他操作(處理指令和數(shù)據(jù),測試狀態(tài)等)以在軟件中實(shí)現(xiàn)公式。

其次,將這些操作編寫為程序。這可能是一項(xiàng)相當(dāng)艱巨的任務(wù)。幸運(yùn)的是,有很多“預(yù)制”軟件可用,通常是像C這樣的高級(jí)語言(HLL),在某種程度上簡化了(但絕不是消除!)編程工作。不過,從學(xué)習(xí)的角度來看,從匯編語言開始可能更有啟發(fā)性;此外,匯編語言算法通常比必須優(yōu)化系統(tǒng)性能的 HLL 更有用。在某些高級(jí)語言的抽象級(jí)別,程序可能看起來不太像方程。例如,圖 2 顯示了作為 C 程序?qū)崿F(xiàn)的 FIR 算法的示例。

float fir_filter(float input, float *coef, int n, float *history)

{

int i;

float *hist_ptr, *hist1_ptr, *coef_ptr;

float output;

hist_ptr = history;

hist1_ptr = hist_ptr; /* use for history update */

coef_ptr = coef + n -1; /* point to last coef */

/*form output accumulation */

output = *hist_ptr++ * (*coef_ptr-);

for(i = 2; i < n; i++)

{

*hist1_ptr++ = *hist_ptr; /* update history array */

output += (*hist_ptr++) * (*coef_ptr-);

}

output += input * (*coef_ptr); /* input tap */

*hist1_ptr = input; /* last history */

return(output);

}

有許多支持算法建模的分析包可用;請參閱本文末尾的參考資料,了解幾個(gè)流行的軟件包。在本系列的不同時(shí)間,我們將回到算法建模。現(xiàn)在,繼續(xù)討論該過程,在這些濾波器算法建模之后,它們就可以在DSP架構(gòu)中實(shí)現(xiàn)了。

將模型與DSP架構(gòu)相關(guān)聯(lián):對(duì)于編程,必須了解DSP架構(gòu)的四個(gè)部分:數(shù)字、存儲(chǔ)器、序列器和I/O操作。此體系結(jié)構(gòu)討論是通用的(適用于一般 DSP 概念),但它也是具體的,因?yàn)樗c本文后面的編程示例相關(guān)。圖 3 顯示了本節(jié)介紹的通用 DSP 架構(gòu)。

建筑

數(shù)字部分:由于 DSP 必須在單個(gè)指令周期內(nèi)完成乘法/累加、加、減和/或位移運(yùn)算,因此針對(duì)數(shù)字運(yùn)算優(yōu)化的硬件是所有 DSP 處理器的核心。正是這種硬件將DSP與通用微處理器區(qū)分開來,通用微處理器可能需要許多周期才能完成這些類型的操作。在數(shù)字濾波器(和其他DSP算法)中,DSP必須完成涉及數(shù)據(jù)值和系數(shù)的多個(gè)算術(shù)運(yùn)算步驟,以實(shí)時(shí)產(chǎn)生通用處理器無法實(shí)現(xiàn)的響應(yīng)。

數(shù)字運(yùn)算發(fā)生在DSP的乘法/累加器(MAC)、算術(shù)邏輯單元(ALU)和桶形移位器(移位器)中。MAC執(zhí)行乘積總和運(yùn)算,這些運(yùn)算出現(xiàn)在大多數(shù)DSP算法(如FIR和IIR濾波器以及快速傅里葉變換)中。ALU 功能包括加法、減法和邏輯運(yùn)算。對(duì)位和字的操作發(fā)生在移位器內(nèi)。圖 3 顯示了 MAC、ALU 和移位器的并行度,以及數(shù)據(jù)如何流入和流出它們。

圖3.有用的 DSP 架構(gòu)。

從編程的角度來看,使用單獨(dú)數(shù)字部分的DSP架構(gòu)提供了極大的靈活性和效率。數(shù)據(jù)有許多不沖突的路徑,允許單周期完成數(shù)值運(yùn)算。DSP的架構(gòu)還必須為MAC操作提供寬動(dòng)態(tài)范圍,能夠處理兩倍于輸入寬度的乘法結(jié)果,以及可以安裝而不會(huì)溢出的累加器輸出。(在 16 位 DSP 上,此功能相當(dāng)于 MAC 的 16 位數(shù)據(jù)輸入和 40 位結(jié)果輸出。需要此范圍來處理大多數(shù)DSP算法(例如濾波器)。

數(shù)字部分的其他功能可以促進(jìn)實(shí)時(shí)系統(tǒng)中的編程。通過使操作依賴于由數(shù)值運(yùn)算產(chǎn)生的各種條件狀態(tài),這些狀態(tài)可以作為程序執(zhí)行、進(jìn)位、溢出、飽和、標(biāo)志或其他狀態(tài)測試中的變量。使用這些條件,DSP 可以根據(jù)數(shù)值運(yùn)算快速處理有關(guān)程序流的決策。需要不斷將數(shù)據(jù)饋送到數(shù)字部分,這是影響DSP存儲(chǔ)器和內(nèi)部總線結(jié)構(gòu)的關(guān)鍵設(shè)計(jì)因素。

內(nèi)存部分:DSP存儲(chǔ)器和總線架構(gòu)設(shè)計(jì)以速度需求為導(dǎo)向。數(shù)據(jù)和指令必須在每個(gè)指令周期流入DSP的數(shù)字和排序部分。不能有延誤,不能有瓶頸。設(shè)計(jì)的所有內(nèi)容都集中在吞吐量上。

|

哈佛和馮諾依曼架構(gòu)的詞源 - 根據(jù)弗吉尼亞理工大學(xué)計(jì)算機(jī)科學(xué)系的John A. N. Lee: 哈佛系列機(jī)器的開發(fā)者霍華德·艾肯(Howard Aiken)堅(jiān)持在他的所有機(jī)器中分離數(shù)據(jù)和程序。在我最熟悉的Mark III中,他甚至為每個(gè)鼓準(zhǔn)備了不同尺寸的鼓。 “馮·諾依曼的概念是,通過將指令視為數(shù)據(jù),可以對(duì)程序進(jìn)行更改,增強(qiáng)程序'學(xué)習(xí)'的能力。 “出于某種原因,后者被賦予了馮·諾依曼的名字,而前者的名字來自哈佛大學(xué)的機(jī)器系列。” |

為了正確看待吞吐量,可以看看DSP存儲(chǔ)器設(shè)計(jì)與其他微處理器存儲(chǔ)器之間的區(qū)別。大多數(shù)微處理器使用包含數(shù)據(jù)和指令的單個(gè)存儲(chǔ)器空間,使用一條總線作為地址,另一條用于數(shù)據(jù)或指令。這種架構(gòu)被稱為馮諾依曼架構(gòu)。馮諾依曼架構(gòu)中對(duì)吞吐量的限制來自于必須在每個(gè)周期的一段數(shù)據(jù)或一條指令之間進(jìn)行選擇。在DSP中,存儲(chǔ)器通常分為程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器,每個(gè)存儲(chǔ)器都有單獨(dú)的總線。這種類型的架構(gòu)被稱為哈佛架構(gòu)。通過分離數(shù)據(jù)和指令,DSP可以在每個(gè)周期中獲取多個(gè)項(xiàng)目,從而使吞吐量翻倍。指令緩存、結(jié)果反饋和上下文切換等其他優(yōu)化也提高了 DSP 吞吐量。

DSP 存儲(chǔ)器架構(gòu)中的其他優(yōu)化與重復(fù)存儲(chǔ)器訪問有關(guān)。大多數(shù)DSP算法(如數(shù)字濾波器)需要以重復(fù)訪問模式從存儲(chǔ)器中獲取數(shù)據(jù)。通常,這種類型的訪問用于從一系列地址中獲取數(shù)據(jù),該范圍充滿了來自要處理的真實(shí)信號(hào)的數(shù)據(jù)。通過減少“管理”存儲(chǔ)器訪問所需的指令數(shù)量(開銷),DSP可以“保存”指令周期,從而為每個(gè)周期處理信號(hào)的主要工作留出更多時(shí)間。為了減少開銷并自動(dòng)管理這些類型的訪問,DSP 利用專用數(shù)據(jù)地址生成器 (DAG)。

大多數(shù)DSP算法要求在單個(gè)周期內(nèi)從存儲(chǔ)器中獲取兩個(gè)操作數(shù),以成為算術(shù)單元的輸入。為了以靈活的方式提供這兩個(gè)操作數(shù)的地址,DSP 有兩個(gè) DAG。在DSP改進(jìn)的哈佛架構(gòu)中,一個(gè)地址生成器通過數(shù)據(jù)存儲(chǔ)器地址總線提供地址;另一個(gè)通過程序存儲(chǔ)器地址總線提供地址。通過為下一條數(shù)字指令及時(shí)執(zhí)行這兩個(gè)數(shù)據(jù)獲取,DSP能夠維持指令的單周期執(zhí)行。

DSP算法(例如示例數(shù)字濾波器)通常需要對(duì)地址范圍(緩沖區(qū))中的數(shù)據(jù)進(jìn)行尋址,以便地址指針從緩沖區(qū)的末尾“環(huán)繞”回緩沖區(qū)的開頭(緩沖區(qū)長度)。此指針移動(dòng)稱為循環(huán)緩沖。(在濾波器方程中,每個(gè)求和基本上都是由數(shù)據(jù)點(diǎn)循環(huán)緩沖區(qū)和系數(shù)循環(huán)緩沖區(qū)的乘法累加序列得出的)。循環(huán)緩沖的變體(在某些應(yīng)用程序中是必需的)將地址指針推進(jìn)每個(gè)“步長”大于一個(gè)地址的值,但仍以給定長度環(huán)繞。這種變化稱為模循環(huán)緩沖。

通過其DAG支持各種類型的緩沖,DSP能夠在硬件中執(zhí)行地址修改和比較操作,以實(shí)現(xiàn)最佳效率。在軟件中執(zhí)行這些功能(如在通用處理器中發(fā)生)會(huì)限制處理器處理實(shí)時(shí)信號(hào)的能力。

由于緩沖是一個(gè)不尋常的概念,但卻是數(shù)字信號(hào)處理的關(guān)鍵,因此一個(gè)簡短的緩沖示例非常有用。在圖 4 所示的示例中,從地址 30 開始,內(nèi)存中駐留了八個(gè)位置的緩沖區(qū)。地址生成器必須計(jì)算保留在此緩沖區(qū)內(nèi)的下一個(gè)地址,但保持適當(dāng)?shù)臄?shù)據(jù)間距,以便跳過兩個(gè)位置。地址生成器將地址 30 輸出到地址總線上,同時(shí)將地址修改為 33 以進(jìn)行下一個(gè)周期的內(nèi)存訪問。此過程重復(fù),在緩沖區(qū)中移動(dòng)地址指針。當(dāng)?shù)刂?36 修改為 39 時(shí),會(huì)出現(xiàn)特殊情況。地址 39 位于緩沖區(qū)外部。地址生成器檢測到地址已落在緩沖區(qū)邊界之外,并將地址修改為 31,就像緩沖區(qū)的末尾連接到緩沖區(qū)的開頭一樣。更新、比較和修改不會(huì)產(chǎn)生任何開銷。在一個(gè)周期內(nèi),地址36被輸出到地址總線上。在下一個(gè)周期,地址31被輸出到地址總線上。這種模循環(huán)緩沖可滿足插值濾波器等算法的需求,并節(jié)省處理指令周期。

圖 4.模循環(huán)緩沖示例。

音序器部分:由于大多數(shù)DSP算法(例如示例濾波器)本質(zhì)上是重復(fù)的,因此DSP的程序序列器需要循環(huán)遍歷重復(fù)的代碼,而不會(huì)產(chǎn)生開銷,同時(shí)從循環(huán)的結(jié)束返回到循環(huán)的開始。此功能稱為零開銷循環(huán)。能夠在沒有開銷的情況下進(jìn)行環(huán)路是DSP與傳統(tǒng)微處理器區(qū)別的一個(gè)關(guān)鍵領(lǐng)域。通常,微處理器要求在軟件中維護(hù)程序循環(huán),在循環(huán)的末尾放置條件指令。此條件指令確定地址指針是移動(dòng)(跳轉(zhuǎn))回循環(huán)頂部還是另一個(gè)地址。由于從存儲(chǔ)器中獲取這些地址需要時(shí)間,而信號(hào)處理時(shí)間的可用性在DSP應(yīng)用中至關(guān)重要,因此DSP不能浪費(fèi)周期以這種方式檢索條件程序排序(分支)的地址。相反,DSP 在硬件中執(zhí)行這些測試和分支功能,存儲(chǔ)所需的地址。

如圖5所示,DSP在一個(gè)周期內(nèi)執(zhí)行環(huán)路的最后一條指令。在下一個(gè)周期,DSP評(píng)估條件并執(zhí)行循環(huán)頂部的第一條指令或環(huán)路外的第一條指令。由于 DSP 使用專用硬件進(jìn)行這些操作,因此不會(huì)在軟件評(píng)估條件、檢索地址或分支程序執(zhí)行上浪費(fèi)額外的時(shí)間。

圖5.程序循環(huán)示例。

輸入/輸出 (I/O) 部分:正如一再指出的那樣,需要向DSP提供巨大的數(shù)據(jù)吞吐量;關(guān)于其設(shè)計(jì)的所有內(nèi)容都集中在將數(shù)據(jù)匯集到數(shù)字、內(nèi)存和序列器部分。數(shù)據(jù)的來源和輸出的目的地(信號(hào)處理的結(jié)果)是DSP與其系統(tǒng)和現(xiàn)實(shí)世界的連接。完成信號(hào)處理任務(wù)需要許多I/O功能。非 DSP 存儲(chǔ)器陣列存儲(chǔ)處理器指令和數(shù)據(jù)。通信通道(如串行端口、I/O 端口和直接存儲(chǔ)器訪問 (DMA)通道)將數(shù)據(jù)快速傳入和傳出 DSP。其他功能(如定時(shí)器和程序啟動(dòng)邏輯)簡化了DSP系統(tǒng)開發(fā)。DSP 系統(tǒng)中典型 I/O 任務(wù)的簡要列表包括以下內(nèi)容(以及許多其他任務(wù)):

引導(dǎo)加載:在復(fù)位時(shí),DSP通常通過外部存儲(chǔ)器接口從外部源(EPROM或主機(jī))加載指令。

串行通信:DSP 通過同步串行端口 (SPORT) 接收或傳輸數(shù)據(jù),與編解碼器、ADC、DAC 或其他設(shè)備通信。

內(nèi)存映射 I/O:DSP 通過外部設(shè)備解碼的非 DSP 存儲(chǔ)器位置接收或傳輸數(shù)據(jù)。

試驗(yàn)數(shù)字濾波器

在對(duì)濾波器算法進(jìn)行建模并查看了一些DSP架構(gòu)特性之后,人們準(zhǔn)備開始研究如何用DSP匯編語言對(duì)這些濾波器進(jìn)行編碼。到目前為止,討論和示例都是通用的,幾乎適用于所有DSP。此處的示例特定于ADI公司的ADSP-2181。該處理器是一個(gè)定點(diǎn)、16 位 DSP。術(shù)語“定點(diǎn)”是指分隔尾數(shù)和指數(shù)的“點(diǎn)”在算術(shù)運(yùn)算期間不會(huì)改變其位位置。定點(diǎn)DSP的編程可能更具挑戰(zhàn)性,但它們往往比浮點(diǎn)DSP便宜。“16位DSP”中的“16位”是指DSP數(shù)據(jù)字的大小。該DSP使用16位數(shù)據(jù)字和24位寬指令字。DSP 由數(shù)據(jù)大小而不是指令寬度指定,因?yàn)閿?shù)據(jù)字大小描述了 DSP 可以最有效地處理的數(shù)據(jù)寬度。

該軟件有兩個(gè)部分。主例程包括寄存器和緩沖區(qū)初始化以及中斷向量表,以及數(shù)據(jù)樣本準(zhǔn)備就緒時(shí)執(zhí)行的中斷例程。初始化后,DSP 在主例程中執(zhí)行指令,執(zhí)行一些后臺(tái)任務(wù)、循環(huán)訪問代碼或在低功耗待機(jī)模式下空閑,直到從 A/D 轉(zhuǎn)換器獲得中斷。在此示例中,處理器在低功耗待機(jī)模式下空閑,等待中斷。

FIR 濾波器中斷子例程(代碼的最后一段)是濾波器程序的核心。處理器響應(yīng)中斷,保存主例程的上下文并跳轉(zhuǎn)到中斷例程。此中斷例程處理濾波器輸入樣本,從存儲(chǔ)器讀取數(shù)據(jù)和濾波器系數(shù),并將其存儲(chǔ)在DSP處理器的數(shù)據(jù)寄存器中。處理輸入樣本后,DSP將輸出樣本發(fā)送到D/A轉(zhuǎn)換器。

.module/RAM/ABS=0 FIR_PROGRAM;

/******** Initialize Constants and Variables *****************/

.const taps=127;

.var/dm/circ data[taps];

.var/pm/circ fir_coefs[taps];

.init fir_coefs: ;

.var/dm/circ output_data[taps];

/******** Interrupt vector table *****************************/

reset_svc: jump start; rti; rti; rti;

/*00: reset */

irq2_svc: /*04: IRQ2 */

si=io(0); /* get next sample */

dm(i0,m0)=si; /* store in tap delay line */

jump fir; /* jump to fir filter */

nop; /* nop is placeholder */

irql1_svc: rti; rti; rti; rti; /*08: IRQL1 */

irql0_svc: rti; rti; rti; rti; /*0c: IRQL0 */

sp0tx_svc: rti; rti; rti; rti; /*10: SPORT0 tx */

sp0rx_svc: rti; rti; rti; rti; /*14: SPORT1 rx */

irqe_svc: rti; rti; rti; rti; /*18: IRQE */

bdma_svc: rti; rti; rti; rti; /*1c: BDMA */

sp1tx_svc: rti; rti; rti; rti; /*20: SPORT1 tx or IRQ1 */

sp1rx_svc: rti; rti; rti; rti; /*24: SPORT1 rx or IRQ0 */

timer_svc: rti; rti; rti; rti; /*28: timer */

pwdn_svc: rti; rti; rti; rti; /*2c: power down */

/******* START OF PROGRAM - initialize mask, pointers **********/

start:

/* set up various control registers */

ICNTL=0x07; /* set IRQ2, IRQ1, IRQ0 edge sensitive */

IFC=0xFF; /* clear all pending interrupts */

NOP; /* add nop because of one cycle */

/* synchronization delay of IFC */

SI=0x0000;

DM(0x3FFF)=SI; /* sports not enabled */

/* sport1 set for IRQ1, IRQ0, FI, FO */

IMASK=0x200; /* enable IRQ2 interrupt */

i0=^data; /* index to data buffer */

l0=taps; /* length of data buffer */

m0=1; /* post modify value */

i4=^fir_coefs; /* index to fir_coefs buffer */

l4=taps; /* length of fir_coefs buffer */

m4=1; /* post modify value */

i2=^output_data; /* index to data buffer */

l2=taps; /* length of data buffer */

cntr=taps;

do zero until ce;

dm(i0,m0)=0; /* clear out the tap delay data buffer */

zero: dm(i2,m0)=0; /* clear out the output_data buffer */

/**** WAIT for IRQ2 Interrupt - then JUMP to INTERRUPT VECTOR **/

wait: idle; /* wait for IRQ2 interrupt */

jump wait;

/******* FIR FILTER interrupt subroutine ***********************/

fir cntr=taps-1; /* set up loop counter */

mr=0, mx0=dm(i0,m0), my0=pm(i4,m4);

/* fetch data and coefficient */

do fir1loop until ce; /* set up loop */

fir1loop: mr=mr+mx0*my0(ss), mx0=dm(i0,m0), my0=pm(i4,m4);

/* calculations */

/* if not ce jump fir1loop;*/

mr=mr+mx0*my0(rnd); /* round final result to 16-bits */

if mv sat mr; /* if overflow, saturate */

io(1)=mr1; /* send result to DAC */

dm(i2,m0)=mr1;

rti;

/******* END OF PROGRAM *************************************/

.endmod;

請注意,此程序使用 DSP 功能,這些功能以零開銷執(zhí)行操作,通常由條件引入。特別是,程序循環(huán)和數(shù)據(jù)緩沖區(qū)以零開銷進(jìn)行維護(hù)。濾波器循環(huán)核心中的多功能指令執(zhí)行乘法/累加運(yùn)算,同時(shí)從內(nèi)存中獲取下一個(gè)數(shù)據(jù)字和濾波器系數(shù)。

程序檢查過濾器計(jì)算的最終結(jié)果是否有任何溢出。如果最終值溢出,則該值將飽和以模擬模擬信號(hào)的削波。最后,恢復(fù)主例程的上下文,并通過中斷返回 (RTI) 指令將指令流返回到主例程。

查看和預(yù)覽

本文的目的是提供濾波器理論與數(shù)字濾波器實(shí)現(xiàn)之間的聯(lián)系。在此過程中,本文將介紹如何使用 HLL 程序?qū)V波器進(jìn)行建模、使用 DSP 架構(gòu)以及試驗(yàn)濾波器軟件。本文介紹的問題包括:

過濾器作為程序

DSP 架構(gòu)(通用)

DSP 匯編語言

由于這些問題涉及許多有價(jià)值的細(xì)節(jié)級(jí)別,在這篇簡短的文章中無法公正地描述,因此您應(yīng)該考慮閱讀Richard Higgins的文本,VLSI中的數(shù)字信號(hào)處理和Paul Embree的文本,實(shí)時(shí)DSP的C算法(見下面的參考文獻(xiàn))。這些文本提供了DSP理論,實(shí)現(xiàn)問題和實(shí)踐簡化(發(fā)布時(shí)可用的設(shè)備)的完整概述,以及練習(xí)和示例。下面的參考部分還包含進(jìn)一步放大本文問題的其他來源。為準(zhǔn)備本系列的下一篇文章,您可能需要免費(fèi)獲取ADSP-2100系列用戶手冊*或ADSP-2106x SHARC用戶手冊。 這些文本提供有關(guān)ADI公司的定點(diǎn)和浮點(diǎn)DSP架構(gòu)的信息,這是這些文章的主要主題。在本系列中,每個(gè)部分都增加了一些功能或信息,有助于實(shí)現(xiàn)開發(fā)DSP系統(tǒng)的系列目標(biāo)。

審核編輯:郭婷

-

dsp

+關(guān)注

關(guān)注

555文章

8142瀏覽量

355311 -

模擬電路

+關(guān)注

關(guān)注

125文章

1590瀏覽量

103690 -

濾波器

+關(guān)注

關(guān)注

162文章

8076瀏覽量

181066

發(fā)布評(píng)論請先 登錄

數(shù)字信號(hào)處理器DSP技術(shù)入門(附送算法設(shè)計(jì)與系統(tǒng)方案)

哪位大神關(guān)于《數(shù)字信號(hào)處理與數(shù)字信號(hào)處理器》的DSP論.....

DSP數(shù)字信號(hào)處理介紹

DSP數(shù)字信號(hào)處理簡述

《DSP系統(tǒng)課程設(shè)計(jì)》教學(xué)大綱

數(shù)字信號(hào)處理(DSP)應(yīng)用系統(tǒng)中的低功耗設(shè)計(jì)

數(shù)字信號(hào)處理入門指南

數(shù)字信號(hào)處理器(DSP)

基于DSP的數(shù)字信號(hào)處理實(shí)驗(yàn)設(shè)計(jì)

DSP是什么?詳解DSP又稱數(shù)字信號(hào)處理器

基于DSP的數(shù)字信號(hào)采集處理系統(tǒng)設(shè)計(jì)

數(shù)字信號(hào)處理和DSP系統(tǒng)的學(xué)習(xí)教程免費(fèi)下載

數(shù)字信號(hào)處理:DSP系統(tǒng)設(shè)計(jì)入門課程

數(shù)字信號(hào)處理:DSP系統(tǒng)設(shè)計(jì)入門課程

數(shù)字信號(hào)處理:DSP系統(tǒng)設(shè)計(jì)入門課程

評(píng)論