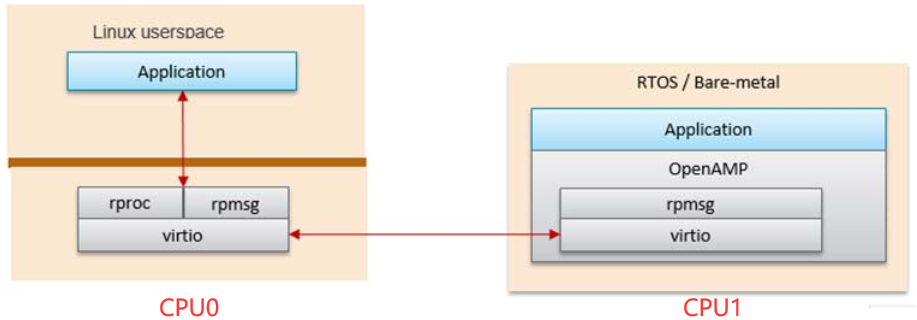

前 言:本文主要介紹基于OpenAMP框架的雙核ARM通信案例的使用說明,CPU0(Master)運(yùn)行Linux系統(tǒng),CPU1(Remote)運(yùn)行裸機(jī)或FreeRTOS程序。CPU0使用remoteproc加載CPU1程序,并對CPU1進(jìn)行配置。

圖 1

OpenAMP詳細(xì)開發(fā)說明可查閱官方文檔。

本文基于Xilinx Zynq-7010/7020平臺進(jìn)行案例測試。

圖2

1、echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1發(fā)送數(shù)據(jù),CPU1接收到數(shù)據(jù)后再使用RPMsg向CPU0回傳數(shù)據(jù)。CPU0對回傳的數(shù)據(jù)進(jìn)行驗(yàn)證,并輸出驗(yàn)證結(jié)果。

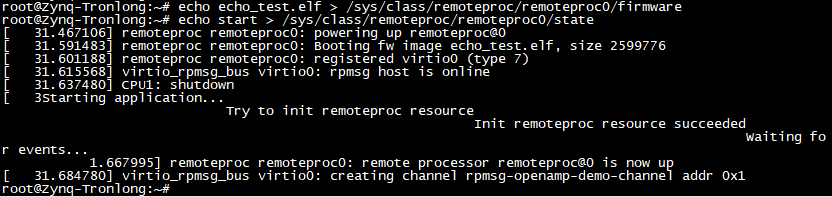

1.2 操作說明

將CPU1裸機(jī)或FreeRTOS可執(zhí)行文件復(fù)制到評估板文件系統(tǒng)“/lib/firmware/”目錄下,并執(zhí)行如下命令加載CPU1程序。

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

圖 3

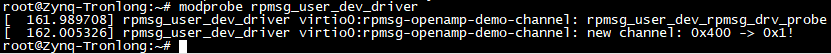

執(zhí)行如下命令加載RPMsg驅(qū)動,并在“/dev/”目錄下生成RPMsg設(shè)備節(jié)點(diǎn)。

Target# modprobe rpmsg_user_dev_driver

圖 4

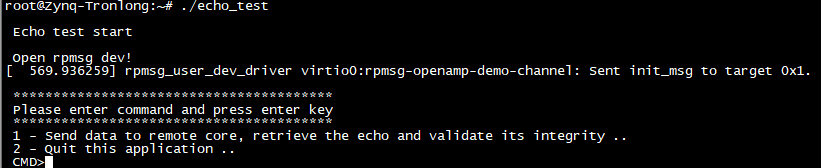

將CPU0應(yīng)用程序可執(zhí)行文件復(fù)制到評估板文件系統(tǒng),并執(zhí)行如下命令通過RPMsg與CPU1進(jìn)行通信。

Target# ./echo_test

圖 5

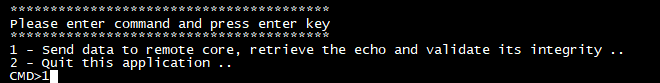

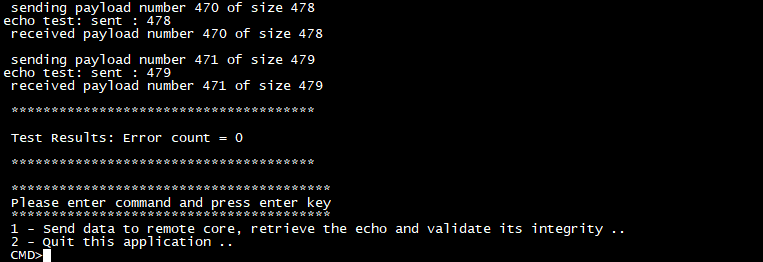

輸入1,并按回車鍵進(jìn)行測試。

圖 6

圖 7

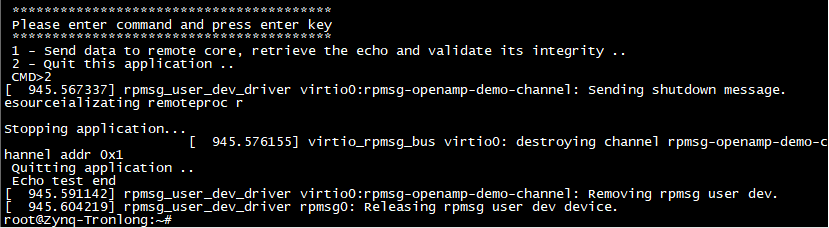

輸入2,并按回車鍵退出測試。

圖 8

執(zhí)行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

圖 9

2、matrix_multiply案例

2.1 案例功能

案例功能:CPU0隨機(jī)生成兩個矩陣并使用RPMsg向CPU1發(fā)送數(shù)據(jù),CPU1接收到數(shù)據(jù)后進(jìn)行矩陣乘法運(yùn)算,再使用RPMsg向CPU0回傳運(yùn)算結(jié)果,然后CPU0通過串口終端輸出運(yùn)算結(jié)果。

2.2 操作說明

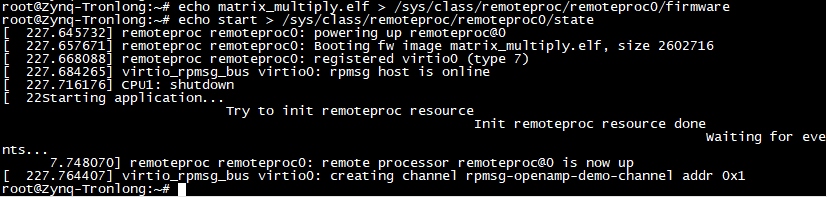

將CPU1裸機(jī)或FreeRTOS可執(zhí)行文件復(fù)制到評估板文件系統(tǒng)“/lib/firmware/”目錄下,并執(zhí)行如下命令加載CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

圖 10

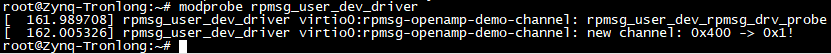

執(zhí)行如下命令加載RPMsg驅(qū)動,并在“/dev/”目錄下生成RPMsg設(shè)備節(jié)點(diǎn)。

Target# modprobe rpmsg_user_dev_driver

圖 11

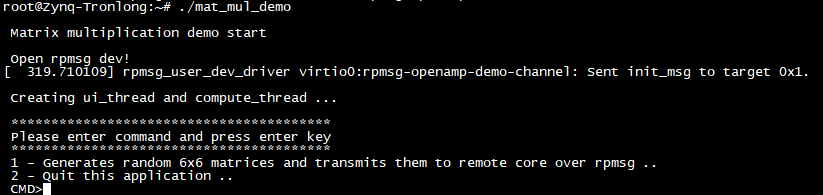

將CPU0應(yīng)用程序可執(zhí)行文件復(fù)制到評估板文件系統(tǒng),并執(zhí)行如下命令通過RPMsg與CPU1進(jìn)行通信。

Target# ./mat_mul_demo

圖 12

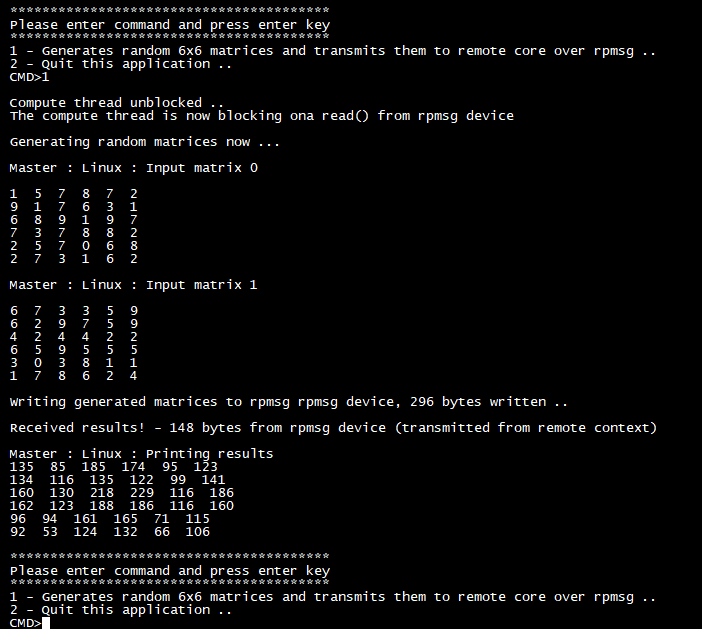

輸入1,并按回車鍵進(jìn)行測試。

圖 13

輸入2,并按回車鍵退出測試。

圖 14

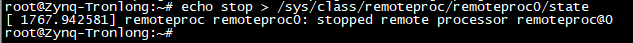

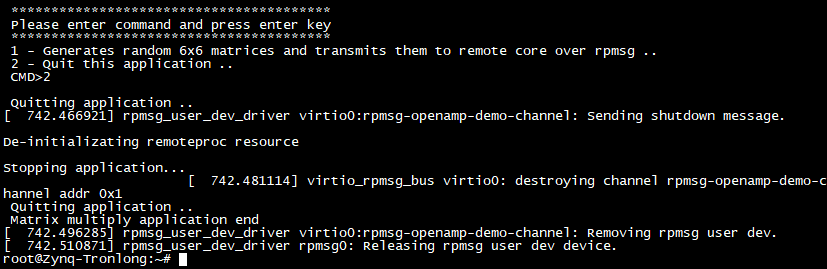

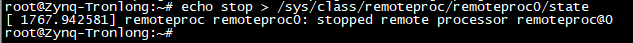

執(zhí)行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

圖 15

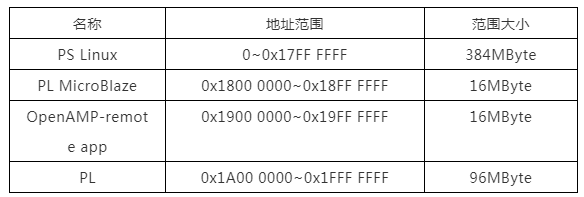

3、內(nèi)存分配說明

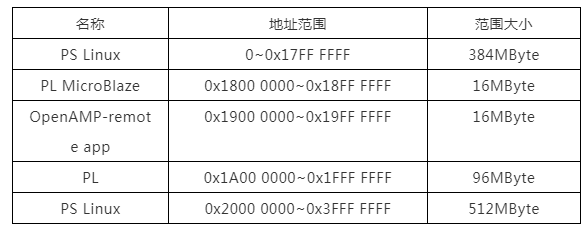

512MByte DDR容量版本核心板的內(nèi)存地址分配如下:

表 1

1GByte DDR容量版本核心板的內(nèi)存地址分配如下:

表 2

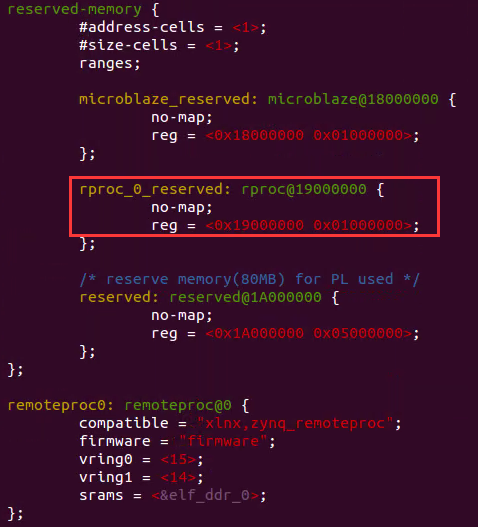

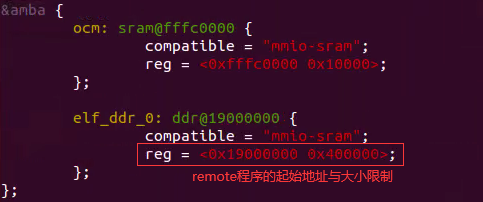

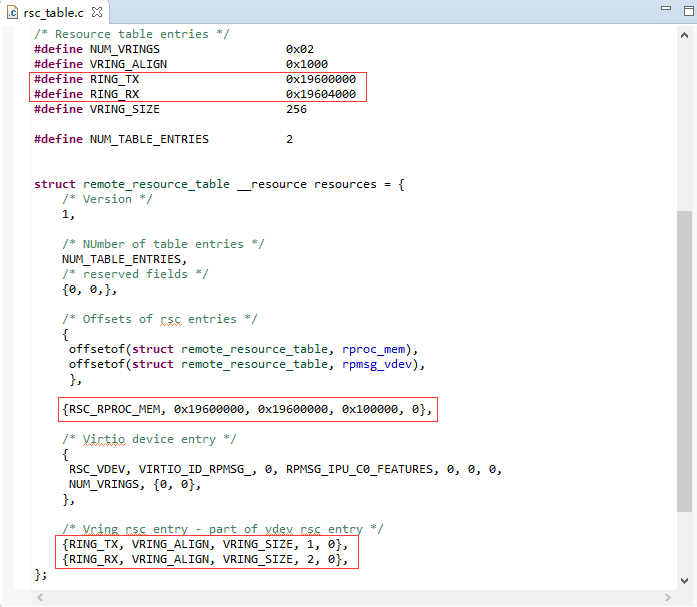

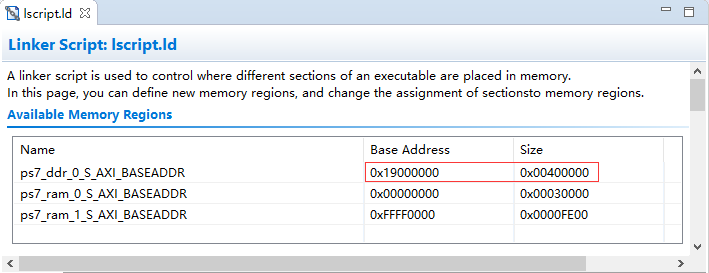

如需修改CPU1程序(OpenAMP-remote app)內(nèi)存地址空間范圍,可通過更改設(shè)備樹文件tlz7x-easyevm-s.dts、資源表rsc_table.c及鏈接文件lscript.ld對內(nèi)存地址空間進(jìn)行重新分配。三者需同步修改并保持一致,以確保固件程序鏈接地址與設(shè)備樹配置的elf_ddr_0對應(yīng)。所使用的資源(內(nèi)存和virtio設(shè)備資源)不能超出設(shè)備樹文件配置的內(nèi)存范圍。

圖 16設(shè)備樹文件tlz7x-easyevm-s.dts配置

圖 17設(shè)備樹文件tlz7x-easyevm-s.dts配置

圖 18 CPU1程序資源表rsc_table.c配置

圖 19 CPU1程序鏈接文件lscript.ld配置

-

嵌入式

+關(guān)注

關(guān)注

5144文章

19575瀏覽量

315814 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

5589瀏覽量

103177 -

Zynq-7000

+關(guān)注

關(guān)注

3文章

144瀏覽量

37317 -

核心板

+關(guān)注

關(guān)注

5文章

1127瀏覽量

30696 -

工控板

+關(guān)注

關(guān)注

0文章

196瀏覽量

13459

發(fā)布評論請先 登錄

ZYNQ FPGA的PS端IIC設(shè)備接口使用

基于Xilinx ZYNQ7000 FPGA嵌入式開發(fā)實(shí)戰(zhàn)指南

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

全志T113雙核異構(gòu)處理器的使用基于Tina Linux5.0——異構(gòu)雙核通信驗(yàn)證

正點(diǎn)原子fpga開發(fā)板不同型號

【AG32開發(fā)板體驗(yàn)連載】雷達(dá)實(shí)現(xiàn)與控制

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

Xilinx ZYNQ雙核ARM通信開發(fā)實(shí)例

Xilinx ZYNQ雙核ARM通信開發(fā)實(shí)例

評論