引言

Preface

如何快速便捷的完成巨型原型驗證系統(tǒng)的組網(wǎng),并監(jiān)測系統(tǒng)的連通性及穩(wěn)定性?

如何將用戶設(shè)計快速布局映射到參與組網(wǎng)的原型驗證系統(tǒng)的每一塊 FPGA?

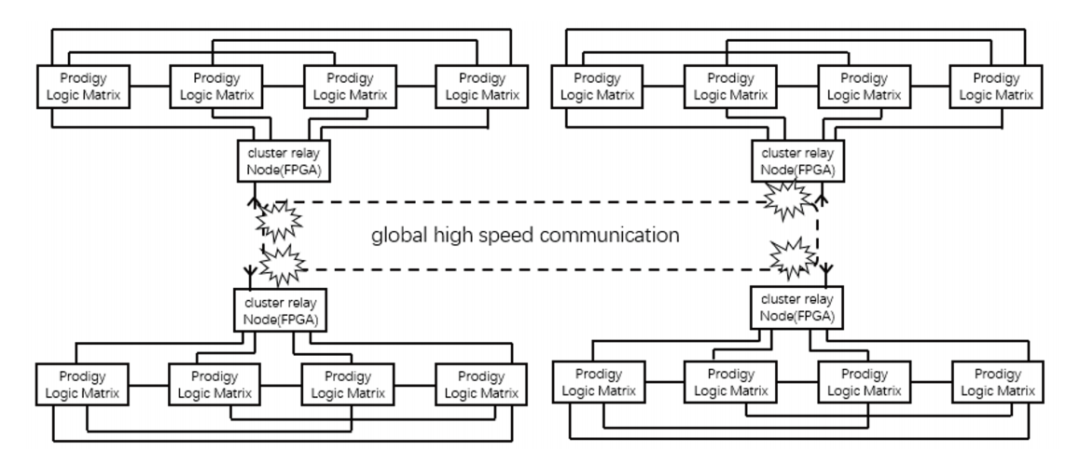

隨著用戶設(shè)計規(guī)模的日益增大,傳統(tǒng)基于單片 FPGA 或單塊電路板的原型驗證系統(tǒng)已經(jīng)遠遠不能滿足用戶的設(shè) 計驗證需求,設(shè)計團隊常需以靈活組網(wǎng)的方式,將數(shù)十甚至上百臺原型驗證系統(tǒng)“組裝”為一個完整的巨型原 型驗證系統(tǒng)。鑒于此,以上兩個問題成為了亟需解決的問題。

本次國微思爾芯白皮書《基于組網(wǎng)分割的超大規(guī)模設(shè)計 FPGA原型驗證解決方案》闡述了S2C對客戶超大型設(shè)計的原型驗證,從硬件系統(tǒng)的組建,F(xiàn)PGA 互連組網(wǎng),外設(shè)接口的可擴展性,時鐘及復(fù)位等 全局信號同步性處理,到基于 RTL 或 netlist 的設(shè)計分割算法,系統(tǒng)級靜態(tài)時序分析,增量式設(shè)計分割版本迭代的等新挑戰(zhàn)的解決思路。

核心內(nèi)容

Main Point

基于組網(wǎng)的人工可干預(yù)聚類分割

如何快速完成硬件組網(wǎng)并正確將用戶設(shè)計分割映射到每一片 FPGA?歡迎下載了解以下內(nèi)容:

硬件組網(wǎng)資源

組網(wǎng)拓撲定義

基于 RTL 級的聚類分割方案

基于 netlist 級的 TDM 模塊插入

半自動化工具庫

常見標(biāo)準組網(wǎng)

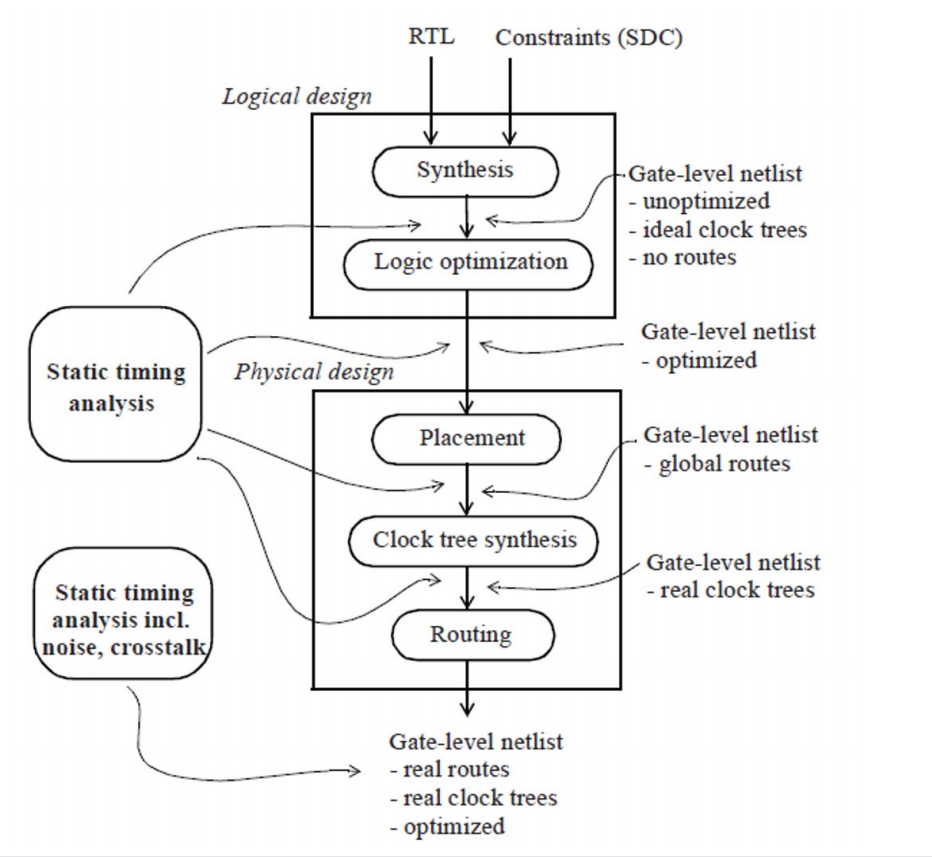

組網(wǎng)聚類分割后的系統(tǒng)靜態(tài)時序分析與仿真

如何保證分割后設(shè)計運行時的穩(wěn)定性,并優(yōu)化設(shè)計的運行速度?歡迎下載了解以下內(nèi)容:

系統(tǒng)級靜態(tài)時序分析 SSTA

STA的限制和不足

數(shù)字電路設(shè)計中的靜態(tài)時序分析

-

FPGA

+關(guān)注

關(guān)注

1644文章

22008瀏覽量

616543

發(fā)布評論請先 登錄

超大規(guī)模芯片驗證:基于AMD VP1902的S8-100原型驗證系統(tǒng)實測性能翻倍

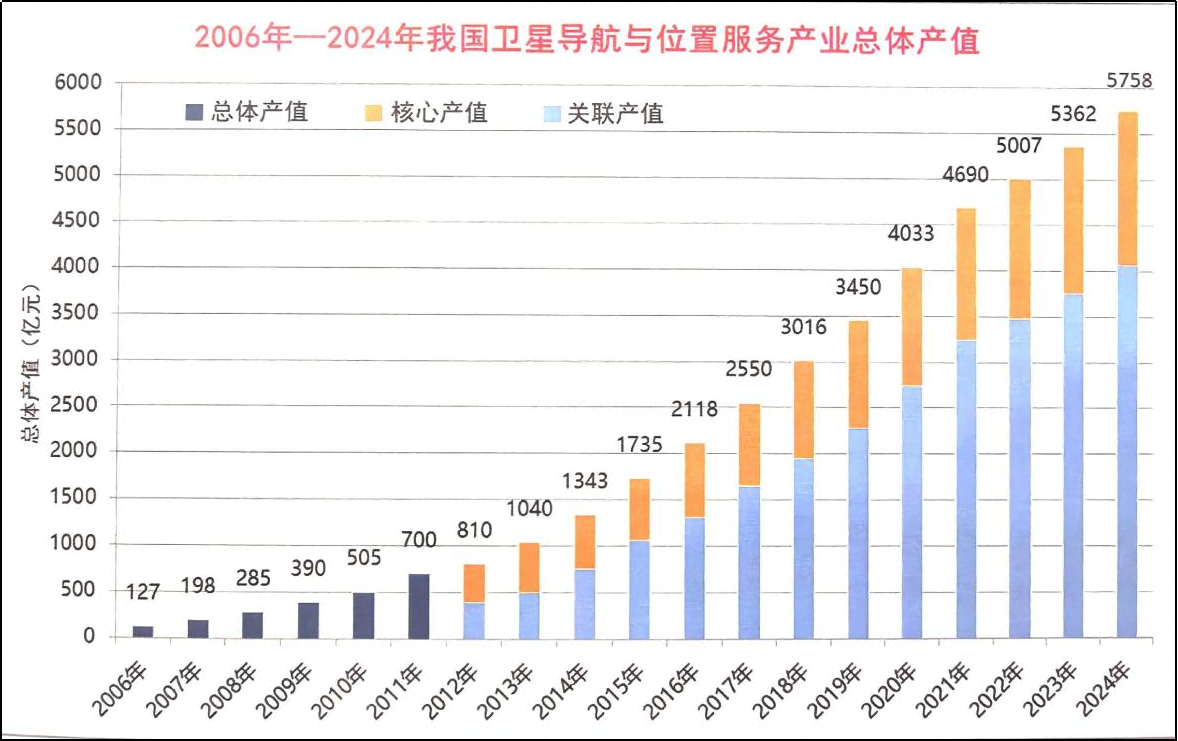

從白皮書數(shù)據(jù)看北斗規(guī)模化應(yīng)用發(fā)展前景

華為發(fā)布星河AI融合SASE解決方案白皮書

AI原生架構(gòu)升級:RAKsmart服務(wù)器在超大規(guī)模模型訓(xùn)練中的算力突破

NVIDIA Blackwell白皮書:NVIDIA Blackwell Architecture Technical Brief

雷曼光電參編的COB顯示屏調(diào)研白皮書發(fā)布

微軟發(fā)布《GraphRAG實踐應(yīng)用白皮書》助力開發(fā)者

Omdia與華為共發(fā)布NPS管理白皮書

Samtec 白皮書 | Flyover?電纜系列下篇

華為發(fā)布天線數(shù)字化白皮書

Samtec 白皮書 | Flyover?電纜系列中篇

白皮書 I 基于組網(wǎng)分割的超大規(guī)模設(shè)計 FPGA原型驗證解決方案

白皮書 I 基于組網(wǎng)分割的超大規(guī)模設(shè)計 FPGA原型驗證解決方案

評論