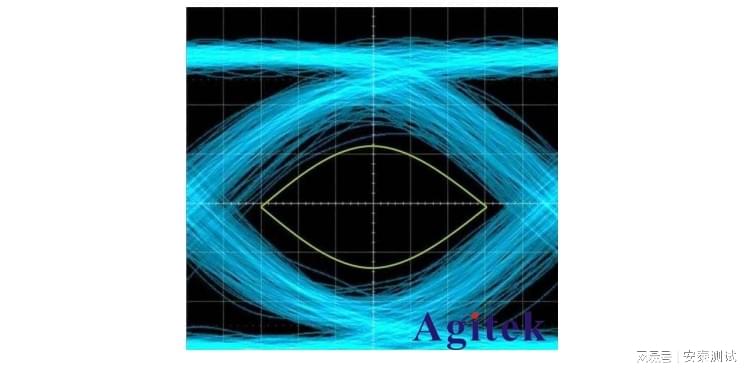

標準協議的規范中一般都對眼圖模板都有詳細的規定,使用 IBERT 完成眼圖掃描后,通過設置一些參數,即可讓 Vivado 自動將模板畫到眼圖上,具體操作步驟如下。

1// 新建 IBERT 工程

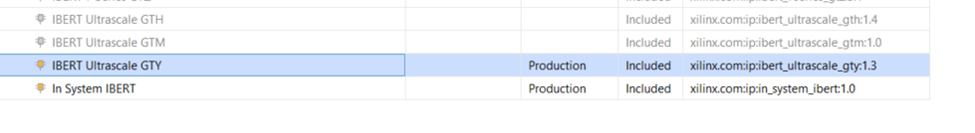

在 Vivado 的 IP Catelog 中找到 IBERT,此處以 UltraScale Plus 系列的 GTY 為例,注意 Versal GTM 不再單獨提供 IBERT,需要通過 GT Wizard 來實現。

2// 根據硬件連接設置 IBERT 參數

這里特別需要注意 Reference Clock 和 System Clock 的頻率和管腳約束,否則將會造成 PLL 無法 Lock 和 IBERT 無法在 Hardware Manager 中被識別等異常情況。

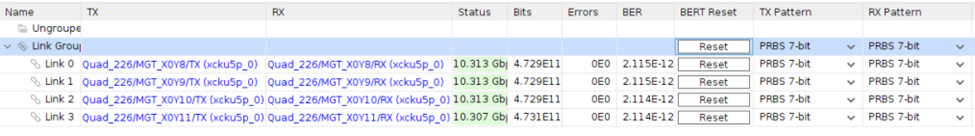

3// 下載、建立連接和掃描眼圖

IBERT 完成設置后,單擊 Generate Bitstream 生成 Bit 文件,并下載到器件。在 Serial IO links 單擊 Create Links 建立連接,為了便于測試此處將 Loopback Mode 設置為 Near End PMA,IBERT 眾多參數用戶可根據需要設置,如下圖所示:

對任意一個 Link 右擊選擇 Create Scan 即可完成眼圖掃描。

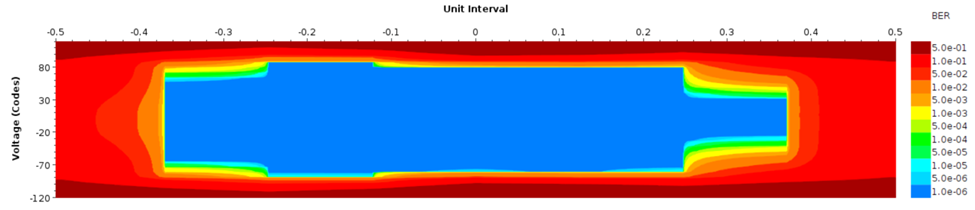

4// 添加眼圖模板

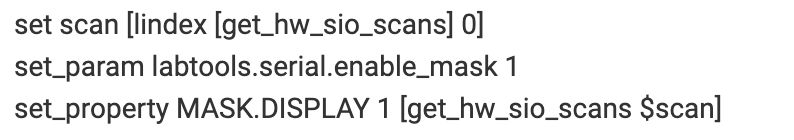

a.打開眼圖模板屬性

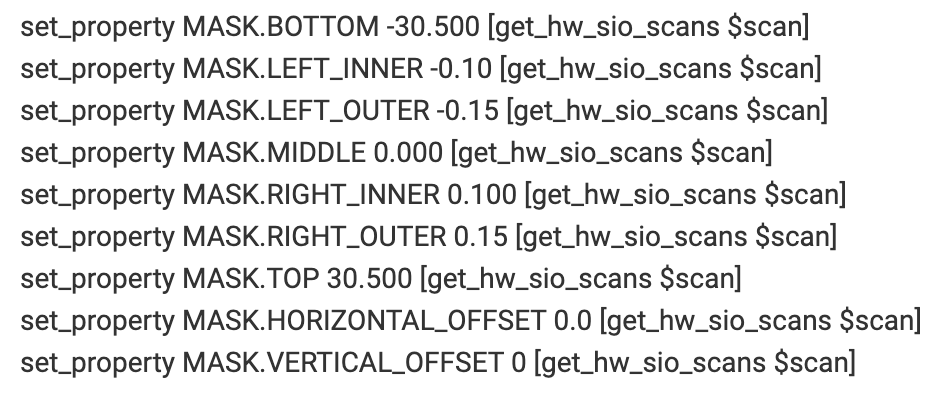

b. 并設置眼圖模板區域

c.設置眼圖模板的色彩和線寬

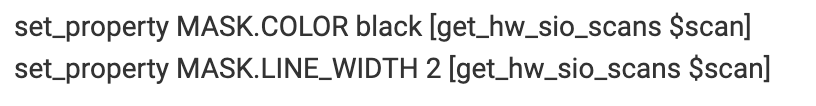

假設某協議規范中對眼圖模板的定義如下圖所示:

那么圖中每個點的 X,Y 坐標對應的屬性參照下表所示:

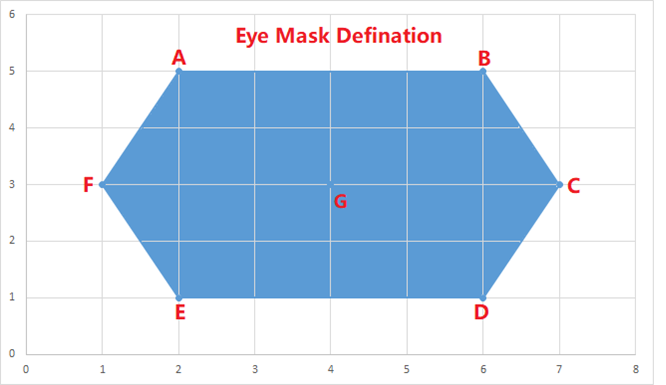

眼圖模板添加完成:

-

amd

+關注

關注

25文章

5533瀏覽量

135430 -

Xilinx

+關注

關注

73文章

2175瀏覽量

123699 -

眼圖

+關注

關注

1文章

69瀏覽量

21289 -

模板

+關注

關注

0文章

108瀏覽量

20776 -

Vivado

+關注

關注

19文章

820瀏覽量

67762

原文標題:開發者分享|Vivado Hardware Debug 技巧-如何在 IBERT 眼圖上添加模板

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

測量眼圖 眼圖代表著什么? 該如何分析眼圖的好與壞?

【設計技巧】眼圖詳解(上)

利用眼圖模板評估串行器和解串器(SerDes)的性能

PSoC Creator教程:如何在工程中添加文件

Altium Designer解答如何在BOM模板中添加行號

如何在Vivado中添加時序約束呢?

如何在IBER眼圖上添加模板

如何在IBER眼圖上添加模板

評論