現(xiàn)實世界是一個模擬世界,我們需要將現(xiàn)實世界的模擬信號送給DSP,供其處理,這就需要模擬信號和數(shù)字信號之間的一個接口,ADC和DAC。隨著DSP運算速度的加快,隨之而來的是ADC的高速和高精度性能同樣需要進一步提高。

ADC概況

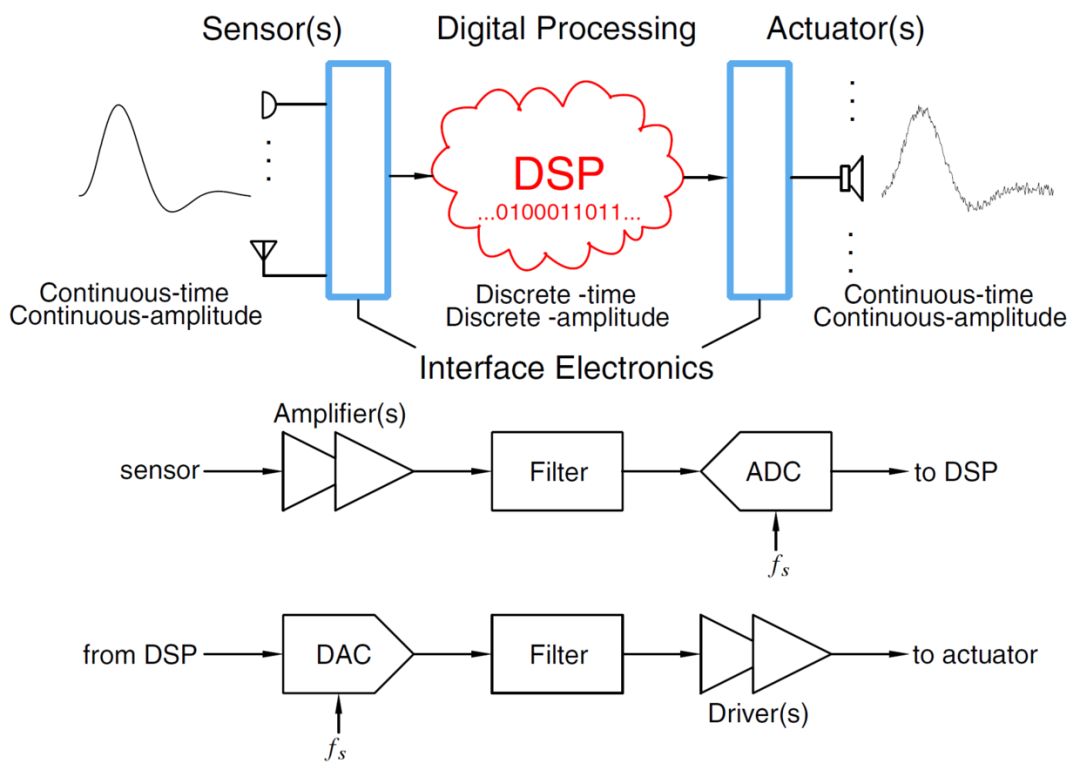

我們首先來看一下常規(guī)的電學(xué)系統(tǒng)框圖,如下圖所示,將現(xiàn)實世界的模擬信號感應(yīng)、放大、濾波,再經(jīng)過A/D轉(zhuǎn)換,送給DSP處理,處理之后送給D/A,接著濾波、放大,送給執(zhí)行器輸出。這個系統(tǒng)具有普適性,當然如果考慮射頻系統(tǒng)的話,再加上混頻器即可。從這個系統(tǒng)框圖中,我們可以看出ADC和DAC在整個電學(xué)系統(tǒng)中所處的位置和作用。其性能往往成為系統(tǒng)的瓶頸,設(shè)計高性能的ADC和DAC是非常有挑戰(zhàn)的。

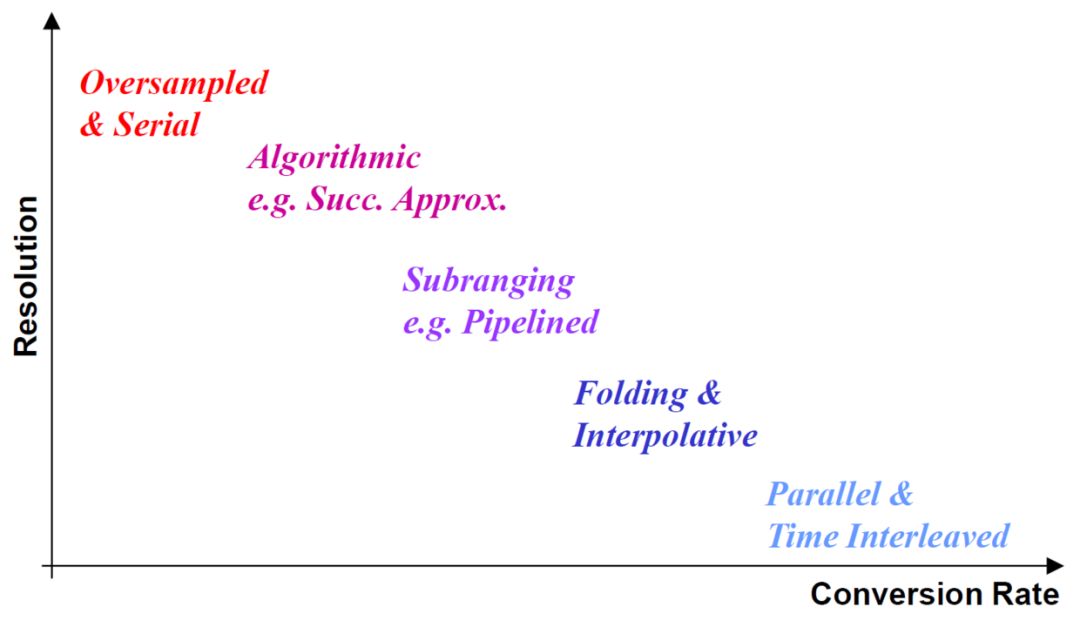

對于ADC來講,主要的設(shè)計指標是精度和速度,遺憾的是,ADC的高速和高精度的滿足是一對矛盾。不同結(jié)構(gòu)的ADC要么是犧牲速度來換取精度,要么是犧牲精度來換取速度。當然,隨著集成電路工藝的進步,以及電路設(shè)計人員的不懈努力,這對矛盾可以稍微緩解。

下圖給出了常見的ADC結(jié)構(gòu)及其可實現(xiàn)的精度和速度的對比情況,可以看到,沒有一種結(jié)構(gòu)可以同時實現(xiàn)高精度和高速度。本文接下來要介紹的是Σ-Δ ADC (Oversampled),它是以犧牲速度來換取精度的。

Σ-Δ ADC

為什么要首先介紹它呢?

正如題目所寫,它是一個非常神奇而又有趣的結(jié)構(gòu),比如,它可以采用一個單比特的量化器,實現(xiàn)多比特輸出的效果。和其它ADC結(jié)構(gòu)相比,它是結(jié)構(gòu)上的一種完全的創(chuàng)新,接下來我們一起來揭開它的神秘面紗。

在引入Σ-Δ ADC之前,首先引入一個實際的例子,以便大家理解。

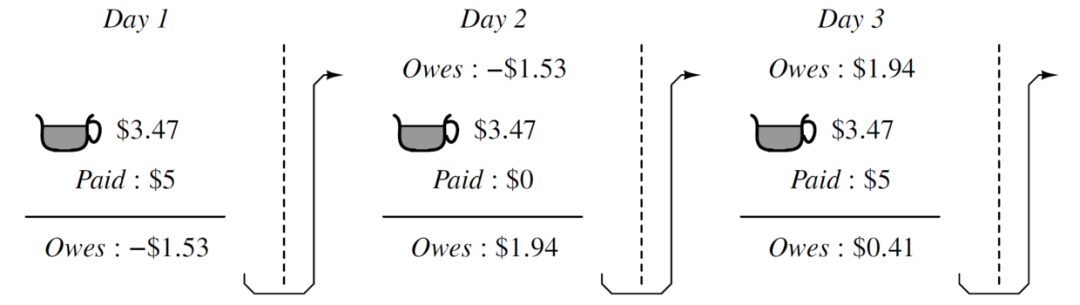

小孟在國外留學(xué)時,面對繁重的課業(yè)壓力,他每天需要喝一杯咖啡來提神。幸好學(xué)校附近有一家百年咖啡老店,以醇香的味道深深地吸引著他。這家店一杯咖啡的售價是3.47刀,不支持刷卡支付(百年老店的倔強)。剛開始時,每天他付給店員5刀,然后店員給他找零1.53刀。日積月累,大家都覺得這樣有點兒麻煩,店員需要準備大量的零錢以供找零,而小孟拿了一堆零錢也不是很方便。所以大家達成一個協(xié)議,小孟每次要不付5刀,要不不付錢,多付的或者虧欠的金額采用記賬的方式。那么小孟什么時候需要付錢呢?每當小孟買完咖啡時,如果虧欠的金額超過2.5刀時,則需要付5刀,否則不需要付錢。這個過程可以用如下的示意圖來表示,這里只給出了前三天的情況,后面的可以以此類推。其實大家可以想象到,雖然每天看起來彼此會互欠一些金額,但是長此以往,小孟所付的金額之和,和他所買咖啡的價格之和幾乎是完全一樣的,而且極大地方便了彼此。

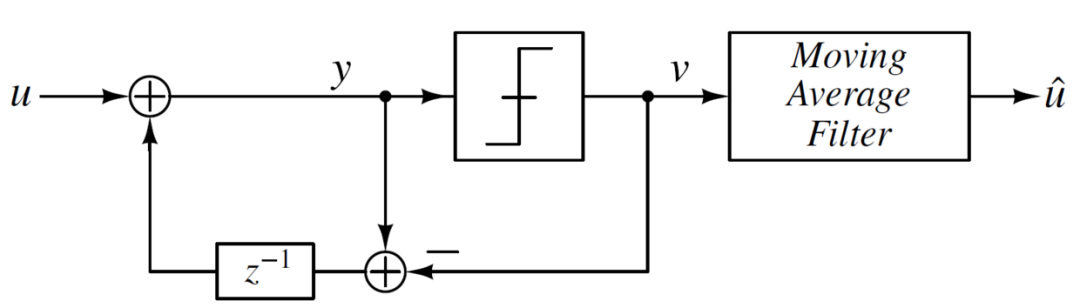

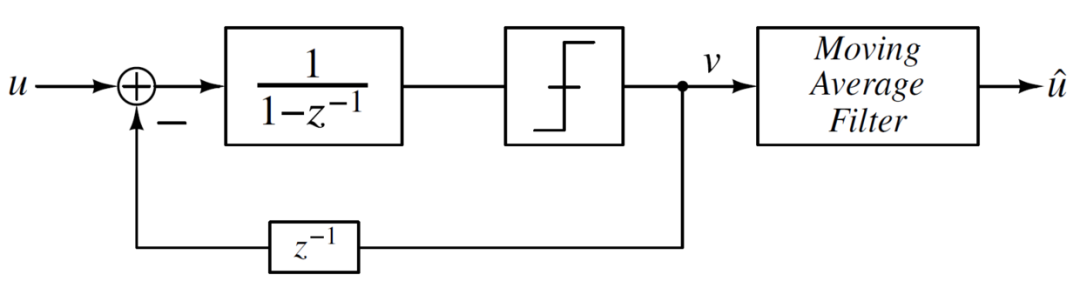

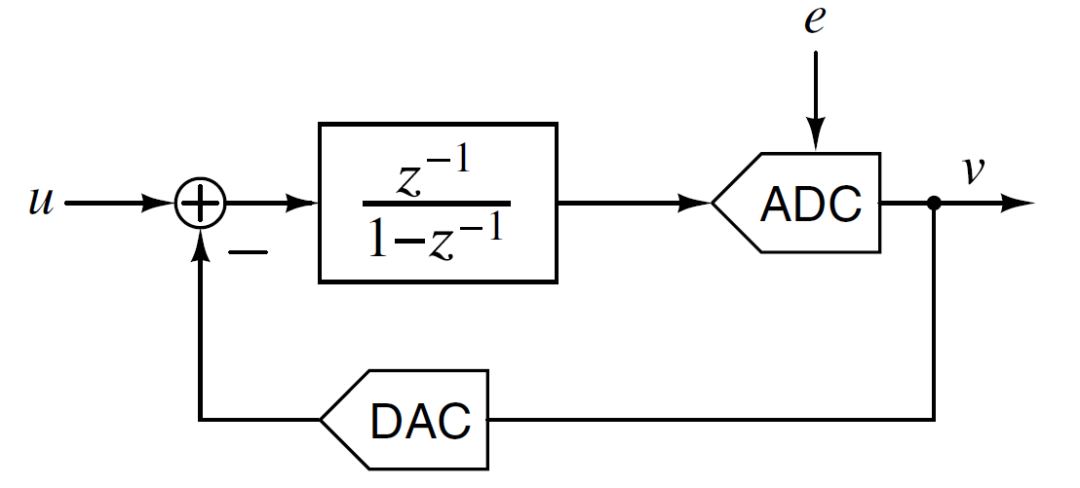

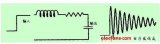

我們可以將上述過程轉(zhuǎn)換為電路語言,如下圖所示。其中,輸入u代表一杯咖啡的價格,y代表當前交易時小孟欠店主的金額,將這個金額和2.5比較,來決定當前交易是否需要付錢,比較的過程可以用一個單比特量化器表示。v表示當前付款的情況,為0,或者為5,類似一個單比特量化器的輸出結(jié)構(gòu)。然后將y和v做差,表示當前交易結(jié)束后,交易雙方互欠金額的情況,z^-1^為一個延遲單元,表示將這個互欠金額的結(jié)果送到第二天,并和第二天的咖啡價格累加,以此類推。如果將長時間v的輸出結(jié)果累加并求平均,得到的 ,可以認為近似等于輸入u。

,可以認為近似等于輸入u。

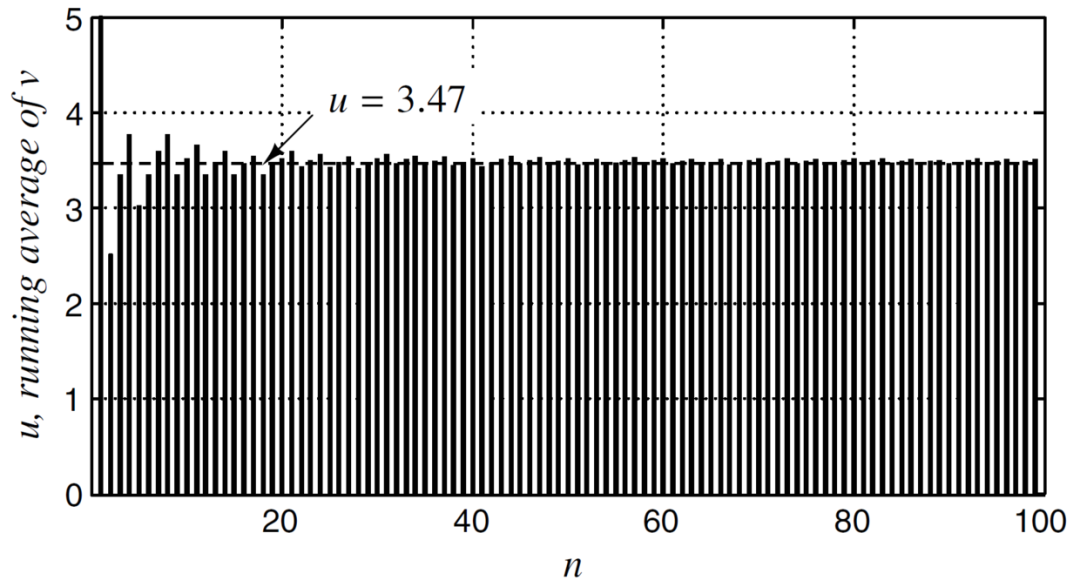

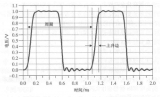

從下圖可以看出,隨著循環(huán)次數(shù)的增加,v的平均輸出非常接近輸入u。

從某種意義上來講,上述過程類似于一個模數(shù)轉(zhuǎn)換的過程。輸入的3.47為模擬值,采用二值化的量化輸出結(jié)果v的長時間平均值來表示輸出u,雖然二值化輸出結(jié)果v并不能代表模擬輸入u,但是其長時間均值卻可以代表u,這意味著將模擬信號轉(zhuǎn)換成了數(shù)字信號。

其它類型ADC的SQNR(Signal-to-Quantization-Noise Ration)取決于量化器的量化間隔,這也符合人們直觀的認識,當用一個數(shù)字信號表示模擬信號時,自然劃分的格子越細,數(shù)字信號和模擬信號越接近,意味著實現(xiàn)的精度越高。但是在Σ-Δ ADC中,采用1-bit的量化器就可以實現(xiàn)很高的分辨率,正如前文所提到的,這是一種結(jié)構(gòu)上的完全創(chuàng)新,其包含了以時間換精度的思想。

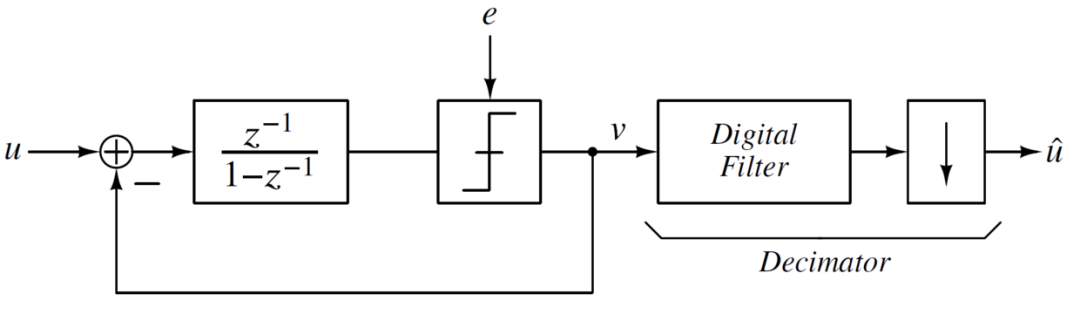

利用信號流圖的化簡,上述電路結(jié)構(gòu)可以等效成下圖所示的結(jié)構(gòu),這是Σ-Δ ADC更為常用的一種結(jié)構(gòu),稱為誤差累積結(jié)構(gòu),而上述結(jié)構(gòu)稱為誤差反饋結(jié)構(gòu)。其中1/(1-z ^-1^ )為累加器,這就是Σ的由來,Σ的輸入是u和v的差(Δ運算),所以稱為Σ-Δ 。該ADC除去輸出濾波和降采樣部分,稱為Σ-Δ調(diào)制器,至于為什么叫調(diào)制器呢,也許大家第一次接觸到的調(diào)制的概念就是通信領(lǐng)域的調(diào)制解調(diào)器,調(diào)制是指基帶信號對高頻載波信號的幅度、頻率或者相位進行改變,從而將基帶信號的信息加載到了高頻載波上。在這里,調(diào)制可以認為是對信號處理的一個過程。

對于一個穩(wěn)定的Σ-Δ ADC,量化器的平均輸入為有界信號,這也意味著累加器的平均輸入為0,所以u和v的平均值相等。

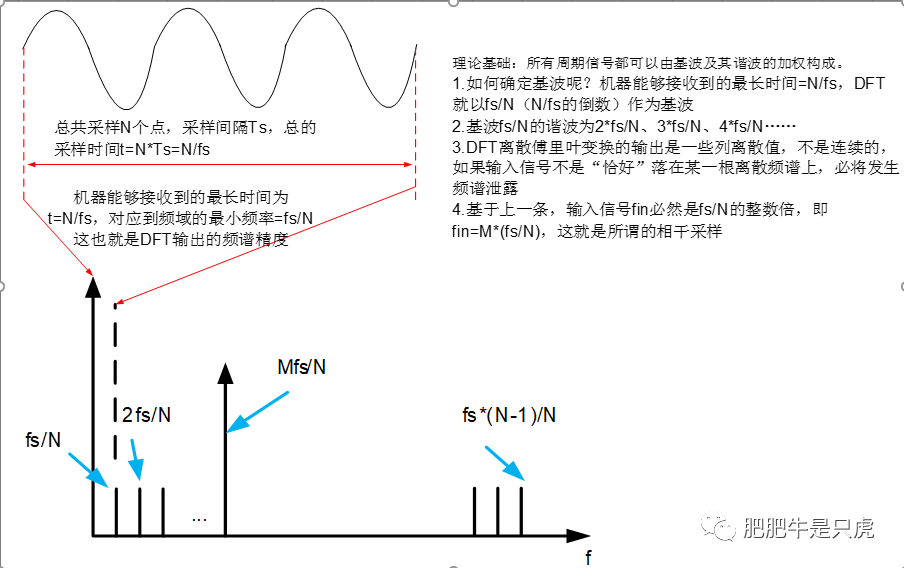

過采樣(Oversampling)

其實,上述情況是假設(shè)輸入u為一個恒定值,通過環(huán)路的迭代才使得v的平均值等于u。如果環(huán)路迭代一次,輸入u就變化一次,那么就無法實現(xiàn)多次迭代。所以,上述環(huán)路的工作速度要遠大于輸入變化的速度,因此為過采樣結(jié)構(gòu)。

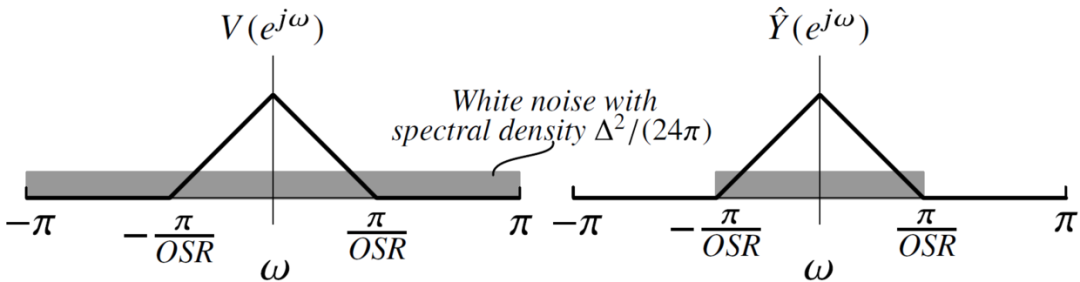

從頻域上來看,量化噪聲在2π范圍內(nèi)平均分布,由于是過采樣,所以信號只處于一個非常窄的范圍之內(nèi),通過濾波操作就極大地減小了量化噪聲。這是Σ-Δ ADC利用單比特量化實現(xiàn)了多比特輸出效果的一個原因。

過采樣本身并不能改善SQNR,而是過采樣技術(shù)和濾波操作結(jié)合才能改善SQNR。

該結(jié)構(gòu)后面的求平均的過程就是上述所提到的濾波器的濾波操作,該數(shù)字濾波器后面再接上一個降采樣的結(jié)構(gòu),將高速率的v降到和輸入u同樣的速率。

噪聲整形(Noise-shaping)

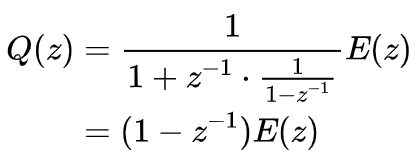

考慮量化器的量化噪聲為一個加性白噪聲。利用梅森定理,Σ-Δ調(diào)制器的量化噪聲的閉環(huán)輸出為:

其功率譜密度為:

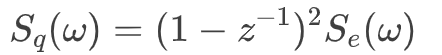

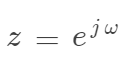

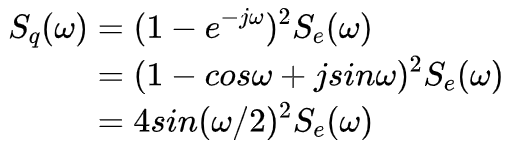

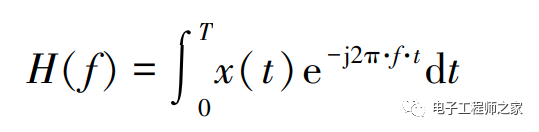

用s變換和z變換的關(guān)系 得:

得:

注意這里的ω表示數(shù)字角頻率,對應(yīng)于上一篇的Ω的。這里用ω是為了和很多文獻保持一致性。

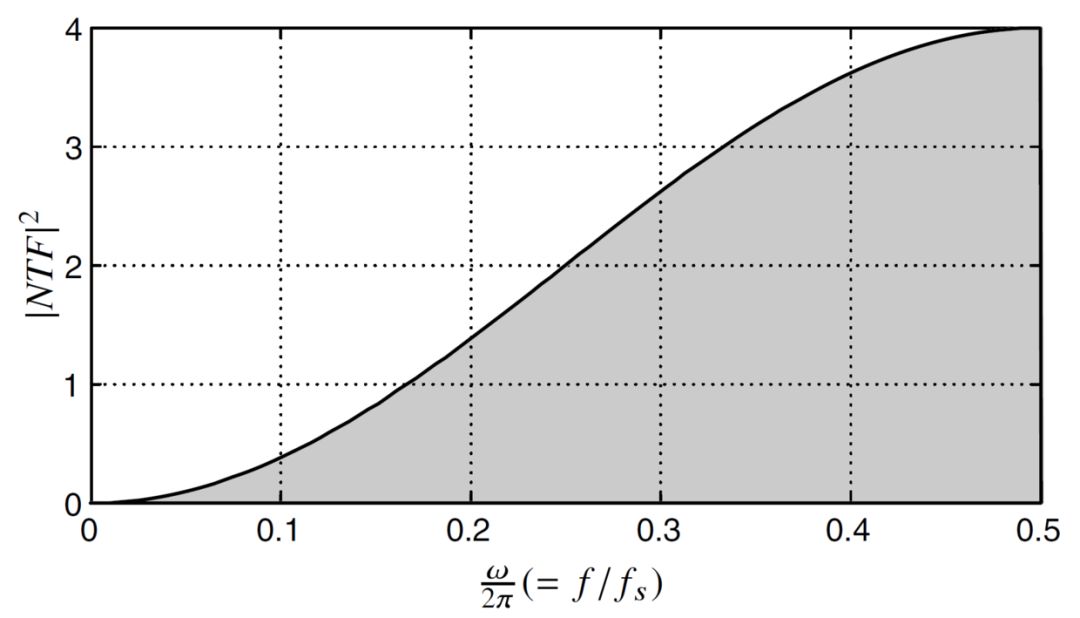

其中, 稱為噪聲傳輸函數(shù)(NTF),其幅度的平方如下圖所示,呈現(xiàn)一個高通特性。這使得處于信號帶內(nèi)的噪聲被進一步抑制,這是Σ-Δ ADC利用單比特量化實現(xiàn)了多比特輸出效果的另一個原因。

稱為噪聲傳輸函數(shù)(NTF),其幅度的平方如下圖所示,呈現(xiàn)一個高通特性。這使得處于信號帶內(nèi)的噪聲被進一步抑制,這是Σ-Δ ADC利用單比特量化實現(xiàn)了多比特輸出效果的另一個原因。

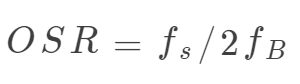

定義過采樣率為:

fB為信號的最高頻率。

fB為信號的最高頻率。

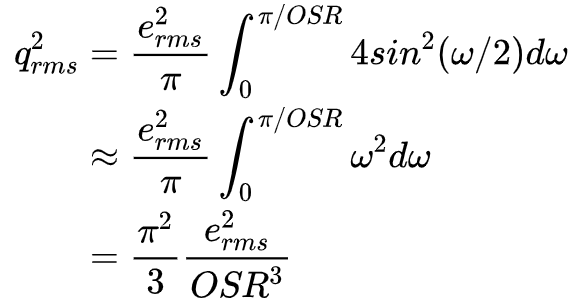

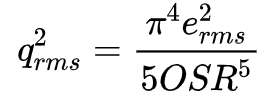

假設(shè)量化噪聲為白噪聲(通常成立),那么帶內(nèi)量化噪聲為:

上式可以看出,隨著OSR的增加,量化噪聲減小。當OSR增加一倍,量化噪聲減小9dB,也就是ENOB(effective number of bits)增加1.5bit。#### 二階Σ-Δ調(diào)制器

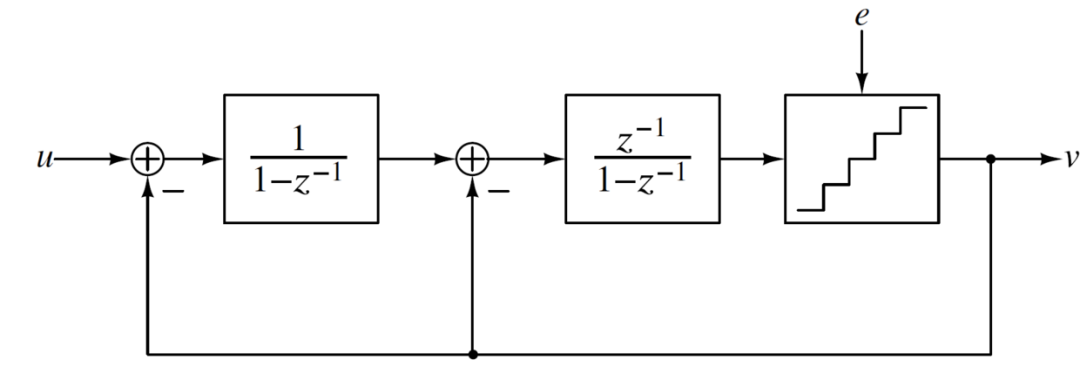

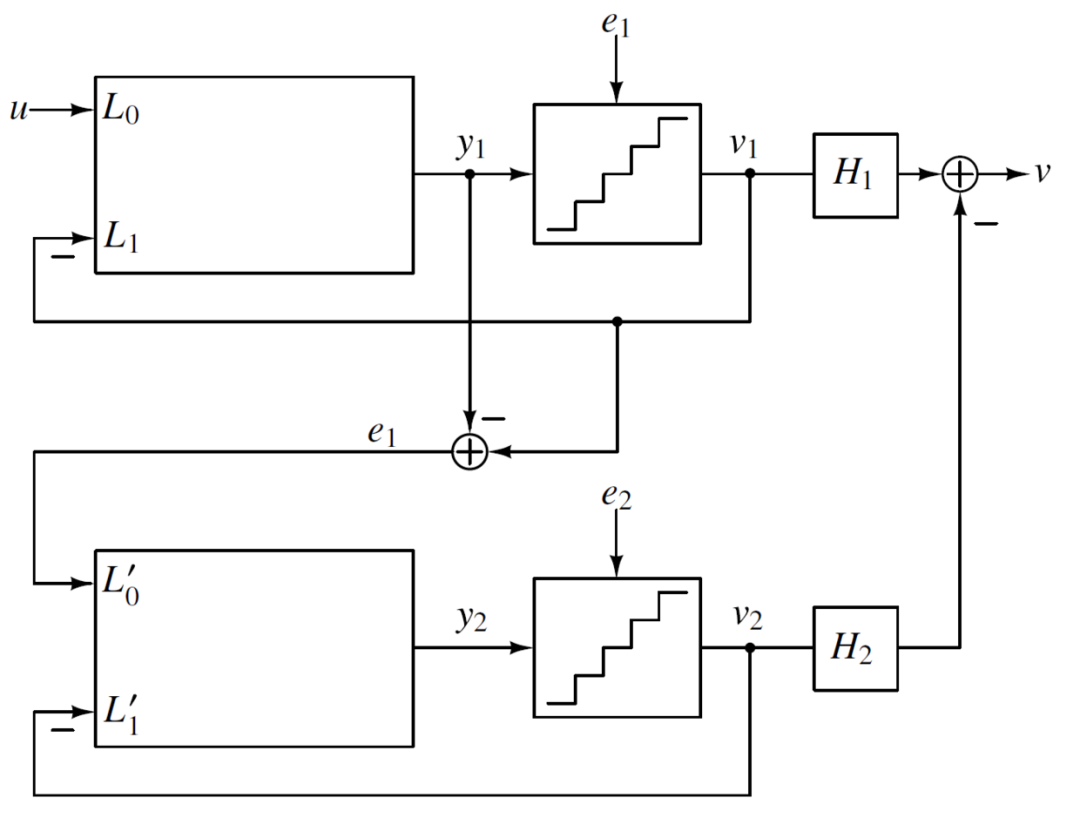

為了進一步提高分辨率,可以考慮將一階結(jié)構(gòu)的量化器用一個一階Σ-Δ調(diào)制器替代,如下圖所示:

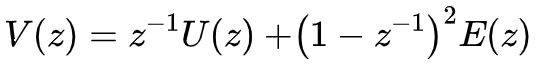

此時,輸出V的表達式為:

此時,輸出V的表達式為:

從該式可以看出,現(xiàn)在的噪聲整形傳函為二階,應(yīng)該可以得到更好的噪聲整形效果。同理可得此時的帶內(nèi)量化噪聲為:

此時,OSR增加一倍,量化噪聲減小15dB,也就是ENOB增加2.5bit,表現(xiàn)出更好的噪聲整形效果。#### 高階Σ-Δ調(diào)制器

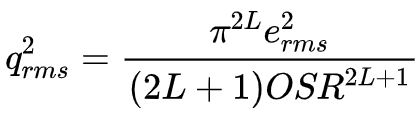

我們可以將上述結(jié)構(gòu)進行推廣到L階,帶內(nèi)噪聲功率表達式為:

此時,當OSR增加一倍,ENOR增加(L+0.5)bit。那么我們可以一直將階數(shù)增加下去,以至實現(xiàn)一個非常好的SQNR性能的ADC嗎?

當然是不可能的,高階環(huán)路會引入穩(wěn)定性問題,后續(xù)文章會介紹這一問題。

多級噪聲整形結(jié)構(gòu)(MASH)

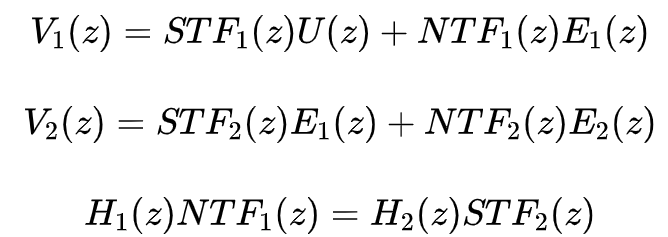

由于多級Σ-Δ結(jié)構(gòu)會有穩(wěn)定性問題,可以考慮將多個低階結(jié)構(gòu)進行級聯(lián),該結(jié)構(gòu)的穩(wěn)定性由低階環(huán)路決定,而實現(xiàn)的噪聲整形特性卻是高階的。如下圖所示,這是一個兩級結(jié)構(gòu)級聯(lián)的MASH結(jié)構(gòu),將第一級的量化噪聲送入到第二級結(jié)構(gòu)的信號輸入端,并將兩級各自的輸出經(jīng)過一定處理后疊加。如果每一級都是一個兩級的Σ-Δ調(diào)制器,那么該MASH結(jié)構(gòu)實現(xiàn)了一個四階噪聲整形效果。如下式所示,V1和V2疊加時要將第一級的量化噪聲抵消掉:

這個結(jié)構(gòu)看似完美,解決了高階環(huán)路的穩(wěn)定性問題,而又實現(xiàn)了高階噪聲整形效果,但是由于需要實現(xiàn)兩式相消,所以它們之間的匹配性成為了很重要一個問題。

多比特Σ-Δ調(diào)制器

我們將前述的Σ-Δ結(jié)構(gòu)進一步具體化,如下圖所示。用一個ADC來表示量化器。之前的結(jié)構(gòu)將量化器輸出直接反饋回去和輸入的模擬信號相減,我們不可能將模擬信號和數(shù)字信號直接進行運算,量化輸出結(jié)果在反饋到輸入端之前首先需要D/A變換。

為什么要引入多比特結(jié)構(gòu)呢?

比特數(shù)越多的量化器的量化噪聲越小,因此在同樣階數(shù),同樣OSR的情況下,可以實現(xiàn)更高的SQNR。

單比特的ADC的增益因子不好確定(后續(xù)文章展開),因此在考慮穩(wěn)定性時,為保證環(huán)路增益變化的情況下,環(huán)路依然穩(wěn)定,輸入信號幅度需要減小,這降低了SNR。

DAC的非線性會導(dǎo)致調(diào)制器輸出的非線性。這是由于反饋增益的存在會使DAC的輸出等于輸入信號u,因此當DAC存在非線性時,DAC的輸入便會失真,以使其輸出等于輸入信號u。

對于一個單比特的DAC,則不存在非線性問題,因為其輸出只有兩個電平。類似兩點確定一條直線的思想,單比特不存在非線性。但是,正如前文所述,量化器采用多比特的ADC具有很大的優(yōu)勢,DAC的位數(shù)應(yīng)該匹配ADC的位數(shù),因此,DAC的非線性還是我們需要解決的一個問題。Trim手段或者Σ-Δ DAC均可以有效解決這個問題。

小結(jié)

本文從時域和頻域分別闡述了Σ-Δ ADC可以提高SNR的原因,過采樣和噪聲整形是Σ-Δ ADC的核心思想,理解了它們,意味著我們窺見了其復(fù)雜內(nèi)涵的一角。為了提高其SNR,可以通過提高OSR、環(huán)路階數(shù)或者量化器的比特數(shù)來實現(xiàn),但是OSR的提高受限于工作帶寬,階數(shù)受限于穩(wěn)定性,采用高比特的量化器則增加了ADC和DAC的設(shè)計難度。此外,還介紹了多級噪聲整形技術(shù),它解決了穩(wěn)定性的問題,卻又引入電路匹配的問題。從以上我們可以再次看到模擬電路設(shè)計的trade-off,這也正是模擬電路的魅力所在。

-

調(diào)制解調(diào)器

+關(guān)注

關(guān)注

3文章

873瀏覽量

39470 -

SNR

+關(guān)注

關(guān)注

3文章

197瀏覽量

24887 -

ADC轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

28瀏覽量

8484 -

累加器

+關(guān)注

關(guān)注

0文章

50瀏覽量

9643 -

射頻系統(tǒng)

+關(guān)注

關(guān)注

0文章

124瀏覽量

13526

發(fā)布評論請先 登錄

EMC中時域和頻域的簡介

射頻 - 時域與頻域的轉(zhuǎn)換

頻譜分析儀R3131可以將波形從頻域轉(zhuǎn)換到時域嗎?

什么是時域和頻域?

基于MATLAB的時域和頻域抽樣計算

從時域、頻域講解OFDMA的原理

深度解析頻域和時域的關(guān)系

什么是頻域分析?頻域和時域有什么關(guān)系?

信號分析:搞懂時域與頻域的關(guān)系

從時域和頻域闡述Σ-Δ ADC提高SNR的原因

從時域和頻域闡述Σ-Δ ADC提高SNR的原因

評論