λ:

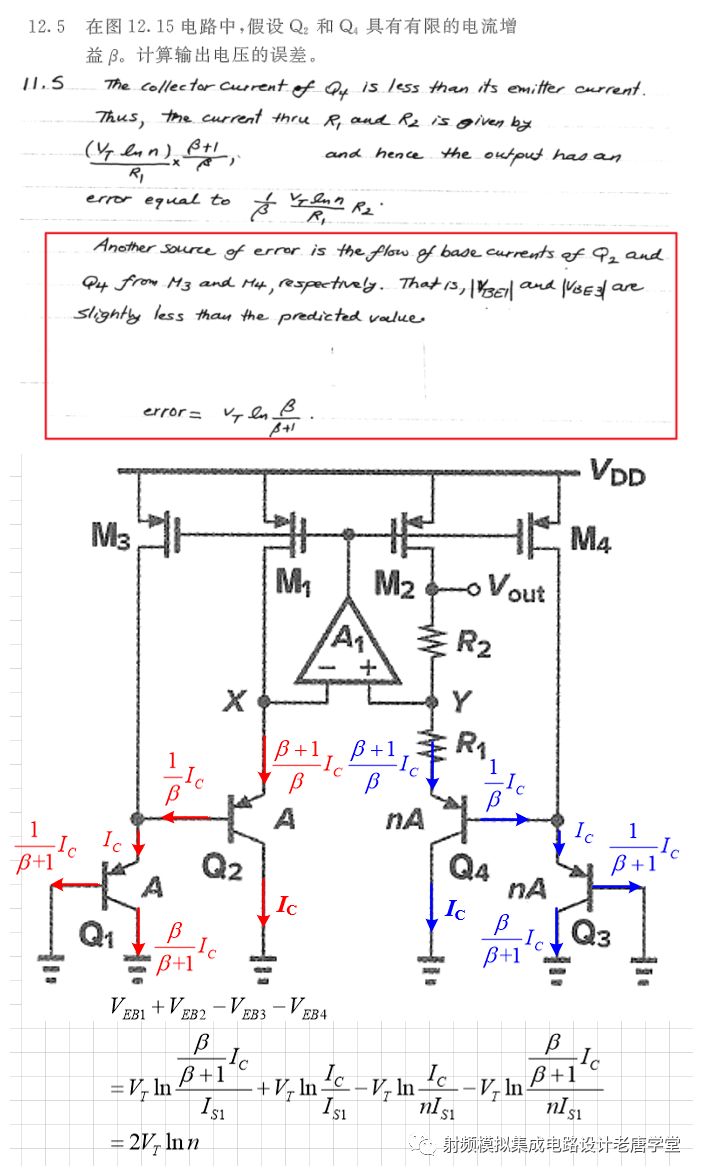

λ:想問一下,拉扎維第二版的習(xí)題12.5。

解答中的第二步,考慮Q2、Q4的基極電流減小了Q1、Q3中的電流,導(dǎo)致VEB1和VEB3有所減小,從而造成了誤差

我覺得這個(gè)誤差是可以彼此消掉的,所以第二步中Q2、Q4的基極電流造成的error應(yīng)該為0

不知道這樣想對(duì)不對(duì)?

唐長文:你的推導(dǎo)只是證明了有限電流增益Beta不會(huì)影響電阻R1上的電壓。

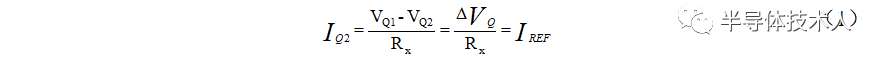

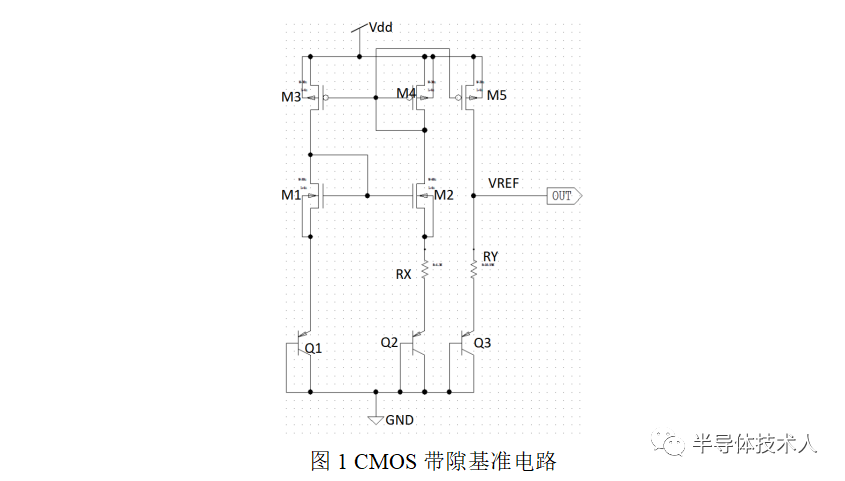

第一個(gè)誤差來源于Q2和Q4的有限電流增益Beta造成的R2電流的變化。如果Q2和Q4的集極電流IC保持不變,無限電流增益時(shí),流過電阻R1和R2的電流為IC;有限電流增益時(shí),流過電阻R1和R2的電流為IC*(Beta+1)/Beta。輸出電壓誤差為(2VT*ln(n)/Beta)*R2/R1。

第二誤差來源于Q2和Q4的有限電流增益Beta造成Q1的VBE的變化。無限電流增益時(shí),VBE1=VT*ln(IC/IS);有限電流增益時(shí),VBE1=VT*ln(IC*Beta/(Beta+1)/IS)=VT*ln(IC/IS)+VT*ln(Beta/(Beta+1))。輸出電壓誤差為VT*ln(Beta/(Beta+1))。

上述只是根據(jù)參考答案給出的解釋。

我也還是有些疑惑,第一、假設(shè)了IC在兩種情況下保持不變,這視乎不合理;第二、能否給出電流增益Beta無限和有限兩種情況下的輸出電壓的表達(dá)式,如果能夠給出,直接相減就能夠得到準(zhǔn)確的電壓誤差表達(dá)式。

-

輸出電壓

+關(guān)注

關(guān)注

2文章

1118瀏覽量

38178 -

帶隙基準(zhǔn)電路

+關(guān)注

關(guān)注

0文章

14瀏覽量

10754

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于LDO穩(wěn)壓器的帶隙基準(zhǔn)電壓源設(shè)計(jì)

求一種低溫漂輸出可調(diào)帶隙基準(zhǔn)電壓源的設(shè)計(jì)方案

帶隙基準(zhǔn)是什么?帶隙基準(zhǔn)的結(jié)構(gòu)是由哪些部分組成的?

電源電壓變化時(shí),帶隙基準(zhǔn)的輸出發(fā)生跳變,怎么減小帶隙基準(zhǔn)的過沖?

基于BiCMOS工藝的帶隙基準(zhǔn)電壓源設(shè)計(jì)

一種高精度BiCMOS帶隙電壓基準(zhǔn)源的設(shè)計(jì)

基于汽車環(huán)境的帶隙基準(zhǔn)電壓源的設(shè)計(jì)

14位Pipeline ADC設(shè)計(jì)的帶隙電壓基準(zhǔn)源技術(shù)

CMOS帶隙基準(zhǔn)電壓源曲率校正方法

一種高PSR帶隙基準(zhǔn)源的實(shí)現(xiàn)

帶隙基準(zhǔn)電壓源及過溫保護(hù)電路

cmos帶隙基準(zhǔn)電壓源設(shè)計(jì)

帶隙基準(zhǔn)是什么_帶隙基準(zhǔn)電路的優(yōu)點(diǎn)

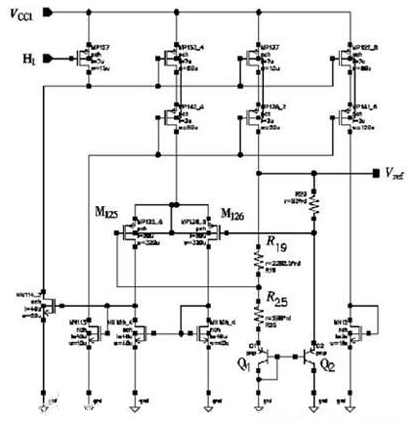

帶隙基準(zhǔn)輸出電壓誤差之解惑

帶隙基準(zhǔn)輸出電壓誤差之解惑

評(píng)論