摘要

在涉及射頻(RF)的硬件測(cè)試中,選擇可配置、已校準(zhǔn)的可靠信號(hào)源是其中最重要的方面之一。本文提供了基于Raspberry Pi的高度集成解決方案,其可用于合成RF信號(hào)發(fā)生器,輸出DC至5.5 GHz的單一頻率信號(hào),輸出功率范圍為0 dBm至-40 dBm。所提出的系統(tǒng)基于直接數(shù)字頻率合成(DDS)架構(gòu),并對(duì)其輸出功率與頻率特性進(jìn)行了校準(zhǔn),可確保在整個(gè)工作頻率范圍中,輸出功率保持在所需功率水平的±0.5 dB以內(nèi)。

簡(jiǎn)介

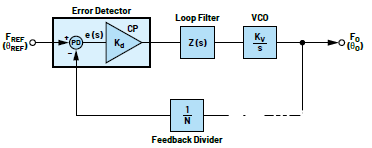

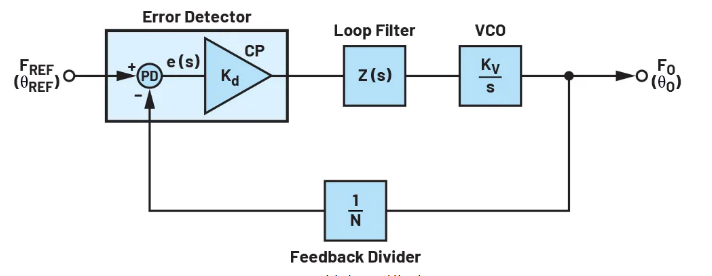

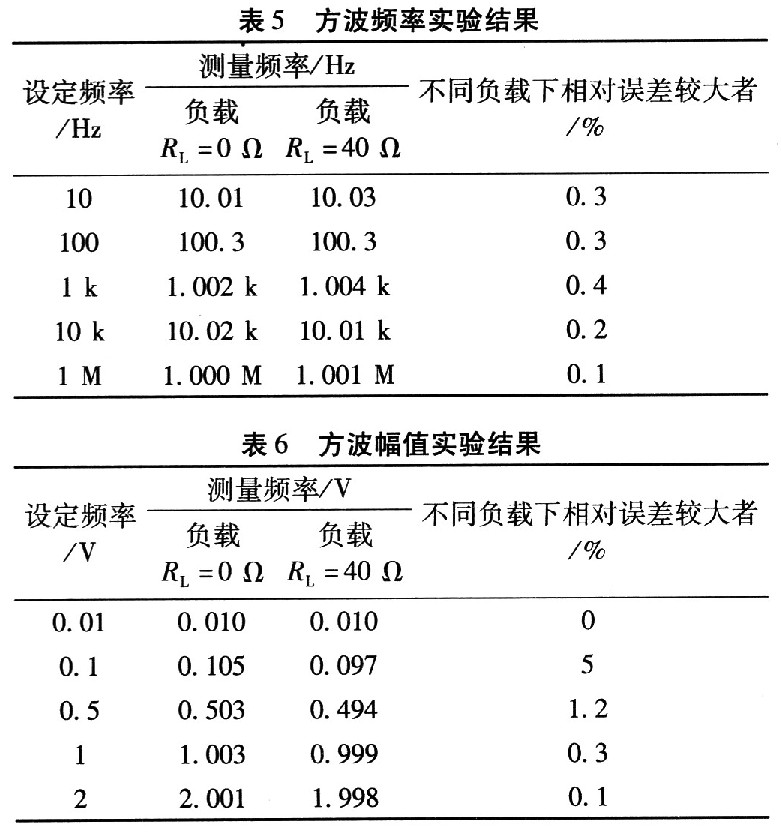

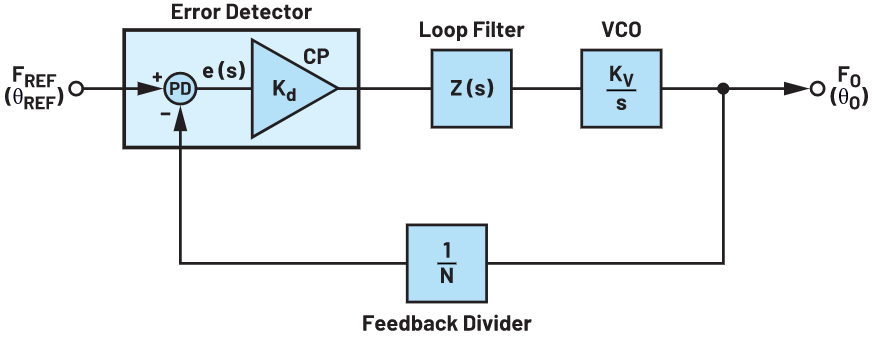

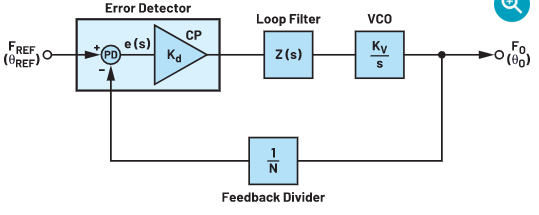

RF信號(hào)發(fā)生器,尤其是微波頻率的RF信號(hào)發(fā)生器,以前通常是基于鎖相環(huán)(PLL)頻率合成器1來(lái)構(gòu)建。PLL支持從低頻參考信號(hào)生成穩(wěn)定的高頻信號(hào)。圖1顯示了一個(gè)基本PLL模型。該模型由反饋系統(tǒng)(其中包括一個(gè)包括一個(gè)電壓控制振蕩器(VCO)用于改變輸出頻率)、誤差檢測(cè)器(用于比較輸入?yún)⒖碱l率和輸出頻率)以及分頻器組成。當(dāng)分頻器的輸出頻率和相位等于輸入?yún)⒖嫉念l率和相位時(shí),環(huán)路被認(rèn)為處于鎖定狀態(tài)。2–5

圖1.基本PLL模型

根據(jù)應(yīng)用的不同,DDS架構(gòu)作為頻率合成器可能比PLL提供了一種更好的替代方案。。圖2顯示了一個(gè)典型的基于DDS的信號(hào)發(fā)生器。調(diào)諧字應(yīng)用于相位累加器,由后者確定輸出斜坡的斜率。累加器的高位經(jīng)過(guò)幅度正弦轉(zhuǎn)換器,最終到達(dá)DAC。與PLL相比,DDS的架構(gòu)具有明顯的優(yōu)勢(shì)。例如,DDS數(shù)字相位累加器可實(shí)現(xiàn)比基于PLL的頻率合成器更精細(xì)的輸出頻率調(diào)諧分辨率。

圖2.基于DDS的典型信號(hào)發(fā)生器

PLL切換時(shí)間是其反饋環(huán)路建立時(shí)間和VCO響應(yīng)時(shí)間的函數(shù),由于自身性質(zhì)的限制,其速度較慢,而DDS僅受數(shù)字處理延遲的限制,因此具有更快的切換速度。在電路板尺寸方面,DDS的面積更小,便于系統(tǒng)設(shè)計(jì),許多硬件RF設(shè)計(jì)難題也迎刃而解6。

下一部分將討論CN0511。一款基于DDS架構(gòu)的完整DC至5.5 GHz正弦波信號(hào)發(fā)生器的總體系統(tǒng)設(shè)計(jì)。接下來(lái)將討論矢量信號(hào)發(fā)生器架構(gòu)及其規(guī)格。而后將重點(diǎn)討論系統(tǒng)時(shí)鐘,包括時(shí)鐘參考要求以及時(shí)鐘管理單元和矢量信號(hào)發(fā)生器之間的電路連接。也會(huì)涉及電源架構(gòu)和系統(tǒng)布局,并進(jìn)一步說(shuō)明整體系統(tǒng)如何實(shí)現(xiàn)高功率效率和合理的散熱性能。隨后的“軟件架構(gòu)和校準(zhǔn)”部分將圍繞系統(tǒng)軟件控制和校準(zhǔn)展開討論。該部分將解釋軟件提供的靈活控制以及如何校準(zhǔn)輸出功率。最后一部分將說(shuō)明整體系統(tǒng)性能,包括系統(tǒng)相位噪聲、校準(zhǔn)輸出功率和系統(tǒng)的熱性能。

系統(tǒng)級(jí)架構(gòu)和設(shè)計(jì)考量

A:系統(tǒng)級(jí)設(shè)計(jì)

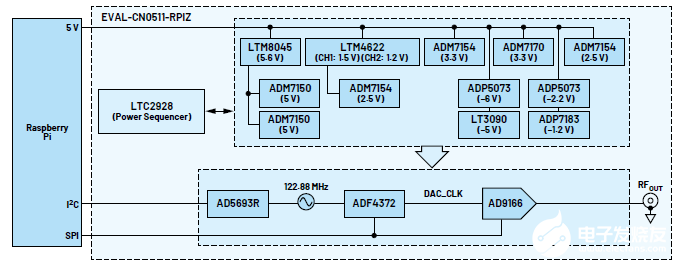

圖3所示系統(tǒng)是基于DDS架構(gòu)的完整DC至5.5 GHz正弦波信號(hào)發(fā)生器。四開關(guān)DAC核心和集成輸出放大器在整個(gè)工作頻率范圍內(nèi)提供極低的失真,并配有50Ω的輸出匹配終端。

板載時(shí)鐘解決方案包括參考振蕩器和PLL,因而無(wú)需外部時(shí)鐘源。所有電源均來(lái)自Raspberry Pi平臺(tái)板,其具有超高電源抑制比(PSRR)穩(wěn)壓器和無(wú)源濾波功能,可使大幅減小電源轉(zhuǎn)換器對(duì)RF性能的影響。

圖3.CN0511:基于RPI的頻率合成RF信號(hào)發(fā)生器

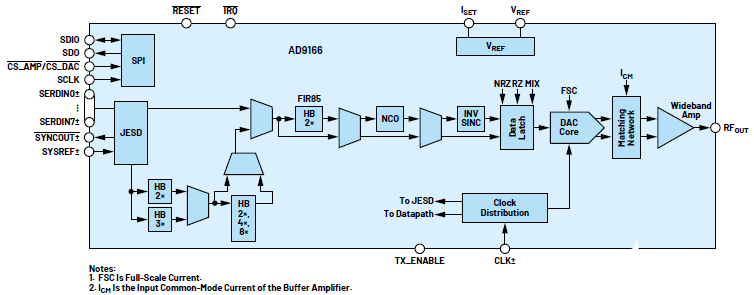

圖4.所用矢量信號(hào)發(fā)生器(AD9166)的功能框圖

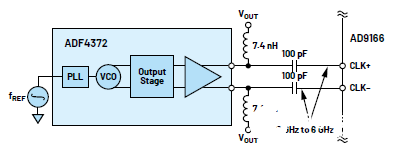

圖5.ADF4372 RF8x輸出級(jí)

圖3所示架構(gòu)可用于雷達(dá)、自動(dòng)測(cè)試、任意波形發(fā)生器和單音信號(hào)發(fā)生器等各種應(yīng)用。而本文中實(shí)現(xiàn)了單音信號(hào)發(fā)生器應(yīng)用。以下小節(jié)將討論CN0511包含的主要集成器件。

B:矢量信號(hào)發(fā)生器

如圖4所示,所使用的DC至9 GHz矢量信號(hào)發(fā)生器包含一個(gè)6 GSPS(1倍不歸零模式)DAC、8通道、12.5 Gbps JESD204B數(shù)據(jù)接口以及一個(gè)具有多個(gè)數(shù)控振蕩器(NCO)的DDS。同時(shí)該器件是高度可配置的數(shù)字?jǐn)?shù)據(jù)路徑,包括插值濾波器、反SINC補(bǔ)償和數(shù)字混頻器,支持靈活的頻譜規(guī)劃。

圖4所示系統(tǒng)利用DAC的48位可編程模數(shù)NCO以非常高的精度(43 μHz頻率分辨率)實(shí)現(xiàn)了信號(hào)的數(shù)字頻移。該DAC的NCO僅需要SPI寫入接口速度達(dá)到100 MHz即可快速更新頻率調(diào)諧字(FTW)。SPI還支持配置和監(jiān)控該DAC中的各種功能模塊。本設(shè)計(jì)未使用JESD通道,器件僅在NCO模式下使用。

圖4中的矢量信號(hào)發(fā)生器集成了單端、50 Ω匹配的輸出RF放大器,因此無(wú)需采用復(fù)雜的RF輸出電路接口。表1顯示了AD9166的主要規(guī)格和在各種條件下的性能。

表1.AD9166主要規(guī)格

| 參數(shù) | 值 | 條件 |

| 頻帶平坦度 | DC至9 GHz | |

| SFDR | –83 dBc | 51 MHz信號(hào)音 |

| -66 dBc | 451 MHz信號(hào)音 | |

| -38 dBc | 4051 MHz信號(hào)音 | |

| 功耗 | ~4 W | 5000 MHz信號(hào)音 |

| 相位噪聲 | -134.8 dBc/Hz | 3600 MHz信號(hào)音;10 kHz偏移 |

| 封裝 |

324引腳BGA (15 mm × 15 mm) |

C:系統(tǒng)時(shí)鐘

圖2中的系統(tǒng)使用了ADF4372 PLL(見圖5),這是一款集成VCO的寬帶頻率合成器,當(dāng)與外部環(huán)路濾波器和外部參考頻率一起使用時(shí),可以作為小數(shù)N分頻或整數(shù)N分頻頻率合成器。此外,VCO頻率可進(jìn)行1、2、4、8、16、32或64分頻,因此用戶可以在RF8x產(chǎn)生低至62.5 MHz的RF輸出頻率。

時(shí)鐘源的質(zhì)量(例如其相位噪聲和雜散特性)以及其與高速DAC時(shí)鐘輸入的接口,會(huì)直接影響交流性能。因此,相位噪聲和其他頻譜內(nèi)容將會(huì)被直接調(diào)制到輸出信號(hào)上。為實(shí)現(xiàn)最佳整數(shù)邊界雜散和相位噪聲性能,ADF4372使用了單端參考輸入信號(hào),然后將其倍頻以產(chǎn)生用于高速DAC的時(shí)鐘,如圖6所示。

圖6.ADF4372和AD9166之間的電路連接

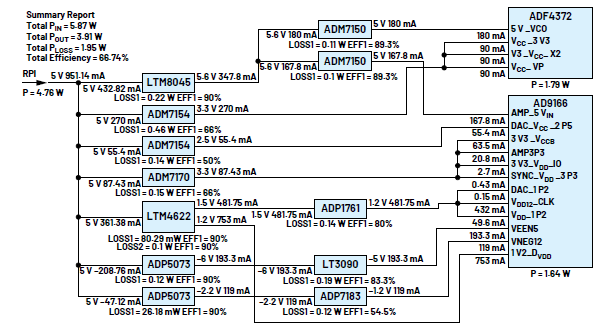

D:電源架構(gòu)

CN0511的系統(tǒng)電源樹如圖7所示,基于系統(tǒng)負(fù)載要求將其效率提高到90%,分別使用了LTM8045、LTM4622和ADP5073開關(guān)穩(wěn)壓器,。并選用ADM7150、ADM7154和ADP1761等低壓差線性穩(wěn)壓器(LDO)來(lái)為DAC、放大器、PLL和VCO供電,其有超低噪聲和高PSRR性能,可實(shí)現(xiàn)最佳相位噪聲性能。

使用電源時(shí)序控制器LTC2928來(lái)確保高速DAC按正確順序上電,避免損壞其內(nèi)部電路。該電源時(shí)序控制器IC可監(jiān)測(cè)和管理四個(gè)電壓軌,并具有控制各電壓軌的上電時(shí)間和其他監(jiān)控功能,其中包括欠壓和過(guò)壓監(jiān)控與報(bào)告功能。

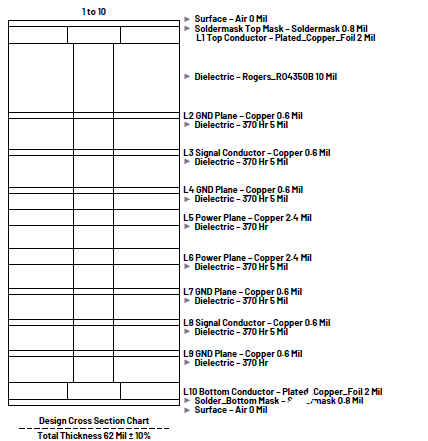

E:布局考慮

對(duì)于這種需要極高性能和較高輸出頻率的應(yīng)用,PCB(印刷電路板)材料的選擇會(huì)對(duì)結(jié)果有很大影響。圖8顯示了推薦的CN0511 PCB疊層,它在包含RF走線的層上使用Rogers 4350電介質(zhì)材料,最大程度上減少3GHz以上的信號(hào)衰減,并確保在RF輸出處獲得最佳的信號(hào)完整性。

圖8.推薦的PCB橫截面和疊層

熱性能與PCB設(shè)計(jì)和工作環(huán)境直接相關(guān)。為改善設(shè)計(jì)的散熱性能,在PCB散熱焊盤上打了散熱通孔。

圖7.系統(tǒng)電源樹

軟件架構(gòu)和校準(zhǔn)

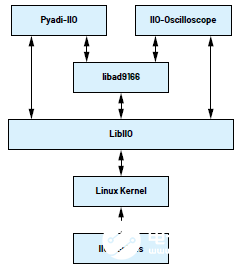

A:軟件控制

在任何涉及信號(hào)發(fā)生器的應(yīng)用都希望能夠輕松靈活地控制儀器設(shè)備。因?yàn)樗恍枰獙⒁粡垘в蠯uiper Linux鏡像的SD卡插入Raspberry Pi,因而可以認(rèn)為CN0511是即插即用的。Kuiper Linux鏡像包含控制信號(hào)發(fā)生器所需的所有必要軟件。有兩種方法可改變輸出功率和頻率:使用PyADI-IIO模塊寫入代碼,或使用IIO-Oscilloscope圖形用戶界面(GUI)輸入所需的輸出。

PyADI-IIO是ADI硬件的Python抽象模塊,帶有工業(yè)輸入/輸出(IIO)驅(qū)動(dòng)程序。此模塊為控制硬件提供了簡(jiǎn)單易用的Python方法和屬性。通過(guò)非常簡(jiǎn)單的Python代碼行即可控制該板,這些代碼可以在本地或遠(yuǎn)程運(yùn)行。可以使用簡(jiǎn)單的for循環(huán)和一些延遲來(lái)創(chuàng)建任何頻率掃描,用于測(cè)試其他設(shè)備。

IIO-Oscilloscope是一個(gè)跨平臺(tái)GUI應(yīng)用程序,需要用戶輸入輸出功率幅度和頻率作為參數(shù)。

PyADI-IIO和IIO-Oscilloscope這兩個(gè)模塊均提供了結(jié)溫傳感器的輸出:一個(gè)在PLL IC內(nèi),另一個(gè)在矢量信號(hào)發(fā)生器IC內(nèi)。圖9展示了這兩個(gè)軟件模塊以及與CN0511板通信所需的其他組件(libAD9166、LibIIO和Linux內(nèi)核)。圖9中顯示的libAD9166是在Kuiper鏡像上預(yù)裝的另一個(gè)庫(kù),用于準(zhǔn)確控制輸出功率,包含輸出校準(zhǔn)功率所需的C++代碼,并特定使用于該板。關(guān)于如何實(shí)現(xiàn)校準(zhǔn)的理論將在B節(jié):輸出功率校準(zhǔn)中繼續(xù)討論。

圖9.通過(guò)PyADI-IIO和IIO-Oscilloscope與設(shè)備通信所需的軟件組件框圖

B:輸出功率校準(zhǔn)

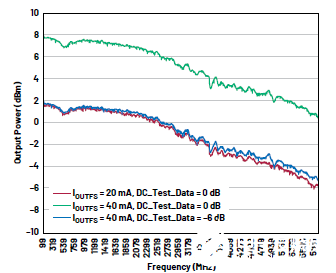

在信號(hào)發(fā)生器應(yīng)用中,頻帶平坦度是一個(gè)關(guān)鍵參數(shù)。在該系統(tǒng)中,輸出功率與頻率的關(guān)系特性主要由矢量信號(hào)發(fā)生器的輸出決定。隨著頻率提高,輸出阻抗從其直流值開始減小。輸出阻抗的這種變化以及負(fù)載處的任何阻抗失配都會(huì)直接影響輸出功率。此外,可預(yù)測(cè)的sinc滾降也會(huì)影響輸出功率的頻率響應(yīng)。圖10討論并顯示了測(cè)得的未校準(zhǔn)輸出功率與頻率的關(guān)系。為了克服這些不利因素,我們對(duì)輸出功率與頻率的關(guān)系進(jìn)行了軟件校準(zhǔn)。

用于校正輸出功率的旋鈕包含了AD9166的兩個(gè)寄存器:設(shè)置滿量程電流的10位寄存器Ioutfs_reg(地址0x42和0x41)和設(shè)置滿量程電流的16位寄存器Iout_reg(地址0x14E和0x14F)。這兩個(gè)寄存器負(fù)責(zé)控制AD9166 DAC的輸出電流,這也是AD9166放大器的輸入(圖3)。

Ioutfs_reg提供大約10 dBm的輸出功率動(dòng)態(tài)范圍,這是用于調(diào)整圖10所示不必要特性的理想值。

圖10.輸出功率與頻率的關(guān)系:未校準(zhǔn)的輸出功率

從測(cè)量結(jié)果來(lái)看,每個(gè)PCB樣片都顯示出圖10所示的相同形狀特性,只是偏移存在差異。考慮到這一點(diǎn),我們開發(fā)了兩個(gè)校準(zhǔn)例程。第一個(gè)校準(zhǔn)程序只需執(zhí)行一次,用于獲取校準(zhǔn)整個(gè)形狀所需的參數(shù),使其平坦化,;第二個(gè)程序則用于校正不同板之間的偏移誤差,并作為每片板的生產(chǎn)測(cè)試運(yùn)行。兩個(gè)校準(zhǔn)例程均通過(guò)輸出測(cè)量、計(jì)算和基于計(jì)算的寄存器調(diào)整來(lái)完成。

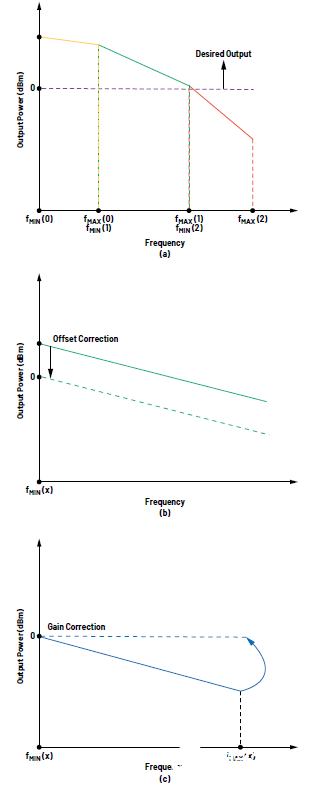

第一個(gè)校準(zhǔn)例程的主要設(shè)計(jì)思路如圖11所示。首先,圖10中的整個(gè)特性曲線被分成多個(gè)頻率區(qū)間,這些區(qū)間可以用從fmin[x]到fmax[x]的線段來(lái)近似表示,其中x是區(qū)間的索引,x ∈ [0, 31],并且x為正整數(shù)。實(shí)際設(shè)計(jì)選擇了31個(gè)區(qū)間,但為了更好地舉例說(shuō)明,圖11a中只顯示了三個(gè)區(qū)間。對(duì)于每個(gè)區(qū)間,需要獲得兩個(gè)常數(shù):一個(gè)是用于偏移校正的Offset_correction(圖11b);一個(gè)是用于增益校正的Gain_correction(圖11c)。還需要存儲(chǔ)參數(shù)fmin[x]以跟蹤區(qū)間。

圖11.校準(zhǔn)例程的可視化舉例:(a) 將特性曲線分成多個(gè)部分;(b) 對(duì)每個(gè)部分進(jìn)行偏移校正;(c) 對(duì)每個(gè)部分進(jìn)行斜率校正。

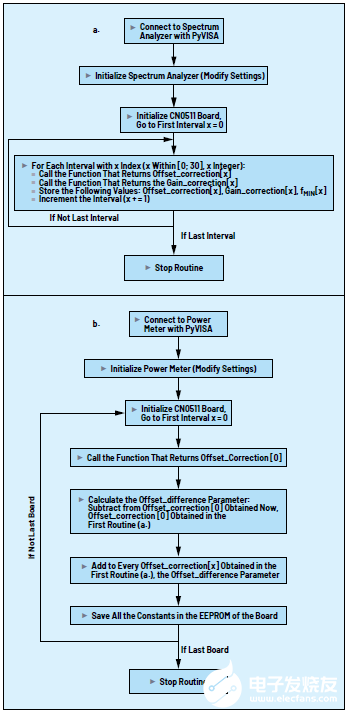

圖12a為第一個(gè)校準(zhǔn)例程的工作原理偽代碼流程圖。為完成此算法,需要使用非常精確的頻譜分析儀來(lái)測(cè)量輸出功率(使用Keysight E5052B/R&S FSUP)。第一個(gè)例程(圖12a)產(chǎn)生的參數(shù)用于第二個(gè)校準(zhǔn)例程,如圖12b所示。

圖12.偽代碼流程圖:(a) 只運(yùn)行一次的第一個(gè)校準(zhǔn)例程;(b) 在每個(gè)CN0511板上運(yùn)行的第二個(gè)校準(zhǔn)例程。

第二個(gè)校準(zhǔn)例程(圖12b)是針對(duì)生產(chǎn)測(cè)試中每個(gè)PCB樣片運(yùn)行的,并為每個(gè)區(qū)間的Offset_correction參數(shù)增加同一常數(shù)。在第二個(gè)例程結(jié)束時(shí),對(duì)于每個(gè)區(qū)間,修改的參數(shù)Offset_correction[x]、Gain_correction[x] 和fmin[x]都將存儲(chǔ)在電路板的EEPROM中。當(dāng)電路板工作時(shí),這些參數(shù)將在軟件中進(jìn)一步使用。

為設(shè)置校準(zhǔn)輸出功率,軟件使用公式1來(lái)計(jì)算調(diào)整頻率fx處的輸出功率的Ioutfs_reg寄存器值,以。fx是區(qū)間x內(nèi)的頻率:fx ∈ [Fmin[x], fmax[x]),fx為實(shí)正數(shù),fmin[x]是索引為x的區(qū)間的最小頻率。

如公式1所示,電路板上必須為每個(gè)x區(qū)間存儲(chǔ)三個(gè)參數(shù),以便進(jìn)行輸出校正:即Offset_correction[x]、Gain_correction[x]和fmin[x]。

系統(tǒng)性能

A:校準(zhǔn)輸出功率

圖13顯示了CN0511在幾種不同輸出功率水平下的寬帶補(bǔ)償頻帶平坦度。對(duì)于設(shè)置在0 dBm和-40 dBm之間的任何輸出功率,從DC到5.5 GHz的整個(gè)頻帶內(nèi)的精度為±0.5 dBm。

圖13.校準(zhǔn)輸出功率與頻率的關(guān)系

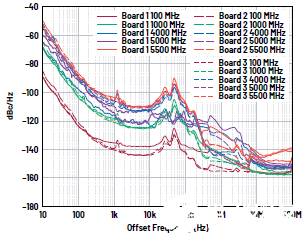

B:相位噪聲

時(shí)鐘源的質(zhì)量以及其與AD9166時(shí)鐘輸入端的接口會(huì)直接影響相位噪聲性能。在指定頻率偏移處的相位噪聲和雜散會(huì)被直接轉(zhuǎn)為輸出信號(hào)。圖14顯示了經(jīng)過(guò)測(cè)量的單邊帶(SSB)相位噪聲與頻率偏移的關(guān)系。所有數(shù)據(jù)都是在輸出功率設(shè)置為滿量程的情況下收集的。使用板載122.88 MHz CMOS壓控晶體振蕩器用作系統(tǒng)時(shí)鐘參考。

圖14.系統(tǒng)相位噪聲性能

C:熱性能

根據(jù)應(yīng)用和配置,高速DAC的功耗可能接近4 W。該器件使用裸露芯片封裝來(lái)降低熱阻并允許芯片直接散熱。使用帶風(fēng)扇的機(jī)械散熱器來(lái)散發(fā)封裝的熱量。在安裝散熱器的情況下,LTM4622在25°C的環(huán)境溫度下顯示出的最高溫度讀數(shù)約為60.6°C。

結(jié)論

本文提出了一種高頻、低失真、低噪聲的信號(hào)源。所介紹的系統(tǒng)是一種采用基于高速DAC的DDS架構(gòu)的低成本RF信號(hào)頻率合成器解決方案,通過(guò)使用基于DDS技術(shù)的矢量信號(hào)發(fā)生器,該系統(tǒng)較之簡(jiǎn)單PLL的有多項(xiàng)優(yōu)勢(shì),例如簡(jiǎn)單化、低失真、高分辨率調(diào)諧、近乎瞬時(shí)的跳頻、相位和幅度調(diào)制。

DDS架構(gòu)的多項(xiàng)優(yōu)勢(shì)使得調(diào)整和校準(zhǔn)輸出功率以及微調(diào)輸出頻率成為可能。在系統(tǒng)中添加校準(zhǔn)例程可為用戶提供從DC到5.5 GHz的輸出參考信號(hào)音,精度為±0.5 dBm,動(dòng)態(tài)范圍為0 dBm到-40 dBm。對(duì)于實(shí)驗(yàn)室儀器而言,這是一種近乎理想的解決方案。

-

DDS

+關(guān)注

關(guān)注

22文章

672瀏覽量

154439 -

信號(hào)發(fā)生器

+關(guān)注

關(guān)注

28文章

1574瀏覽量

110635

發(fā)布評(píng)論請(qǐng)先 登錄

基于Raspberry Pi的合成射頻信號(hào)發(fā)生器的實(shí)現(xiàn)

基于ALTERA實(shí)現(xiàn)的DDS信號(hào)發(fā)生器設(shè)計(jì)

怎么實(shí)現(xiàn)基于FPGA+DDS的正弦信號(hào)發(fā)生器的設(shè)計(jì)?

基于DDS技術(shù)的信號(hào)發(fā)生器研究與實(shí)現(xiàn)策略

微型DDS信號(hào)發(fā)生器

信號(hào)發(fā)生器原理_DDS芯片及應(yīng)用_DDS信號(hào)發(fā)生器設(shè)計(jì)

基于DDS的信號(hào)發(fā)生器設(shè)計(jì)

泰克全新RF信號(hào)發(fā)生器系列敘述

DDS函數(shù)信號(hào)發(fā)生器是什么_DDS函數(shù)信號(hào)發(fā)生器原理及使用方法

DDS函數(shù)信號(hào)發(fā)生器是什么_DDS函數(shù)信號(hào)發(fā)生器簡(jiǎn)單介紹

DDS信號(hào)發(fā)生器的理解與實(shí)現(xiàn)

使用基于Raspberry Pi的DDS信號(hào)發(fā)生器實(shí)現(xiàn)精確RF測(cè)試

使用基于Raspberry Pi的DDS信號(hào)發(fā)生器實(shí)現(xiàn)精確RF測(cè)試

如何使用基于Raspberry Pi的DDS信號(hào)發(fā)生器實(shí)現(xiàn)精確RF測(cè)試

使用基于Raspberry Pi的DDS信號(hào)發(fā)生器實(shí)現(xiàn)精確RF測(cè)試

使用基于Raspberry Pi的DDS信號(hào)發(fā)生器實(shí)現(xiàn)精確RF測(cè)試

評(píng)論