如76059 - Versal ACAP DDRMC - DDR4 和 LPDDR4/x PCB 仿真支持文章中所述,使用 Versal ACAP DDRMC 時,Vivado 會為外部參考時鐘端口自動生成所需 I/O 標準約束。 這些約束可確保輸入參考時鐘搭配所需參考電路使用時,能遵循各數據手冊要求正常運作,并且 PVT 運作期間也同樣如此。

雖然可以為 DDRMC 外部參考時鐘使用其他 I/O 標準和約束組合,但不建議違背這些設計準則要求。 對于此類情境,用戶需查詢 Versal ACAP 數據手冊,了解受支持的 I/O 標準和輸入要求。

此外,受支持的 I/O 標準和 I/O 約束還存在其他限制,需交叉比對《Versal ACAP SelectIO 資源架構手冊》(AM010) 以了解這些限制。 在某些情況下,如不使用 IP 生成的默認設置,將導致與用戶生成的設置產生沖突,而在此情況下唯一的解決途徑是在 Vivado 外部手動修改設計文件中 IP 生成的約束。

解決方法:

當 AXI_NOC 實例配置為包含集成的 DDRMC 時,在每個 DDRMC 的 IP 外部邊界處會出現 1 個 sys_clk 端口。此端口必須連接到一個時鐘源,用戶可在 AXI NoC 配置 GUI 的“DDR Basic”(DDR 基本設置)選項卡上選擇該時鐘源的頻率。“DDR Basic”選項卡還提供了以下三個可用的“System Clock”(系統時鐘)選項以供選擇:“Differential”(差分)、“No Buffer”(無緩沖)或“Internal”(內部)。

“Differential”和“No Buffer”都要求在 DDRMC 使用的三個 XPIO bank 之一中的“Global Clock (GC)”(全局時鐘)輸入管腳上布局差分時鐘源。“Internal”使用 CIPS 中片上生成的內部 HSM1 參考時鐘。 設計中任一或所有 DDRMC 實例都能使用該內部 HSM1 參考時鐘。

外部參考時鐘應保持穩定運行一段時間,然后才能啟動 DDRMC。

外部參考時鐘應持續運行,既不停止也不更改時鐘周期。

外部參考時鐘的 RMS 抖動應少于 3 ps,占空比應為 50/50。

不支持擴展頻譜時鐘設置。

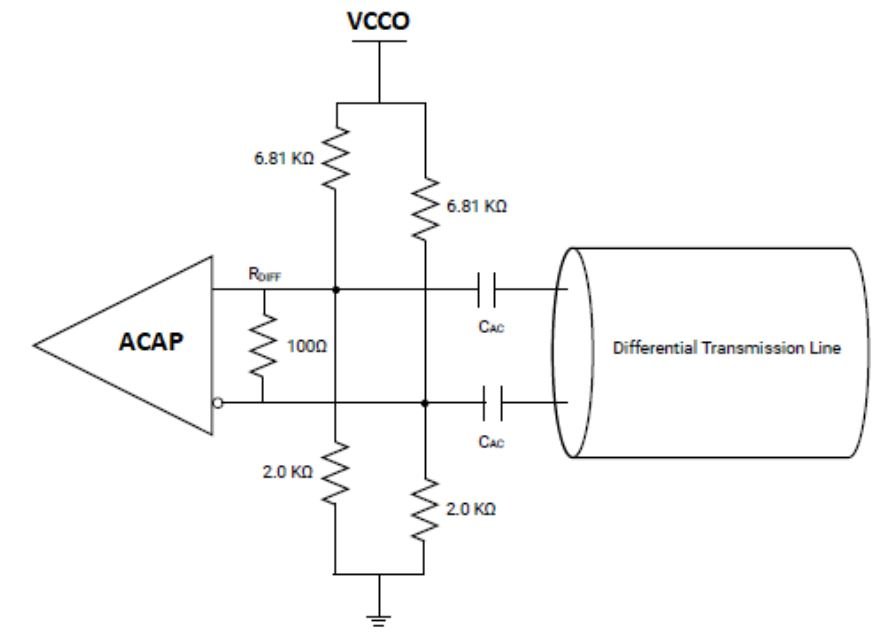

下圖顯示的是使用 DDR4、LPDDR4 或 LPDDR4X 的 Versal ACAP DDRMC 應用所期望的外部參考時鐘偏置電路。

VCCO 將因使用的存儲器技術而異:

DDR4 將使用 1.2 V

LPDDR4 將使用 1.1 V

LPDDR4X 將使用 1.2 V

如需了解 ACAP DDRMC 接口的其他設計要求,請參閱《Versal ACAP PCB 設計用戶指南》(UG863)。

以下列示了 IP 生成的默認 I/O 標準和約束以供參考:

DDR4

LPDDR4

LPDDR4X

如需獲取有關 I/O 標準和 IP 生成的默認約束的更多詳細信息,請參閱76059 - Versal ACAP DDRMC - DDR4 和 LPDDR4/x PCB 仿真支持文章。

審核編輯:湯梓紅

-

仿真

+關注

關注

52文章

4289瀏覽量

135892 -

DDR4

+關注

關注

12文章

333瀏覽量

41757 -

時鐘設計

+關注

關注

0文章

27瀏覽量

11040 -

Versal

+關注

關注

1文章

169瀏覽量

8108

發布評論請先 登錄

新品迅為RK3588-LPDDR5核心板_LPDDR4x與LPDDR5的區別

論手機運行內存 LPDDR 4X在LPDDR4的基礎上有哪些提升

LPDDR4X是什么?LPDDR4X與UFS2.1有什么差別?

lpddr4頻率無法修改怎么解決?

LPDDR4X內存表現亮眼 竟比LPDDR4節能多達40%

使用用戶為 LPDDR4 和 x8 或 x16 DDR4 組件接口指定的 DQS 字節交換生成管腳分配時,其中可能包含錯誤且需更改

LPDDR4是什么意思?LPDDR4X內存是什么意思?

lpddr4x過時了嗎?lpddr4x顯卡怎么樣?電腦LPDDR4X夠用嗎?

lpddr4x和lpddr5區別 lpddr4x和ddr5的區別大不大

DDR4、LPDDR4和LPDDR4x的區別

TPS65296-完整 LPDDR4/LPDDR4X存儲器電源解決方案數據表

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

評論