迷人的技術(shù)革命。

從 2011 年開(kāi)始,英特爾和其他領(lǐng)先的半導(dǎo)體行業(yè)實(shí)現(xiàn)了顯著的技術(shù)轉(zhuǎn)型。該行業(yè)首次開(kāi)始生產(chǎn)三維晶體管——主要稱(chēng)為鰭式場(chǎng)效應(yīng)晶體管(FinFET)。

平面

幾十年來(lái),半導(dǎo)體行業(yè)的構(gòu)建模塊是金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管或 MOSFET。這種晶體管在反相器、與非門(mén)和 SRAM 單元等數(shù)字電路中非常常見(jiàn)。它由位于連接源極和漏極的通道頂部的柵極組成。

源極和漏極基本上只是摻雜有其他元素原子的硅區(qū)域,用于提供或接收電子。兩者之間還有一層薄薄的絕緣層——通常由氧化硅制成。閘門(mén)本身并不穿過(guò)通道。

除了這個(gè)柵極及其絕緣層之外,整個(gè)東西都是平坦的或平面的。該柵極可以允許電子沿著溝道從源極移動(dòng)到漏極。關(guān)閉柵極,電子流動(dòng)停止。

經(jīng)典縮放

在半導(dǎo)體行業(yè)的最初幾十年里,新的工藝節(jié)點(diǎn)只需縮小晶體管的物理尺寸并將更多晶體管塞到芯片上即可實(shí)現(xiàn)性能、功耗和面積增益,這稱(chēng)為經(jīng)典縮放。集成電路工作得更好,因?yàn)殡娦盘?hào)在每個(gè)晶體管之間傳播的距離更短。

正如 IBM 研究人員 Robert Dennard 在 1974 年提出的那樣,第二個(gè)但同樣重要的好處是,這些較小的晶體管也使用更少的功率。摩爾定律推動(dòng)半導(dǎo)體行業(yè)每三年將晶體管的線(xiàn)性尺寸減少一半。20 世紀(jì) 80 年代,尺寸首次降至1微米以下。

泄漏

大約在那個(gè)時(shí)候,人們開(kāi)始注意到他們的晶體管開(kāi)始表現(xiàn)得有點(diǎn)奇怪。隨著晶體管的物理尺寸縮小,源極和漏極變得越來(lái)越靠近。柵極和溝道之間的絕緣層變得更薄,為 1.2 納米或 5 個(gè)原子寬,而且通道本身也變得更細(xì)。

這樣,柵極對(duì)電流從源極到漏極的控制就會(huì)變?nèi)酢H缓蠡旧习l(fā)生的是電流從源極流向漏極時(shí)“潛入柵極下方”。即使閘門(mén)關(guān)閉,電流也可以可以穿過(guò)離柵極最遠(yuǎn)的溝道部分,或者在某些情況下甚至穿過(guò)硅襯底本身。這被稱(chēng)為“短溝道效應(yīng)”,到 20 世紀(jì) 90 年代中期(350 納米工藝節(jié)點(diǎn)),它已成為一個(gè)嚴(yán)重的工業(yè)問(wèn)題。

除了不可預(yù)測(cè)的行為之外,還存在嚴(yán)重的功耗問(wèn)題。這種泄漏意味著這些較小的晶體管不遵循登納德縮放比例。

按照事情的發(fā)展方式,晶體管在“關(guān)閉”狀態(tài)下消耗的能量與“開(kāi)啟”狀態(tài)下消耗的能量一樣多。這是因?yàn)?a href="http://m.xsypw.cn/soft/data/39-96/" target="_blank">消費(fèi)電子產(chǎn)品開(kāi)始變得更加便攜,從而對(duì)電源效率提出了更高的要求。

研究人員很快意識(shí)到他們正在打一場(chǎng)必?cái)≈獭=?jīng)典 MOSFET 結(jié)構(gòu)有一個(gè)最終終點(diǎn),實(shí)際的最終尺寸限制在 20 納米左右。1996 年,憑借 250 納米的領(lǐng)先優(yōu)勢(shì),美國(guó)國(guó)防部高級(jí)研究計(jì)劃局(DARPA)意識(shí)到該行業(yè)沒(méi)有 2002年(5 年后)之后的長(zhǎng)期計(jì)劃。他們呼吁提出有關(guān)25 納米以下器件的研究提案,名為25納米開(kāi)關(guān)。

25納米開(kāi)關(guān)

DARPA 收到了來(lái)自 IBM、AT&T,當(dāng)然還有斯坦福大學(xué)的 10-12 份提案。然而,所有這些都只是原始 MOSFET 結(jié)構(gòu)的延伸。這不是 DARPA 想要的。他們想要一些雄心勃勃且可行的東西。

獲勝者來(lái)自加州大學(xué)伯克利分校胡正明教授領(lǐng)導(dǎo)的團(tuán)隊(duì)。胡教授于 1976 年加入伯克利分校。早期,他研究了混合動(dòng)力汽車(chē)等能源主題。但里根政府上臺(tái)后,美國(guó)政府的資金很快就枯竭了,里根政府轉(zhuǎn)向半導(dǎo)體研究。

1982年,胡先生休假到美國(guó)國(guó)家半導(dǎo)體工作。在那里,他有機(jī)會(huì)從前線(xiàn)看到平面晶體管的終結(jié)。在聽(tīng)說(shuō) DARPA 向伯克利分校的一位教員征集提案后,他召集了一批工作人員,并在一周內(nèi)提出了最終提交的提案。該提案題為“太比特級(jí)電子器件的 25 nm FET 的新穎制造、器件結(jié)構(gòu)和物理原理”,提出了兩個(gè)想法,都集中在讓柵極更好地控制通道本身的想法。

第一種稱(chēng)為全耗盡絕緣體上硅或 FD-SOI。如果電子使用硅基板不適當(dāng)?shù)匾苿?dòng),那么我們會(huì)在硅基板頂部添加一層新的絕緣層以防止這種情況發(fā)生。

FDSOI 取得了一定的成功。業(yè)界已將其用于模擬或電力電子等特定用途。第二個(gè)想法是胡教授在一次長(zhǎng)途飛行中勾勒出來(lái)的——FinFET。

FinFET 崛起

正如前面提到的,重點(diǎn)是讓門(mén)能夠更好地控制通道。

傳統(tǒng)的平面源極、漏極和溝道都是平坦的,大門(mén)位于其頂部。FinFET 將平面源極、漏極和溝道轉(zhuǎn)向一側(cè),使其升起至周?chē)鷧^(qū)域上方,并賦予其 3D 鯊魚(yú)鰭外觀(guān)。然后將門(mén)包裹在通道的頂部和側(cè)面,而不是僅僅坐在通道的頂部。

FinFET 的主要優(yōu)點(diǎn)是它允許柵極在三個(gè)側(cè)面環(huán)繞溝道。相比之下,舊平面晶體管上的柵極僅覆蓋一側(cè)的溝道。此外,F(xiàn)inFET 的物理占用空間也更小。這意味著我們可以繼續(xù)將更多的它們填充到同一塊平面上。

這不是什么新主意了。之前曾提出過(guò)兩個(gè)概念上相似的提案,但這些想法都沒(méi)有被實(shí)施或變成真正的發(fā)明。

第一個(gè)來(lái)自日立公司的研究員 D. Hisamoto。早在 1990 年,他就提出了將柵極包裹在溝道周?chē)⒅谱?3D 晶體管的想法。他的論文將其稱(chēng)為“完全耗盡精益溝道晶體管”或 DELTA。久本則受到德州儀器 (TI) 在 20 世紀(jì) 80 年代發(fā)表的一篇呼吁“溝槽晶體管”的論文的啟發(fā)。

發(fā)明

如果沒(méi)有執(zhí)行,這個(gè)概念就毫無(wú)用處,沒(méi)有人知道這些晶體管是否可以擴(kuò)展到 25 納米或更小的世界。因此,在 DARPA 的資金支持下,胡先生和他的團(tuán)隊(duì)花了四年時(shí)間制作了一個(gè)可工作的 FinFET 器件的原型。

至關(guān)重要的是,該團(tuán)隊(duì)可以自由地追求這一長(zhǎng)期目標(biāo),但也有能力利用私營(yíng)和公共部門(mén)的不尋常資源。這包括斯坦福大學(xué)和勞倫斯伯克利國(guó)家實(shí)驗(yàn)室的設(shè)備和設(shè)施。

2001年,DARPA項(xiàng)目進(jìn)入尾聲,胡的團(tuán)隊(duì)公布了他們的研究結(jié)果。人們很快意識(shí)到 FinFET 是一項(xiàng)巨大的創(chuàng)新技術(shù)。但同樣重要的是,F(xiàn)inFET 并沒(méi)有太大的破壞性。該團(tuán)隊(duì)確保仍然可以使用傳統(tǒng)的光刻和蝕刻工具來(lái)制造它。

這樣,半導(dǎo)體行業(yè)就可以獲得其想要的更好的性能和功效,而無(wú)需放棄數(shù)十億美元的設(shè)備和數(shù)十年的經(jīng)驗(yàn)。

應(yīng)變工程

即便如此,半導(dǎo)體行業(yè)仍然是一個(gè)保守的行業(yè)。FinFET 發(fā)布后,他們并沒(méi)有立即采用,而是選擇了短期措施來(lái)避免 MOSFET 的末日。

對(duì)于 2000 年代初的 90 至 45 納米節(jié)點(diǎn),業(yè)界采用了基于應(yīng)變或應(yīng)力的工程。在這里可以將“應(yīng)變”硅層添加到通道中,通常位于硅-鍺緩沖層的頂部。

應(yīng)變,意味著硅的晶體原子層被拉伸。這有助于提高電子穿過(guò)通道時(shí)的移動(dòng)速度。這也不容易做到,需要工程師使用外延生長(zhǎng)這些應(yīng)變硅層。

高K金屬柵極

然后,在 2009 年至 2010 年的 28 納米工藝節(jié)點(diǎn),英特爾及其團(tuán)隊(duì)在其晶體管中實(shí)施了一種新型柵極。這被稱(chēng)為高 K 金屬柵極。

還記得柵極和溝道之間有一層二氧化硅絕緣層嗎?對(duì)于高 K 金屬柵極,我們用氧化鉿等高 K 金屬制成的一層取代了二氧化硅層。這種高 K 值(相對(duì)于傳統(tǒng)二氧化硅而言較高)使相反的電荷在其所屬位置彼此分開(kāi)。

這個(gè)概念也不容易實(shí)現(xiàn)。這導(dǎo)致了“Gate First or Gate Last”困境,導(dǎo)致行業(yè)分裂,并使得大量半導(dǎo)體制造商失去了領(lǐng)先優(yōu)勢(shì)。

是時(shí)候轉(zhuǎn)向 3D 了。

三門(mén)

對(duì)于 28 納米(22 納米)之后的下一個(gè)大節(jié)點(diǎn),英特爾選擇實(shí)施一種 3D 設(shè)備,他們稱(chēng)之為三柵晶體管。

Tri-Gate 是原始 FinFET 的后代。最初的裝置在鰭周?chē)膬蓚€(gè)側(cè)壁上各有兩個(gè)柵極,稱(chēng)為雙柵極 FinFET。

隨著時(shí)間的推移,業(yè)界發(fā)現(xiàn)這些選擇不會(huì)產(chǎn)生效果。他們對(duì)其進(jìn)行了修改,以創(chuàng)建英特爾最終交付的產(chǎn)品,鰭的所有三個(gè)暴露側(cè)面上都有三個(gè)柵極層。

因此,三門(mén)形容詞。無(wú)論如何,大多數(shù)人和我一樣將它們稱(chēng)為 FinFET。

過(guò)渡

從原型到批量生產(chǎn)始終充滿(mǎn)挑戰(zhàn)。翅片的幾何形狀(寬度、高度等)以及翅片之間的間距(稱(chēng)為翅片間距)對(duì)其整體性能起著重要作用。這些都非常細(xì)節(jié),在 20 納米或更小的工藝節(jié)點(diǎn)上,鰭片的寬度僅為 10 納米。

鰭片間距約為60納米。數(shù)以百萬(wàn)計(jì)的納米級(jí)翅片的制造必須具有極小的變化。與一系列新的多重圖案技術(shù)同時(shí)出現(xiàn),這是極其困難的。繼英特爾之后,所有代工廠(chǎng)都在努力擴(kuò)大其首款 FinFET 產(chǎn)品的良率,從而導(dǎo)致了延誤。

臺(tái)積電和三星終于在 2013 年憑借他們所謂的 16/14 納米工藝實(shí)現(xiàn)了跨越。GlobalFoundries 于 2014 年加入了自己的 14 納米工藝,他們從三星獲得了工藝許可。

全柵Gate All Around

FinFET 在 N7 和 N5 代中表現(xiàn)良好。但最近這些也正在失去效力。代工廠(chǎng)正在盡一切努力來(lái)提高性能——例如,使鰭越來(lái)越高——但最終需要一套新的架構(gòu)。業(yè)界已決定采用 Gate all around 作為新架構(gòu)。

FinFET 工作得更好,因?yàn)樗臇艠O覆蓋了通道上更多的表面積,以便更好地控制。周?chē)拈T(mén)通過(guò)完全包圍通道,甚至從以前不是的底部,進(jìn)一步推進(jìn)了這個(gè)想法。將柵極完全包裹在通道周?chē)€意味著我們可以在多個(gè)通道(或納米線(xiàn))通過(guò)柵極時(shí)將它們堆疊在一起,很完美。

2022 年 6 月,三星開(kāi)始發(fā)售采用全柵 FET 的 3 納米工藝。臺(tái)積電在其即將推出的 N3 工藝節(jié)點(diǎn)中堅(jiān)持使用 FinFET。但他們將在下一個(gè)重大節(jié)點(diǎn)步驟 N2 中采用 Gate-all-around,該節(jié)點(diǎn)正在寶山建設(shè)中。

結(jié)論

這些 3D 晶體管是一個(gè)技術(shù)奇跡。但它們的價(jià)格并不便宜。FinFET 復(fù)雜的結(jié)構(gòu)增加了成本,這意味著 28 納米(最后一個(gè)平面柵極)是每個(gè)柵極成本停止下降并再次開(kāi)始上升的點(diǎn)。

當(dāng)只能向下蝕刻時(shí),如何在納米線(xiàn)之間建立間隙?該解決方案涉及超晶格和一種稱(chēng)為原子層沉積的新方法。這些新結(jié)構(gòu)使得除了最大的公司之外的所有公司都無(wú)法在經(jīng)濟(jì)上取得領(lǐng)先優(yōu)勢(shì)。在最近的一次采訪(fǎng)中,ASML 的首席技術(shù)官表示,他認(rèn)為我們已經(jīng)到達(dá)了光刻技術(shù)的極限。不是因?yàn)榧夹g(shù),而是因?yàn)榻?jīng)濟(jì)可行性。

-

3D

+關(guān)注

關(guān)注

9文章

2956瀏覽量

110473 -

晶體管

+關(guān)注

關(guān)注

77文章

10004瀏覽量

141183 -

半導(dǎo)體行業(yè)

+關(guān)注

關(guān)注

10文章

403瀏覽量

41079

原文標(biāo)題:3D晶體管的轉(zhuǎn)變

文章出處:【微信號(hào):ICViews,微信公眾號(hào):半導(dǎo)體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ZSKY-D882-SOT-89-3L NPN硅功率晶體管規(guī)格書(shū)

晶體管電路設(shè)計(jì)(下)

下一代3D晶體管技術(shù)突破,半導(dǎo)體行業(yè)迎新曙光!

晶體管電路設(shè)計(jì)與制作

如何測(cè)試晶體管的性能 常見(jiàn)晶體管品牌及其優(yōu)勢(shì)比較

晶體管與場(chǎng)效應(yīng)管的區(qū)別 晶體管的封裝類(lèi)型及其特點(diǎn)

麻省理工學(xué)院研發(fā)全新納米級(jí)3D晶體管,突破性能極限

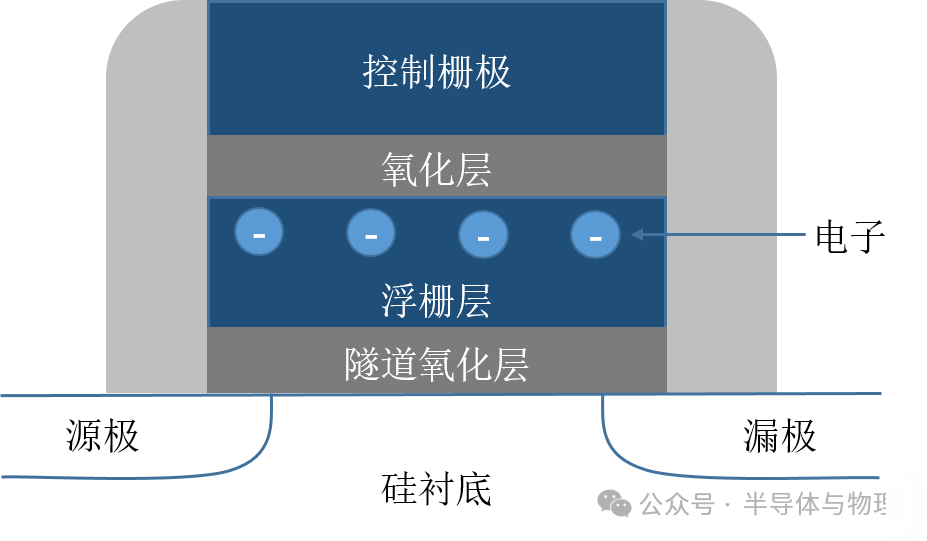

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

晶體管的輸出特性是什么

淺析晶體管光耦產(chǎn)品

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

晶體管處于放大狀態(tài)的條件是什么

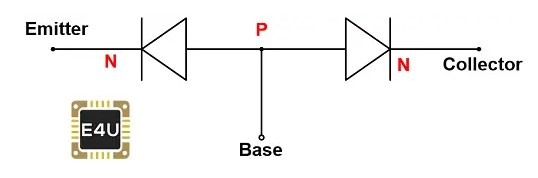

什么是NPN晶體管?NPN晶體管的工作原理和結(jié)構(gòu)

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

3D晶體管的轉(zhuǎn)變

3D晶體管的轉(zhuǎn)變

評(píng)論