我覺得稱時(shí)鐘樹為芯片的大動(dòng)脈一點(diǎn)也不夸張,因?yàn)樗衒lipflop 翻轉(zhuǎn)都要受到它的控制。而時(shí)鐘樹的設(shè)計(jì)到實(shí)現(xiàn)是一個(gè)很復(fù)雜的過程,從流程上說,它牽扯到使用的工具,流程,flow等。從人的角度講,它需要設(shè)計(jì),綜合,dft ,pr, sta 工程師的通力合作。從知識(shí)上講它需要一定的芯片架構(gòu)設(shè)計(jì)知識(shí),一定的綜合,STA 知識(shí),一定的dft知識(shí),包括一定的pr 長(zhǎng)clock tree的知識(shí)。我這里結(jié)合我的個(gè)人有限知識(shí),結(jié)合實(shí)踐經(jīng)歷以及理解對(duì)這些問題做多方面的闡述,難免有缺漏,也是為了拋磚引玉,歡迎同仁討論。集思廣益。

本文所涉及的工具綜合DC, 時(shí)序分析PT, 物理實(shí)現(xiàn)工具innovus.

大家需要什么樣的clocktree呢?

設(shè)計(jì) :我要更少的PLL, (更多的PLL 帶來配值的麻煩,能用各種分頻產(chǎn)生的頻率。盡量用分頻電路產(chǎn)生,能不多加PLL就不要多加。)我要沒有毛刺,PLL jitter抖動(dòng)更小(設(shè)計(jì)上沒有毛刺需要電路結(jié)構(gòu)上的改變 如glitch free mux , PLL jitter需要電路上更給力的模擬單元。)。我要更低的功耗 (設(shè)計(jì)通過powerpro 添加更多的ICG 上去,ICG的效率提上去。盡量不要有組合邏輯clock gating檢查。)

DFT: 我要配值更少的PLL (盡量相同頻率的邏輯用一個(gè)PLL 去拉通,更多的PLL 需要更多的tdr 配值增加面積還帶來不確定性)。我要更少的occ (相同頻率的fanout 盡量墊一個(gè)occ, 更少的occ ,更少的面積,處理起來也更簡(jiǎn)便)

SYN&PR : 我要更精準(zhǔn)的SDC ( 更精準(zhǔn)的SDC 去除更多的假path, 在PR SI 分析上也能過濾掉不該分析的部分,還能指導(dǎo)clocktree的生長(zhǎng) )。我要更好的useful skew (需要flow,分析,try run和調(diào)整,來達(dá)到不平的clock tree 與setup hold 之間微妙的平衡)。我要更長(zhǎng)的common path ,更短的clock tree (長(zhǎng)的common path 更短的clocktree, 可能需要設(shè)計(jì)clock tree結(jié)構(gòu)調(diào)整, sdc 的調(diào)整,ccopt spec 調(diào)整, place 調(diào)整等等)。

我要PLL 的REF CLOCK 走更短的距離 (PLL ref clock 需要高的時(shí)鐘質(zhì)量。提前有好的規(guī)劃,不要插多余的cell到ref clock 路徑上,pr floorplan 的迭代 控制PLL 與ref clock 的距離, 綜合過程不要給這種net上加?xùn)|西。)。我要更小的SI (pr clock tree 布線上更好的布線層規(guī)劃,良好的shielding )。我要tree更好的平衡 (該balance的地方balance,不該balance的地方不要相互拖拽,需要良好的ccopt_spec, sdc ,以及setting配合。)

等等,還有很多,所有的需求都需要相互trade off 來達(dá)到一個(gè)平衡。

我以圖片舉例來挑其中一些問題針對(duì)的談?wù)劇?/p>

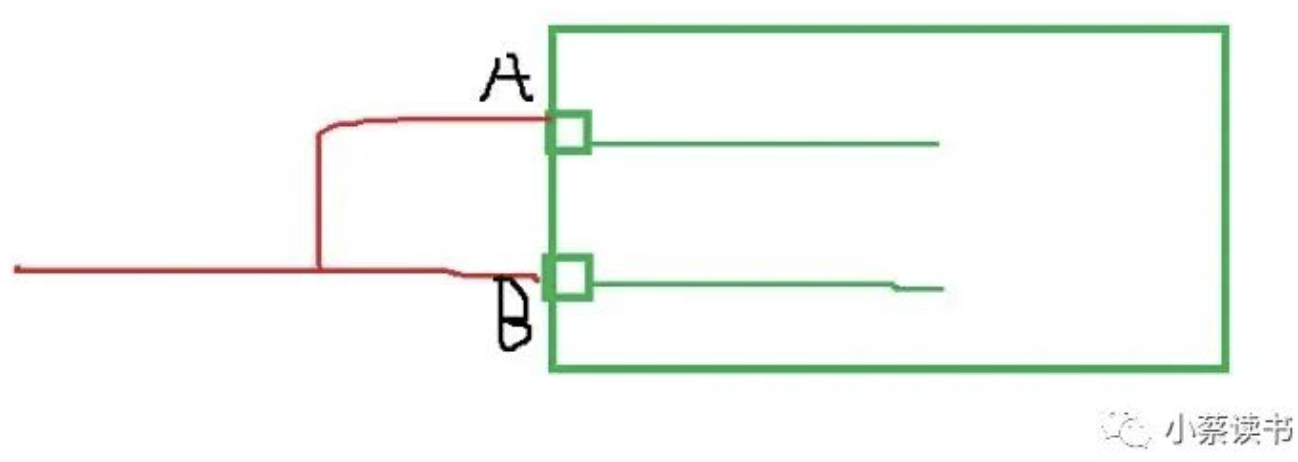

能不要多點(diǎn)長(zhǎng)tree平衡,盡量不要多點(diǎn)長(zhǎng)tree,除非迫不得已。如圖從物理實(shí)現(xiàn)角度說 綠色是一個(gè)block ,A 和B 兩個(gè)clock 從port進(jìn)來需要相互balance。這種結(jié)構(gòu)block的PR工程師好不容易把A 和B 調(diào)的tree平衡。但是到了頂層,頂層pr工程師還需要保證紅色的到A &B兩個(gè)hier pin的tree路線是平衡的。對(duì)時(shí)序收斂是不友好的。

設(shè)計(jì)牽扯到從block穿clock出來到頂層的結(jié)構(gòu)那么紅色的這路去頂層的clock路徑不要帶多余的邏輯,如果有多余的邏輯分配到A 那部分去, 因?yàn)榫G色的地方dft要加occ, 而occ一般是不級(jí)聯(lián)的。

設(shè)計(jì)中驅(qū)動(dòng)兩個(gè)hinst如果是同頻的能用一個(gè)occ (紅色) 就盡量不要用兩個(gè)(綠色)。造成面積浪費(fèi)不說,且如果A和B再有timing talk 會(huì)導(dǎo)致非 common path 變長(zhǎng)。

分頻模塊在功能模式下的分頻系數(shù)頻率與dft 模式下的分頻系數(shù)盡量一致。當(dāng)功能模式時(shí)候toggle fun_reset 就能讓div模塊配置到需要的系數(shù)上。當(dāng)dft模式下toggle dft cgu reset 也能讓div模塊配置到相同的系數(shù)上。否則需要dft通過tdr或者其它連線來配值自己想要的參數(shù),增加多余邏輯。不過具體情況具體分析。沒有通解。

STA 工程師盡量通過良好的使用 set_clock_group -physically_exclusive -logically_exclusive -asyncronus / set_clock_exclusivity 等命令去過濾掉C 位置不應(yīng)該A B共存導(dǎo)致的SI 分析。

多種mode sdc 能merge的盡量merge ,不能merge再具體問題具體分析。多個(gè)mode sdc會(huì)產(chǎn)生更多需要分析的constraint mode 產(chǎn)生更多scenario 耗費(fèi)更多時(shí)間。舉個(gè)例子類似我遇到的這種結(jié)構(gòu)的clock 就是相對(duì)不那么好做的 A B C三個(gè)mux會(huì)從ip上去選clock。而且A B C之間相互還需要balance, 那么就是2 *2 *2 = 8 種可能性。關(guān)鍵是這8種可能性在真實(shí)情況下可能只有5種是真實(shí)會(huì)產(chǎn)生的。

你如果只通過create_clock create_generated_clock set_clock_group set_false_path 方式來做,那么就會(huì)產(chǎn)生過約,因?yàn)闀?huì)額外約束多余那3種可能性,如果我通過給mux sel set_case_analysis 來case的話那么就會(huì)產(chǎn)生更多的sdc mode, 更多的view.事實(shí)上當(dāng)時(shí)這種類似mode有好幾十種情況。

合理的使用set_clock_sense set_sense.應(yīng)用場(chǎng)景有時(shí)會(huì)有個(gè)A clock 高頻clock和B clock 低頻clock 經(jīng)過mux去驅(qū)動(dòng)后面的A INST 與B INST, 真實(shí)情況是可能B clock 只會(huì)打到A INST 模塊進(jìn)行搬運(yùn)數(shù)據(jù), 比如芯片boot階段。它不會(huì)去B INST 那么一定要用set_sense 去把B clock在B INST 前面停掉,這有利于timing分析也有利于PR 進(jìn)行長(zhǎng)clock tree。默認(rèn)情況下innovus create ccopt spec 會(huì)轉(zhuǎn)換 set_sense /set_clock_sense 為 set_ccopt_property -sink_type igore [get_pin xxx] 這樣對(duì)于B clock 來說B INST 里面的sink點(diǎn)就不會(huì)被balance 。去掉不該balance的 sink點(diǎn)自然tree就會(huì)更好。

合理利用useful skew ECF/ccd 真實(shí)的設(shè)計(jì)中clock是不可能長(zhǎng)的完全平的。那么可以通過useful skew 來達(dá)到data clock setup&hold 微妙的平衡。

通過分析DC 的timing報(bào)告人為通過set_clock_latency -clock xxx [get_pins xxxx]去調(diào)整clock tree 長(zhǎng)度,讓DC按照不平的clock tree 長(zhǎng)度進(jìn)行優(yōu)化。進(jìn)入INNOVUS的時(shí)候 INNOVUS create_ccopt_spec 會(huì)轉(zhuǎn)換set_clock_latency 命令為

set_ccopt_property -insertion_delay xxx [get_pins xxxx] 來調(diào)整clock tree長(zhǎng)度,達(dá)到更好的平衡。

或者在DC 中開啟ccd , 通過write_scripts 寫出工具根據(jù)組合邏輯和你的設(shè)置推出來的tree長(zhǎng)度腳本set_clock_latency -offset , 通過腳本轉(zhuǎn)換set_clock_latency -offset 為標(biāo)準(zhǔn)set_clock_latency -clock xxx [get_pins xxx] SDC ,進(jìn)入INNOVUS 優(yōu)化。

或者INNOVUS 刪除set_clock_latency 開啟Cadence 自己的useful skew ECF 來自動(dòng)進(jìn)行不平clock tree優(yōu)化。

至于結(jié)果,不好說,不同設(shè)計(jì)反映不一,推的過多會(huì)導(dǎo)致hold難修。當(dāng)然Synopsys會(huì)推薦DC 可以開hold corner 然后來估計(jì)hold的影響,讓推的不要太兇。

針對(duì)這種結(jié)構(gòu)一個(gè)M clock驅(qū)動(dòng)兩坨邏輯紅色和上面黑色。

通常做法是整一個(gè)M 整一個(gè)GCLK G1 GCLK G2 然后設(shè)置clock_group 來解決。

不要嘗試直接在G2 位置create一個(gè)master clk, 然后設(shè)置clock_group

這種會(huì)導(dǎo)致G2 前面的source latency 丟失,導(dǎo)致無法分析前面路徑的延時(shí)SI 等影響,也不能用來signoff

但是這種類型的SDC 用來INNOVUS ccopt 來長(zhǎng)clock tree是極好的。尤其是當(dāng)你不怎么熟悉innovus的ccopt spec ,但是你又很熟悉sdc和clock結(jié)構(gòu)的時(shí)候。

innovus默認(rèn)create的spec就不會(huì)balance 紅色和藍(lán)色因?yàn)槟愕腉2 地方的create的是一個(gè)master_clock

當(dāng)然別忘了update_constraint update回來,更別忘了手動(dòng)call update_io_latency/set_propagate_clock 來propagated clock 否則你長(zhǎng)完tree你的clock還是ideal的。

最后強(qiáng)調(diào)一點(diǎn),默認(rèn)innovus create ccopt spec 是不識(shí)別sdc里面的 clock_group , false_path 的,它只根據(jù)你的clock 物理連接結(jié)構(gòu)走。 當(dāng)然有setting可以讓create ccopt spec去識(shí)別 clock_group 和false_path ,但是只是大家都不這么做而已。具體原因可能是工具不完善吧,也有可能是這樣創(chuàng)建的spec 文件太大,或者太多的這種ccopt的設(shè)置會(huì)導(dǎo)致不期望的結(jié)果之類的。

著重注意IP 位置的clock ,有的情況是一個(gè)ip是liberty ,internal pin會(huì)打數(shù)據(jù) D 出來同時(shí)這個(gè)internalpin又會(huì)打clock出來 IP 外面會(huì)有flipflop來接數(shù)據(jù),這種path由于launch clock 無法調(diào)整。導(dǎo)致timing不好收斂。

或者是這種IP 作為liberty internal pin會(huì)打clock出來給flipflop launch 然后再用這個(gè)internalpin到IP 邊界上去check。這種由于capture clock 沒法控制同樣不好收斂。

針對(duì)這種情況及時(shí)syn pr, 聯(lián)系vendor 與設(shè)計(jì), 確認(rèn)路徑的正確。設(shè)計(jì)能retime flipflop 多次打拍就提前做。方便timing收斂。

PR 盡量和dft以及sdc owner多溝通。了解dft test_clock sdc里面是怎么下的。通常情況test_clock 會(huì)通過不同的occ去trigger 幾乎所有的flipflop 。一般情況下dft 穿chain是分clock domain 穿的。也就是各個(gè)occ是相互不check的。當(dāng)你的pr sdc為了簡(jiǎn)便下的比較粗的情況比如一個(gè)create 一個(gè)test_clock 完事,沒有在各個(gè)occ上做test_clock的分開處理。那么建議在ccopt spec里面把test_clock skew group 設(shè)置成none不要讓它去balance。否則它會(huì)退拽整個(gè)設(shè)計(jì)的tree。

設(shè)計(jì)時(shí)鐘樹時(shí)候盡量不要讓block 的clock 穿兩個(gè)port到頂層再去trigger 兩個(gè)flipflop相互拍數(shù)據(jù)。這樣會(huì)導(dǎo)致clock branch point 在block內(nèi)部,導(dǎo)致cppr過小timing不好收斂。

這對(duì)這個(gè)問題其實(shí)還有變形,原理其實(shí)都是控制clock tree 的branch point 來控制cppr來優(yōu)化timing

如圖A block 產(chǎn)生clock 到B block 拍數(shù)據(jù)給C block 左邊連接是不是branch point 在A block內(nèi)部這樣cppr 就小。

如果改成右邊的結(jié)構(gòu) branch point 就在B block cppr 就會(huì)變大。當(dāng)然要注意這時(shí)候可能capture path就會(huì)過長(zhǎng)也許對(duì)hold不利。所以要做trade off。本質(zhì)點(diǎn)在于移動(dòng)clock branck point.

-

控制器

+關(guān)注

關(guān)注

114文章

16973瀏覽量

182985 -

分頻器

+關(guān)注

關(guān)注

43文章

490瀏覽量

50842 -

SDC

+關(guān)注

關(guān)注

0文章

49瀏覽量

15813 -

DFT算法

+關(guān)注

關(guān)注

0文章

27瀏覽量

7684 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6717

發(fā)布評(píng)論請(qǐng)先 登錄

請(qǐng)問CUBEmx需要什么樣的電腦配置才能運(yùn)行流暢

編程93AA46AE需要什么樣的模塊

請(qǐng)問中國(guó)需要什么樣的FPGA?

請(qǐng)問開發(fā)6936和69213需要什么樣的開發(fā)工具包?

請(qǐng)問一下需要什么樣的整流橋驅(qū)動(dòng)這個(gè)電機(jī)?

什么是Clock Tree

嵌入式行業(yè)需要什么樣的技術(shù)人才?

嵌入式這個(gè)行業(yè)到底需要什么樣的技術(shù)人才

AI時(shí)代,我們到底需要什么樣的“大腦”

智能制造生產(chǎn)模式需要什么樣的自動(dòng)控制系統(tǒng)

嵌入式開發(fā)培訓(xùn)好學(xué)嗎?零基礎(chǔ)嵌入式學(xué)習(xí)需要什么樣的基礎(chǔ)呢

AI智能眼鏡都需要什么芯片

大家需要什么樣的clocktree呢?芯片的動(dòng)脈CLOCK TREE介紹

大家需要什么樣的clocktree呢?芯片的動(dòng)脈CLOCK TREE介紹

評(píng)論