今天在 GitHub 上看到一個 C 語言項目,用大約 600 行代碼實現了一個 RISC-V CPU 核,甚為感嘆,分享一下。不管是學習 C,還是學習 RISC-V,這個項目都有非常高的學習價值,開源萬歲!

rv

用 ANSI C 編寫的 RISC-V CPU 內核。

特征:

- RV32IMC 用戶級實現

- 通過 riscv 測試中所有支持的測試

- ~600 行代碼

- 不使用任何大于 32 位的整數類型,即使對于乘法也是如此

- 簡單 API(兩個函數,加上您提供的兩個內存回調函數)

- 無內存分配

應用程序接口

/* Memory access callbacks: data is input/output, return RV_BAD on fault, 0 otherwise */

typedef rv_res (*rv_store_cb)(void *user, rv_u32 addr, rv_u8 data);

typedef rv_res (*rv_load_cb)(void *user, rv_u32 addr, rv_u8 *data);

/* Initialize CPU. */

void rv_init(rv *cpu, void *user, rv_load_cb load_cb, rv_store_cb store_cb);

/* Single-step CPU. Returns 0 on success, one of RV_E* on exception. */

rv_u32 rv_step(rv *cpu);

用法

#include < stdio.h >

#include < string.h >

#include "rv.h"

rv_res load_cb(void *user, rv_u32 addr, rv_u8 *data) {

if (addr - 0x80000000 > 0x10000) /* Reset vector is 0x80000000 */

return RV_BAD;

*data = ((rv_u8 *)(user))[addr - 0x80000000];

return RV_OK;

}

rv_res store_cb(void *user, rv_u32 addr, rv_u8 data) {

if (addr - 0x80000000 > 0x10000)

return RV_BAD;

((rv_u8 *)(user))[addr - 0x80000000] = data;

return RV_OK;

}

rv_u32 program[2] = {

/* _start: */

0x02A88893, /* add a7, a7, 42 */

0x00000073 /* ecall */

};

int main(void) {

rv_u8 mem[0x10000];

rv cpu;

rv_init(&cpu, (void *)mem, &load_cb, &store_cb);

memcpy((void *)mem, (void *)program, sizeof(program));

while (rv_step(&cpu) != RV_EECALL) {

}

printf("Environment call @ %08X: %un", cpu.pc, cpu.r[17]);

return 0;

}

為rv編譯程序

使用 riscv-gnu-toolchain工具鏈和 rv 鏈接腳本 。

建議使用gcc命令行:

riscv64-unknown-elf-gcc example.S -nostdlib -nostartfiles -Tlink.ld -march=rv32imc -mabi=ilp32 -o example.o -e _start -g -no-pie

然后用 obj 工具將0x80000000起始的二進制代碼生成能被rv加載的二進制文件:

riscv64-unknown-elf-objcopy -g -O binary example.o example.bin

支持的指令列表

參見 支持指令列表。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

內核

+關注

關注

3文章

1412瀏覽量

41195 -

cpu

+關注

關注

68文章

11057瀏覽量

216335 -

ANSI

+關注

關注

0文章

29瀏覽量

20744 -

C代碼

+關注

關注

1文章

90瀏覽量

14709 -

RISC-V

+關注

關注

46文章

2514瀏覽量

48434

發布評論請先 登錄

相關推薦

熱點推薦

64位RISC-V CPU發展現狀和未來前景

RISC-V CPU發展情況 實際上,目前RISC-V已經開始64位CPU的研發,也已經有相關內核和產品面市,比如平頭哥64位

瑞薩電子推出64位RISC-V CPU內核RZ/Five通用MPU,開創RISC-V技術先河

瑞薩電子今日宣布,推出基于64位RISC-V CPU內核的RZ/Five通用微處理器(MPU)——RZ/Five采用Andes AX45MP,基于RISC-V

發表于 03-01 13:54

?1606次閱讀

瑞薩電子推出采用自研RISC-V CPU內核的通用32位MCU

2024 年 3 月 26 日,中國北京訊 - 全球半導體解決方案供應商瑞薩電子(TSE:6723)今日宣布率先在業內推出基于內部自研CPU內核構建的通用32位RISC-V微控制器(MCU

發表于 03-30 22:08

《RISC-V能否復制Linux 的成功?》

個角度來看,RISC-V ISA是推動RISC-V發展的關鍵因素。回想20年前,基于Linux內核的實現方案非常多,遠遠超過今天基于RISC-V

發表于 11-26 20:20

RISC-V MCU開發 (一):集成開發環境

近年來,RISC-V生態獲得了空前的繁榮發展,國內外眾多科技公司紛紛下場布局、行業應用層出不窮,搭載RISC-V內核的MCU也逐漸走入了工程師的日常開發工作中。 工欲善其事必先利其器,要想實現

發表于 09-22 14:44

如何實現一個RISC-V內核架構的芯片移植工作

使用 common 文件夾中的任務切換代碼RT-Thread RISC-V 內核移植 API 實現內核移植的主要工作內容,主要就是

發表于 03-25 10:11

RISC-V基礎知識:模塊化開放式的ISA CISC和RISC代碼區別

/ti/)TIonal— 一個開放的 ISARISC-V是一種開放式指令集架構(ISA),這意味著您可以自由地在微處理器或微控制器中實現RISC-V CPU,而無需向任何人支付使用此I

發表于 12-23 17:51

Occamy RISC-V 前景如何

位 FPU,以及兩顆來自美光的 16GB HBM2e 內存。處理器的內核通過中介層實現互連,雙塊 CPU 可提供 0.75 FP64 TFLOPS 的性能和 6 FP8 TFLOPS 算力。那么Occamy

發表于 05-13 08:44

RISC-V MCU開發 (六):代碼下載

、CH58x、CH32Fx、CH32Vx等RISC-V/ARM內核MCU工程的代碼下載功能。其中,對于CH56x、CH57x、CH58x等型號,MRS還支持關閉兩線仿真調試接口功能;對于CH32Fx、CH32Vx型號,MRS支持

發表于 12-02 09:06

?11次下載

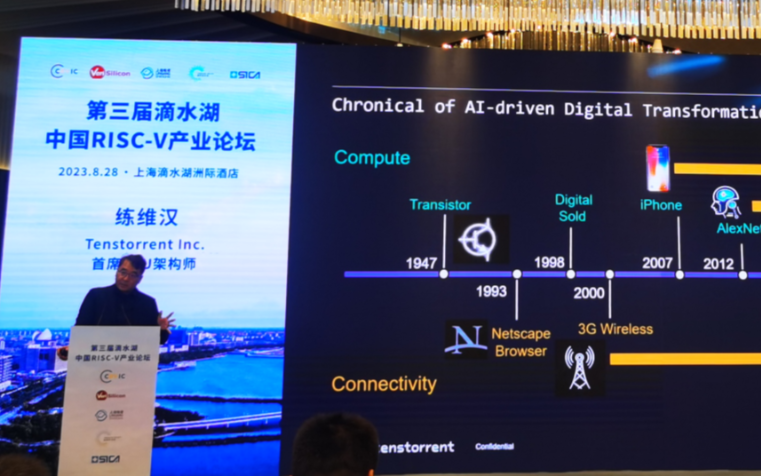

TenstorrentInc首席CPU構架師 練維漢:助力數字化升級的RISC-V AI 高性能CPU

”,曾在水果公司作CPU的架構設計師。練維漢除介紹RISC-V內核的高性能 CPU IP內核技術之外,也對近期熱門的

新聞快訊 | 瑞薩推出第一代32位RISC-V CPU內核

新聞快訊 全球半導體解決方案供應商瑞薩電子(TSE:6723)宣布成功設計、測試并推出基于開放標準RISC-V指令集架構(ISA)的32位CPU內核。瑞薩作為業內首個為32位通用RISC-V

瑞薩推出采用自研CPU內核的通用32位RISC-V MCU 加強RISC-V生態系統布局

瑞薩推出采用自研CPU內核的通用32位RISC-V MCU 加強RISC-V生態系統布局 RISC-V MCU為開發人員帶來低功耗、高性能的

發表于 03-28 19:00

?839次閱讀

使用ANSI C代碼實現RISC-V CPU內核

使用ANSI C代碼實現RISC-V CPU內核

評論