串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立的ASSP 或ASIC 器件。在過去幾年中已經(jīng)看到有內(nèi)置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價(jià)格昂貴。

本方案是以CME的低功耗系列FPGA的HR03為平臺,實(shí)現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data Recovery,時(shí)鐘數(shù)據(jù)恢復(fù)),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發(fā)周期短等特點(diǎn)。

1 硬件接口:

硬件的接口如上圖所示,主要包括發(fā)送與接收模塊。

發(fā)送模塊包括8b/10b編碼器,并串轉(zhuǎn)換器,鎖相環(huán)(PLL)頻率合成器和發(fā)送器,接收模塊包括 8b/10b解碼器,Comma 檢測器,串并轉(zhuǎn)換器,時(shí)鐘數(shù)據(jù)恢復(fù)器(CDR)和接收器。

8b/10b編碼器用于將從上層協(xié)議芯片發(fā)送過來的字節(jié)信號映射成直流平衡的 10 位8b/10b 編碼,并串轉(zhuǎn)換用于將 10 位編碼結(jié)果串行化,并串轉(zhuǎn)換所需的高速、低抖動(dòng)時(shí)鐘由鎖相環(huán)提供,發(fā)送器用于將 CMOS 電平的高速串行碼流轉(zhuǎn)換成抗噪聲能力較強(qiáng)的差分信號,經(jīng)背板連接或光纖信道發(fā)送到接收機(jī)。

在接收端,接收器將接收到的低擺幅差分信號還原為 CMOS 電平的串行信號,CDR 從串行信號中抽取時(shí)鐘信息,完成對串行數(shù)據(jù)的采樣,串并轉(zhuǎn)換利用 CDR 恢復(fù)的時(shí)鐘,將串行信號轉(zhuǎn)換成 10 位的并行數(shù)據(jù),Comma 檢測器檢測特殊的 Comma 字符,調(diào)整字邊界,字邊界正確的并行數(shù)據(jù)經(jīng)過 8b/10b 解碼,還原為字節(jié)信號,傳送到上層協(xié)議芯片,完成整個(gè)信息傳輸過程。

實(shí)際的設(shè)計(jì)中,CDR部分是由純邏輯電路完成的,為設(shè)計(jì)的的部分,下面將介紹數(shù)字CDR在HR03的實(shí)現(xiàn)方案。

2 數(shù)字CDR:

CDR模塊作用是從數(shù)據(jù)中恢復(fù)嵌入的時(shí)鐘,然后接收器按照恢復(fù)的時(shí)鐘進(jìn)行數(shù)據(jù)位對齊并通過comma進(jìn)行字對齊。,將數(shù)據(jù)進(jìn)行8b/10b解碼,供系統(tǒng)使用。

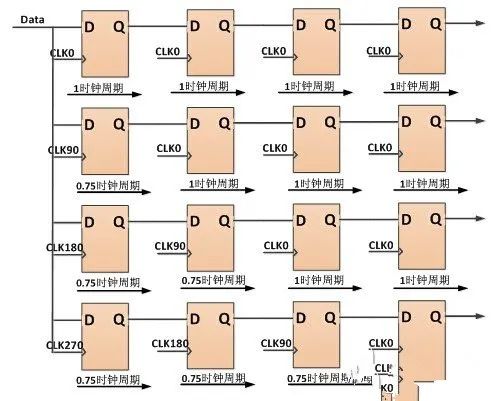

本方案采用同頻多相的時(shí)鐘采樣方法,具體實(shí)現(xiàn)過程利用PLL產(chǎn)生4個(gè)時(shí)鐘頻率相同,相位相差90度的時(shí)鐘,分別為clk0、clk90、clk180、clk270,這四個(gè)時(shí)鐘輸出完全同步,利用4個(gè)時(shí)鐘對數(shù)據(jù)進(jìn)行采樣,以獲得4倍過采樣的效果,具體的實(shí)現(xiàn)過程如下圖所示:

在數(shù)據(jù)時(shí)鐘恢復(fù)時(shí),將到來的數(shù)據(jù)分別輸入到四個(gè)觸發(fā)器,分別用4個(gè)不同的相位進(jìn)行采樣,要注意保證從輸入引腳到四個(gè)觸發(fā)器的延遲基本一致。

列觸發(fā)器的觸發(fā)分別由時(shí)鐘CLK0、CLK90、CLK180、CLK270的上升沿觸發(fā),按照這樣的方式來觸發(fā)就可以得到四個(gè)數(shù)據(jù)采樣點(diǎn)。這樣就將原始時(shí)鐘周期分成了四個(gè)單獨(dú)的90度的區(qū)域,如果系統(tǒng)時(shí)鐘為200MHz,上圖所示的電路就相當(dāng)于產(chǎn)生了800MHz 的采樣速率。

僅通過一階的觸發(fā)器,輸出的采樣數(shù)據(jù)存在亞穩(wěn)態(tài)的問題,因此需對采樣點(diǎn)作進(jìn)一步的處理。這里可將四個(gè)采樣點(diǎn)通過進(jìn)一步的觸發(fā),除掉亞穩(wěn)態(tài)的問題,從而使采樣點(diǎn)移到下一個(gè)相同的時(shí)鐘域。通常,亞穩(wěn)態(tài)的去除要經(jīng)過兩三級的處理,這就使得在有效數(shù)據(jù)輸出前會有數(shù)位無效的數(shù)據(jù),在數(shù)據(jù)采樣的個(gè)階段,電路檢測數(shù)據(jù)線上數(shù)據(jù)的傳輸。當(dāng)檢測到有數(shù)據(jù)傳輸時(shí),對傳輸數(shù)據(jù)的有效性進(jìn)行確認(rèn)。確認(rèn)數(shù)據(jù)有效后,輸出高電平來指示采樣點(diǎn)有數(shù)據(jù)傳輸。

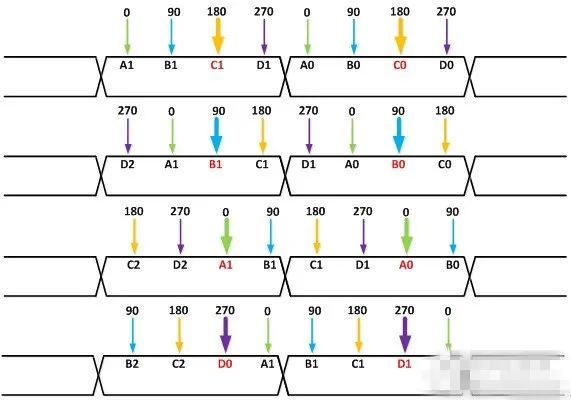

因?yàn)榻K有四個(gè)輸出,所以需要一個(gè)復(fù)用器來選擇數(shù)據(jù)。發(fā)送數(shù)據(jù)與采樣時(shí)鐘的對應(yīng)關(guān)系如上圖所示,其對應(yīng)關(guān)系分為4種情況,每種情況下對應(yīng)一個(gè)的采樣時(shí)鐘,系統(tǒng)通過對數(shù)據(jù)邊沿位置信息的判斷,來確定哪路時(shí)鐘為采樣時(shí)鐘,并利用復(fù)用器從選定的時(shí)鐘域中選擇數(shù)據(jù)位,例如檢測電路確定從時(shí)鐘域A中采樣的數(shù)據(jù)有效,那么將時(shí)鐘域A中采樣的數(shù)據(jù)通過輸出端輸出。

3 結(jié)束語:

通過對純數(shù)字電路的CDR電路,在沒有硬核的支持下,完成了FPGA上SERDES的接口設(shè)計(jì),并通過實(shí)驗(yàn)的傳輸測試,在HR03的FPGA上,可完成100~200Mbps的數(shù)據(jù)傳輸。

?

?

?

?

掃碼加微信邀請您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:基于FPGA芯片的SERDES接口電路設(shè)計(jì)

文章出處:【微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618636

原文標(biāo)題:基于FPGA芯片的SERDES接口電路設(shè)計(jì)

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

從SerDes到SoC,全場景適配的FCom差分晶振設(shè)計(jì)全解

FPGA從0到1學(xué)習(xí)資料集錦

什么是SerDes?SerDes有哪些應(yīng)用?

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

使用FPGA對40G以太網(wǎng)接口芯片Serdes進(jìn)行測試的方法

使用FPGA的LVDS_serdes模式驅(qū)動(dòng)DP83867E,可以不使用PHY芯片上自帶的SGMII_SCO(625MHz)的時(shí)鐘嗎?

lvds接口和HDMI的區(qū)別 lvds接口電路設(shè)計(jì)技巧

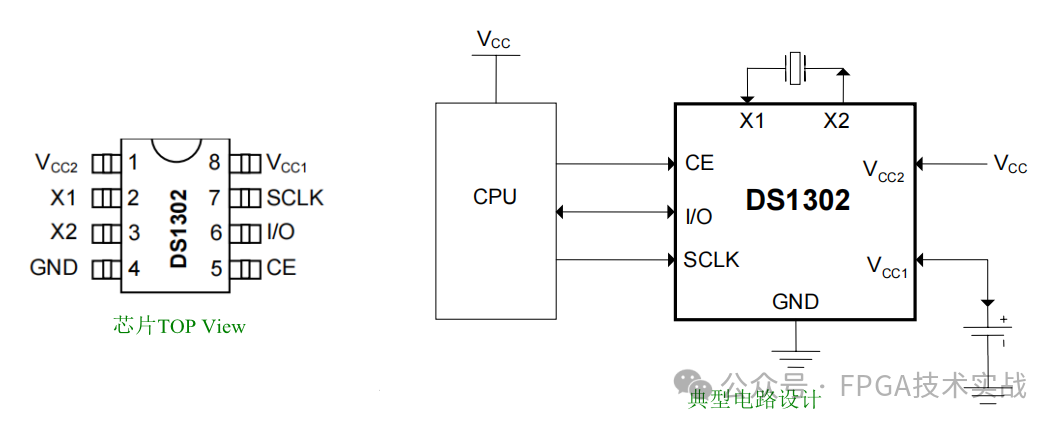

DS1302芯片與FPGA之間SPI通信原理

國科微斬獲“強(qiáng)芯中國創(chuàng)新IC”獎(jiǎng)項(xiàng),車載SerDes芯片漸入佳境

接口芯片的譯碼電路設(shè)計(jì)一般采用什么方法

ASP4644在FPGA SERDES供電中的應(yīng)用

解讀MIPI A-PHY與車載Serdes芯片技術(shù)與測試

基于FPGA芯片的SERDES接口電路設(shè)計(jì)

基于FPGA芯片的SERDES接口電路設(shè)計(jì)

評論