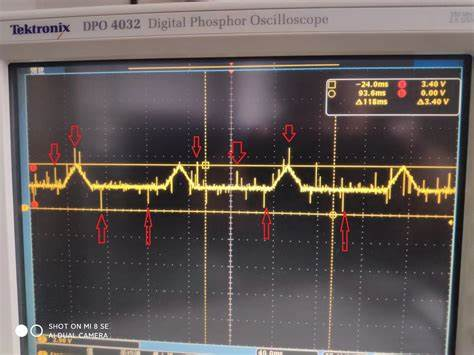

可編程邏輯系統(tǒng)通常部署在可能存在噪聲的應用中。這種噪聲會影響可編程邏輯設計接收的信號。例如,它可能會導致信號故障或跳動,如果處理不當,可能會導致設計和操作出現(xiàn)問題。

毛刺的持續(xù)時間是隨機的,并且與時鐘沿不同步。因此,它們可能會導致下游信息損壞。

處理此問題的最常見方法是使用毛刺濾波器來濾除毛刺和反彈。

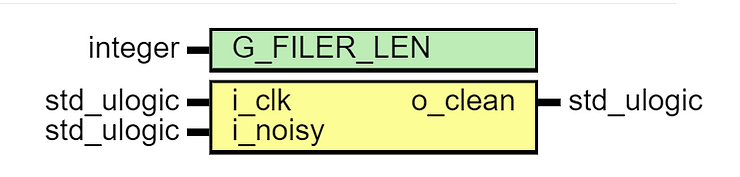

毛刺濾波器核心是使用長度可變的移位寄存器,噪聲信號被放到寄存器中,直到移位寄存器的所有值都一致。此時,信號可以視為穩(wěn)定。當然,我們必須確定潛在毛刺和反彈可能持續(xù)多長時間,以確保時鐘周期的寄存器大小正確。這就是為什么我們的毛刺濾波器需要非常靈活,并且需要確保其大小能夠適合每個應用程序的要求。

濾波器應該能夠接收噪聲輸入并濾除持續(xù)時間為多個時鐘脈沖的毛刺。

libraryieee; useieee.std_logic_1164.all; useieee.numeric_std.all; entityglitch_filteris generic( G_FILER_LEN:integer:=8 ); port( i_clk:instd_ulogic; i_noisy:instd_ulogic; o_clean:outstd_ulogic ); endglitch_filter; architecturebehaviourofglitch_filteris signals_delay_line:std_ulogic_vector(G_FILER_LEN-1downto0); signals_delay_and:std_ulogic; signals_delay_nor:std_ulogic; signals_output_clean:std_ulogic; begin o_clean<=?s_output_clean; ????--Delay?disctete?using?delay?line ????synchroniser_process?:?process?(i_clk)?begin ????????if?rising_edge(i_clk)?then ????????????s_delay_line?<=?s_delay_line(G_FILER_LEN?-?2?downto?0)?&? ????????????????????????????i_noisy; ????????end?if; ????end?process; ????--Generate?AND?and?NOR?of?delay?line?bits ????s_delay_and?<=?'1'?when?to_01(s_delay_line)?=? ????????????????????????????(s_delay_line'range?=>'1')else'0'; s_delay_nor<=?'1'?when?to_01(s_delay_line)?=? ????????????????????????????(s_delay_line'range?=>'0')else'0'; --Setdiscretebasedondelayline output_process:process(i_clk)begin ifrising_edge(i_clk)then ifs_delay_nor='1'then s_output_clean<=?'0'; ????????????elsif?s_delay_and?=?'1'?then ????????????????s_output_clean?<=?'1'; ????????????end?if; ????????end?if; ????end?process; end?behaviour;

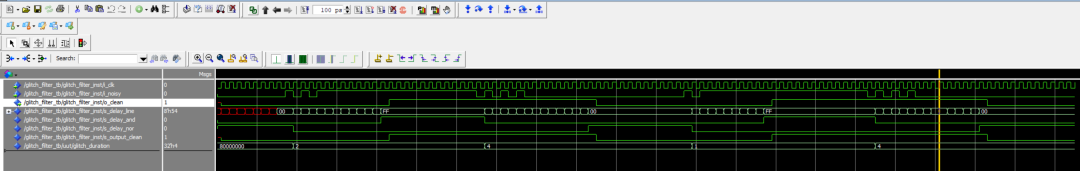

為了測試這個模塊,創(chuàng)建一個簡單的測試文件,它將隨機數(shù)量的毛刺注入信號中。在信號改變狀態(tài)后,許多隨機毛刺被輸入到信號中。如果濾波器運行正常,則這些毛刺將在毛刺濾波器輸出干凈的信號。

libraryieee; useieee.std_logic_1164.all; useieee.numeric_std.all; useieee.math_real.all; entityglitch_filter_tbis end; architecturebenchofglitch_filter_tbis componentglitch_filter generic( G_FILER_LEN:integer ); port( i_clk:instd_ulogic; i_noisy:instd_ulogic; o_clean:outstd_ulogic ); endcomponent; --Clockperiod constantclk_period:time:=10ns; --Generics constantG_FILER_LEN:integer:=8; --Ports signali_clk:std_ulogic:='0'; signali_noisy:std_ulogic; signalo_clean:std_ulogic; begin i_clk<=?not?i_clk?after?(clk_period/2); ??glitch_filter_inst?:?glitch_filter ????generic?map?( ??????G_FILER_LEN?=>G_FILER_LEN ) portmap( i_clk=>i_clk, i_noisy=>i_noisy, o_clean=>o_clean ); uut:process variableglitch_duration:integer; variableseed1:positive:=1; variableseed2:positive:=283647823; impurefunctioninteger_random(min,max:integer)returnintegeris variablerandom:real; begin uniform(seed1,seed2,random); returninteger(round(random*real(max-min)+real(min))); endfunction; begin i_noisy<=?'0'; ????wait?until?rising_edge(i_clk); ????wait?for?G_FILER_LEN?*?clk_period; ????test:?for?i?in?0?to?1?loop ????????i_noisy?<=?'1'; ????????wait?until?rising_edge(i_clk); ????????glitch_duration?:=?integer_random(1,5); ????????for?x?in?0?to?glitch_duration?loop ????????????i_noisy?<=?not?i_noisy; ????????????wait?until?rising_edge(i_clk); ????????end?loop; ????????i_noisy?<=?'1'; ????????wait?for?20?*?clk_period; ????????report?"loop?high?completed"?severity?note; ????????i_noisy?<=?'0'; ????????wait?until?rising_edge(i_clk); ????????glitch_duration?:=?integer_random(1,5); ????????for?x?in?0?to?glitch_duration?loop ????????????i_noisy?<=?not?i_noisy; ????????????wait?until?rising_edge(i_clk); ????????end?loop; ????????i_noisy?<=?'0'; ????????wait?for?20?*?clk_period; ????????report?"loop?low?completed"?severity?note; ????end?loop; ????report?"Simulation?complete"?severity?failure; ???? end?process; end;

運行仿真后顯示在信號狀態(tài)改變后隨機數(shù)量的脈沖便增加。檢查輸出信號表明濾波器已正確濾除輸入信號中可能存在的毛刺。

正如在一開始所說的,這樣的濾波器對于部署在可能存在電噪聲的環(huán)境中非常有用。與 BRAM 上的 EDAC 等其他緩解策略相結合,這是可用于實現(xiàn)設計彈性的關鍵方法之一。

審核編輯:劉清

-

濾波器

+關注

關注

162文章

8076瀏覽量

181042 -

寄存器

+關注

關注

31文章

5421瀏覽量

123359 -

狀態(tài)機

+關注

關注

2文章

493瀏覽量

28070 -

BRAM

+關注

關注

0文章

41瀏覽量

11236 -

時鐘脈沖

+關注

關注

0文章

19瀏覽量

12904

原文標題:【數(shù)字實驗室】消除毛刺

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

TPA3110D2無信號輸入時,輸出336kHZ的正弦波信號有明顯的毛刺,如何濾除毛刺?

引入輸入濾波器來濾除噪聲設計

毛刺的濾波方法

怎樣去設計一個使用時序邏輯對單bit信號進行毛刺濾除操作的電路

FPGA | 競爭冒險和毛刺問題

電路從SDA和SCL線路中濾除毛刺的解決方法及過程

FPGA中的冒險現(xiàn)象和如何處理毛刺

電感的毛刺現(xiàn)象是什么意思?如何解決感應毛刺?

怎樣使用毛刺濾波器來濾除毛刺和反彈?

怎樣使用毛刺濾波器來濾除毛刺和反彈?

評論