作為邏輯工程師,在FPGA和數(shù)字IC開發(fā)和設(shè)計中,一般采用verilog,VHDL或SystemVerilog等作為硬件描述語言進行工程設(shè)計,將一張白板描繪出萬里江山圖景。

工程師在利用硬件描述語言進行數(shù)字電路設(shè)計時,需要遵守編譯器支持的Verilog,VHDL或systemverilog標準規(guī)范,并形成良好的RTL設(shè)計風格。

本文簡要介紹verilog-2005和systemverilog-2017標準,在應(yīng)用過程中,可根據(jù)自己擅長的語言進行設(shè)計。

一、verilog-2005標準

首先我們來看verilog-2005標準。

Verilog硬件描述語言(HDL)在本標準中定義。Verilog HDL是一種正式的符號,旨在用于電子系統(tǒng)創(chuàng)建的所有階段。因為它是機器可讀和人類可讀的,所以它支持硬件設(shè)計的開發(fā)、驗證、綜合和測試;硬件設(shè)計數(shù)據(jù)的通信;以及硬件的維護、改裝和采購。本標準的主要受眾是支持該語言的工具的實現(xiàn)者和該語言的高級用戶。

Verilog硬件描述語言(HDL)在1995年作為IEEE標準1364- 1995成為IEEE標準。它被設(shè)計成簡單、直觀和有效的,在多個抽象層次上采用標準文本格式,適用于各種設(shè)計工具,包括驗證模擬、定時分析、測試分析和綜合。正是由于這些豐富的功能,Verilog已被公認為集成電路(IC)設(shè)計人員的首選語言。

Verilog包含一組豐富的內(nèi)置原語,包括邏輯門、用戶可定義原語、開關(guān)和有線邏輯。它還具有設(shè)備引腳到引腳的延遲和定時檢查。抽象層次的混合本質(zhì)上是由兩種數(shù)據(jù)類型的語義提供的:網(wǎng)絡(luò)和變量。連續(xù)賦值提供了基本的結(jié)構(gòu)結(jié)構(gòu),其中變量和網(wǎng)的表達式可以連續(xù)地將值驅(qū)動到網(wǎng)上。程序賦值提供了基本的行為結(jié)構(gòu),其中涉及變量和凈值的計算結(jié)果可以存儲到變量中。設(shè)計由一組模塊組成,每個模塊都有一個輸入/輸出(I/O)接口,以及對其功能的描述,可以是結(jié)構(gòu)的、行為的,也可以是混合的。這些模塊形成一個層次結(jié)構(gòu),并通過網(wǎng)絡(luò)相互連接。

隨著IEEE Std 1364-2001的完成,在更大的Verilog社區(qū)中繼續(xù)進行工作,以確定該語言的突出問題以及可能增強的想法。當Accellera在2001年開始標準化SystemVerilog時,發(fā)現(xiàn)了可能導致Verilog 1364與SystemVerilog不兼容的其他問題。IEEE P1364工作組是作為SystemVerilog P1800工作組的一個小組委員會成立的,以幫助確保這些問題的一致解決。這項合作工作的結(jié)果是這個標準,IEEE標準1364-2005。

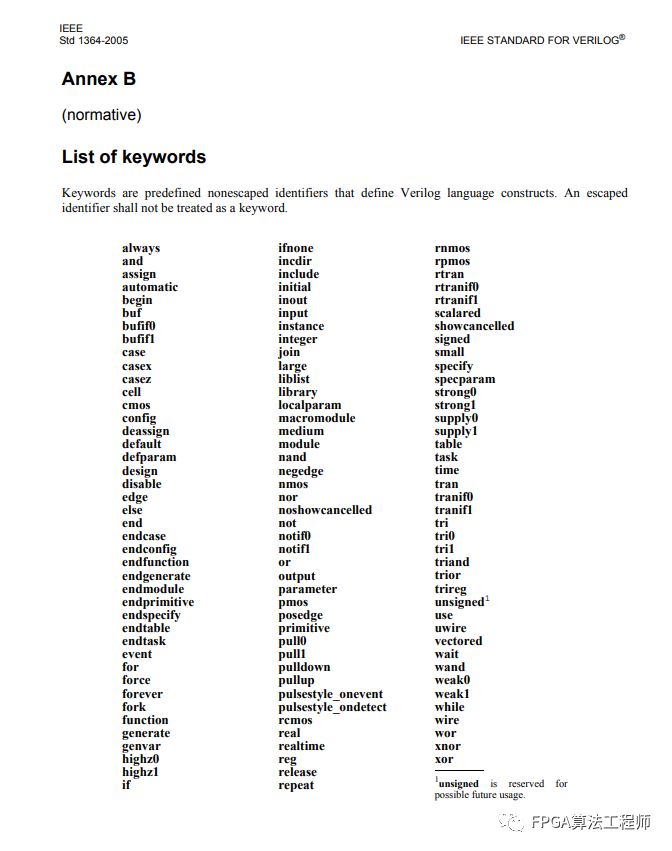

VerilogHDL語言的關(guān)鍵字列表:

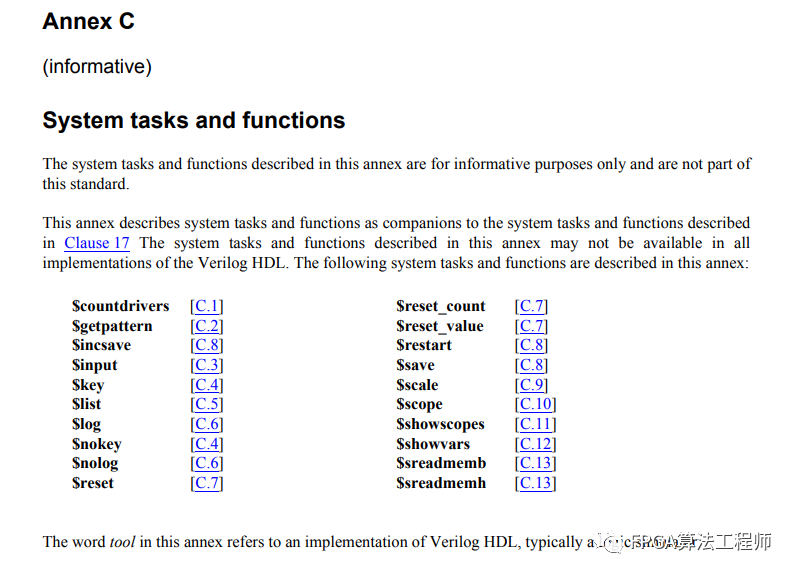

VerilogHDL語言的系統(tǒng)Task和Function列表:

更多詳細說明,參閱IEEE Std Verilog HDL。

二、SystemVerilog-2017

本標準為IEEE 1800SystemVerilog語言提供了語言語法和語義的定義,這是一種統(tǒng)一的硬件設(shè)計,規(guī)范和驗證語言。該標準包括對行為、寄存器傳輸級(RTL)和門級硬件描述的支持;Testbench、覆蓋、斷言、面向?qū)ο蠛图s束隨機結(jié)構(gòu);并且還為外國編程語言提供應(yīng)用程序編程接口(API)。

SystemVerilog語言既可以用于設(shè)計,也可以用于驗證,在FPGA、IC中占有重要地位。相對于VerilogHDL,提供了更豐富的設(shè)計和驗證規(guī)范,SystemVerilog改進了Verilog代碼的生產(chǎn)率、可讀性以及可重用性。

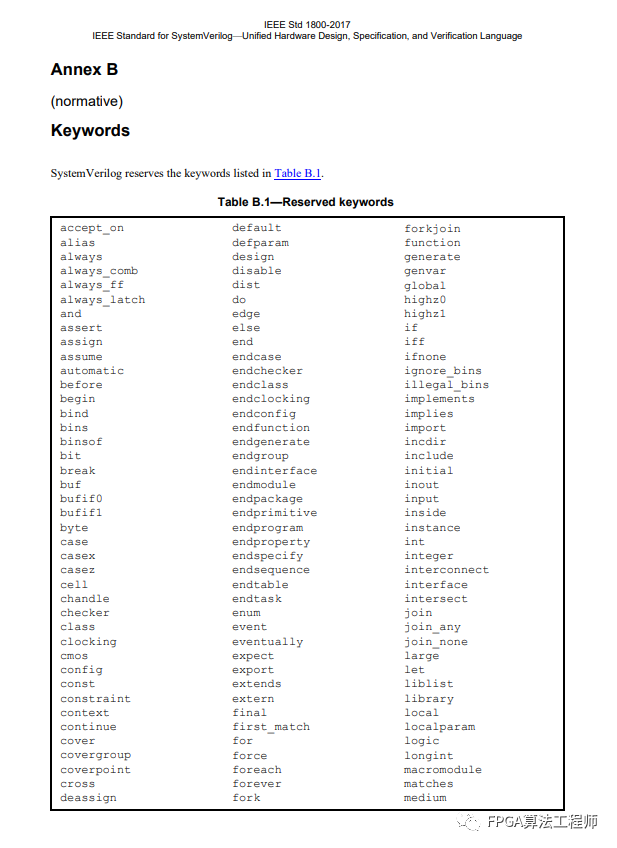

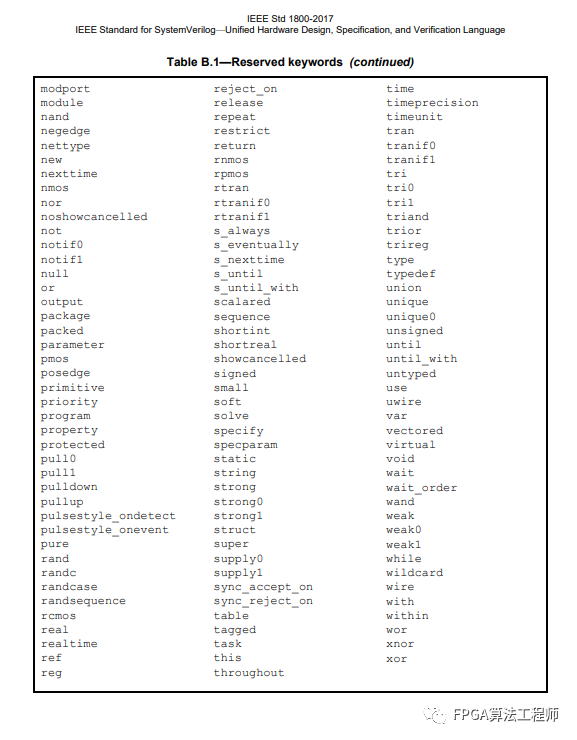

SystemVerilog語言的關(guān)鍵字列表:

更多詳細說明,參閱IEEE Std SystemVerilog。

IEEE官網(wǎng)Verilog HDL標準:1364-2005 - IEEE Standard for Verilog Hardware Description Language | IEEE Standard | IEEE Xplore

IEEE官網(wǎng)SystemVerilog標準:1800-2017 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language | IEEE Standard | IEEE Xplore

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1642文章

21920瀏覽量

612126 -

Verilog

+關(guān)注

關(guān)注

28文章

1365瀏覽量

111503 -

System

+關(guān)注

關(guān)注

0文章

165瀏覽量

37505 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60522 -

編譯器

+關(guān)注

關(guān)注

1文章

1652瀏覽量

49738

原文標題:【文檔必備】Verilog、SystemVerilog IEEE標準規(guī)范

文章出處:【微信號:FPGA算法工程師,微信公眾號:FPGA算法工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

SD卡接口標準規(guī)范

請給我分享《DDS Extensions for Time Sensitive Networking》標準規(guī)范?

現(xiàn)場電工技術(shù)操作標準規(guī)范

電工技術(shù)操作標準規(guī)范

IPC-TM-650阻抗測量標準規(guī)范

煙花爆竹機械 引線機標準規(guī)范 AQ4108--2008

音頻數(shù)據(jù)加工標準與工作規(guī)范標準規(guī)范

中國將更新FDT國家標準規(guī)范

LED燈具的安全標準規(guī)范

了解千兆光模塊和萬兆光模塊的標準規(guī)范

FMR52-AAECAABPCJK+AK四線制雷達料位計信號檢測標準規(guī)范

SMA連接器的國家標準規(guī)范

verilog-2005和systemverilog-2017標準規(guī)范

verilog-2005和systemverilog-2017標準規(guī)范

評論