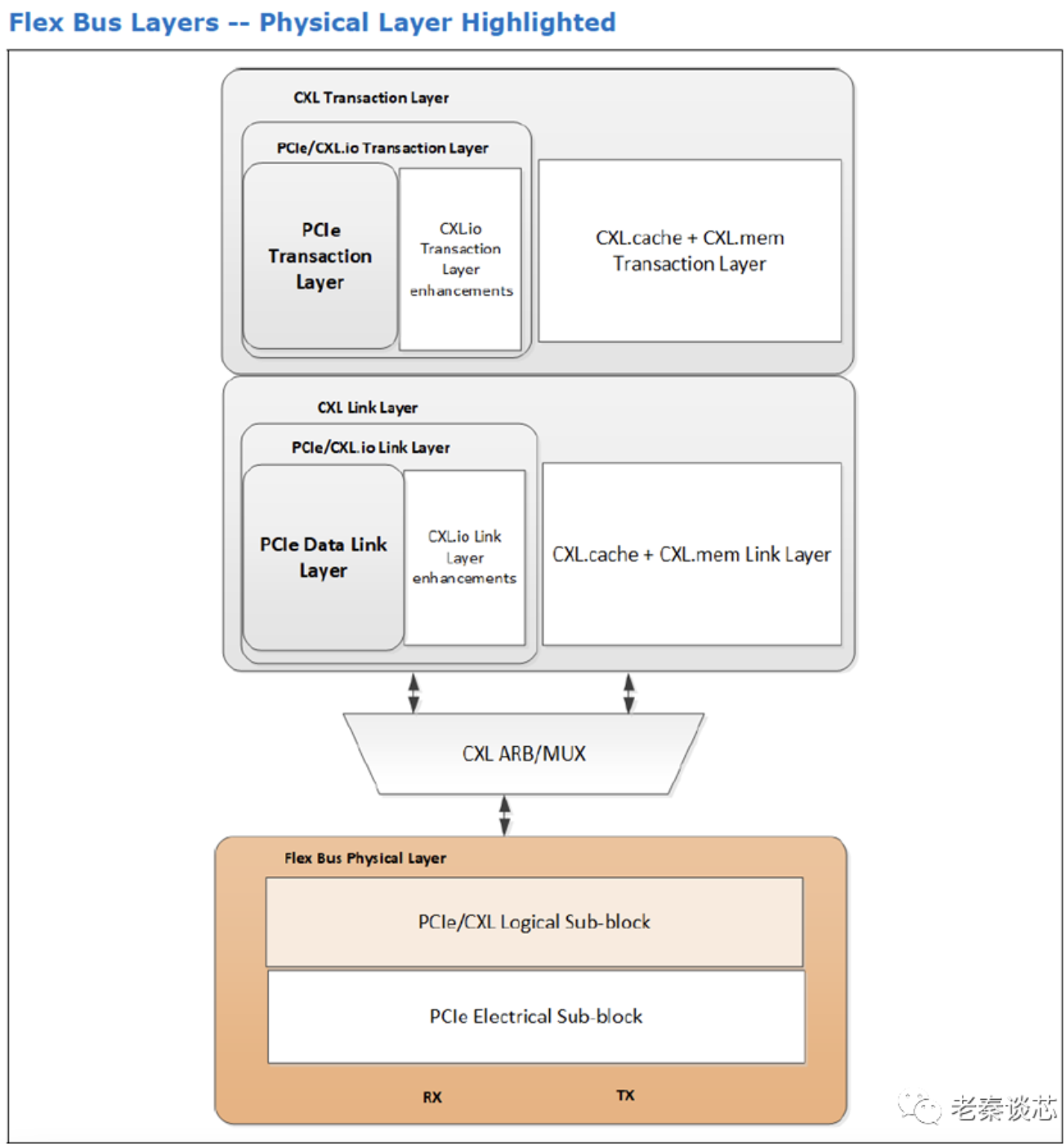

在傳輸端,F(xiàn)lex Bus物理層準(zhǔn)備從PCIe鏈路層或CXL ARB/MUX接收的數(shù)據(jù),以便通過(guò)Flex Bus鏈路進(jìn)行傳輸。在接收端,F(xiàn)lex Bus物理層對(duì)Flex Bus鏈路上接收的數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,并將其轉(zhuǎn)換為適當(dāng)?shù)母袷剑赞D(zhuǎn)發(fā)到PCIe鏈路層或ARB/MUX。

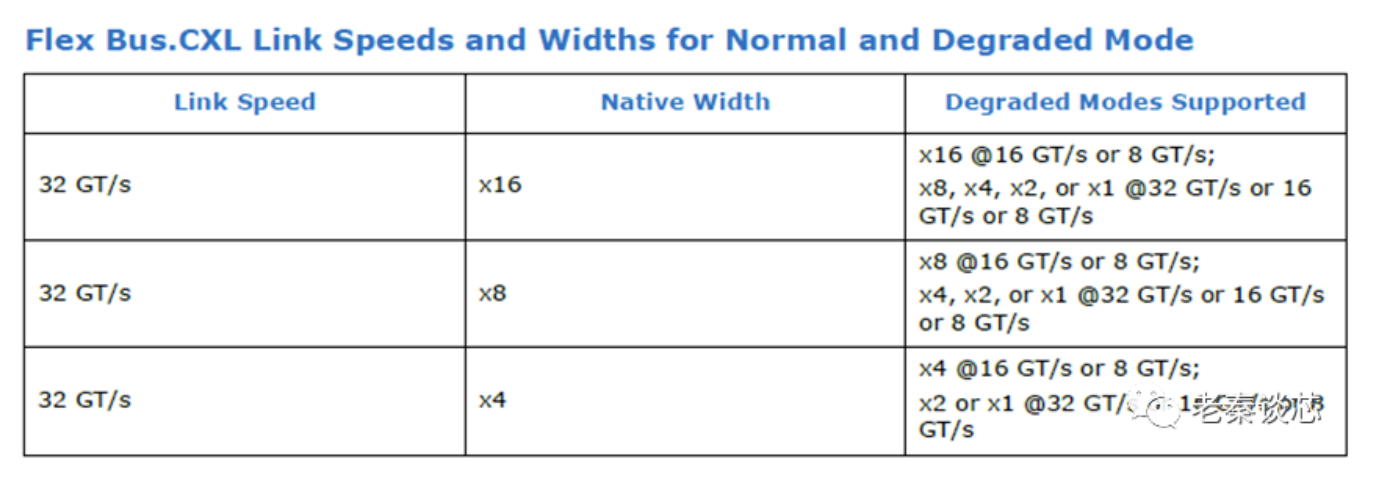

在初始鏈路訓(xùn)練期間,邏輯PHY在PCIe模式下工作,在訓(xùn)練至2.5 GT/s后,根據(jù)備用模式協(xié)商的結(jié)果,在適當(dāng)?shù)那闆r下切換到CXL模式。在CXL模式下,正常操作在本機(jī)鏈路寬度和32 GT/s鏈路速度下進(jìn)行。降級(jí)運(yùn)行模式包括8 GT/s或16 GT/s鏈路速度,和較小的x2和x1鏈路寬度。下表總結(jié)了協(xié)議支持的CXL鏈路寬度和鏈路速度組合。

6.2 Flex Bus的CXL幀和數(shù)據(jù)

6.2.1 有序集塊和數(shù)據(jù)塊

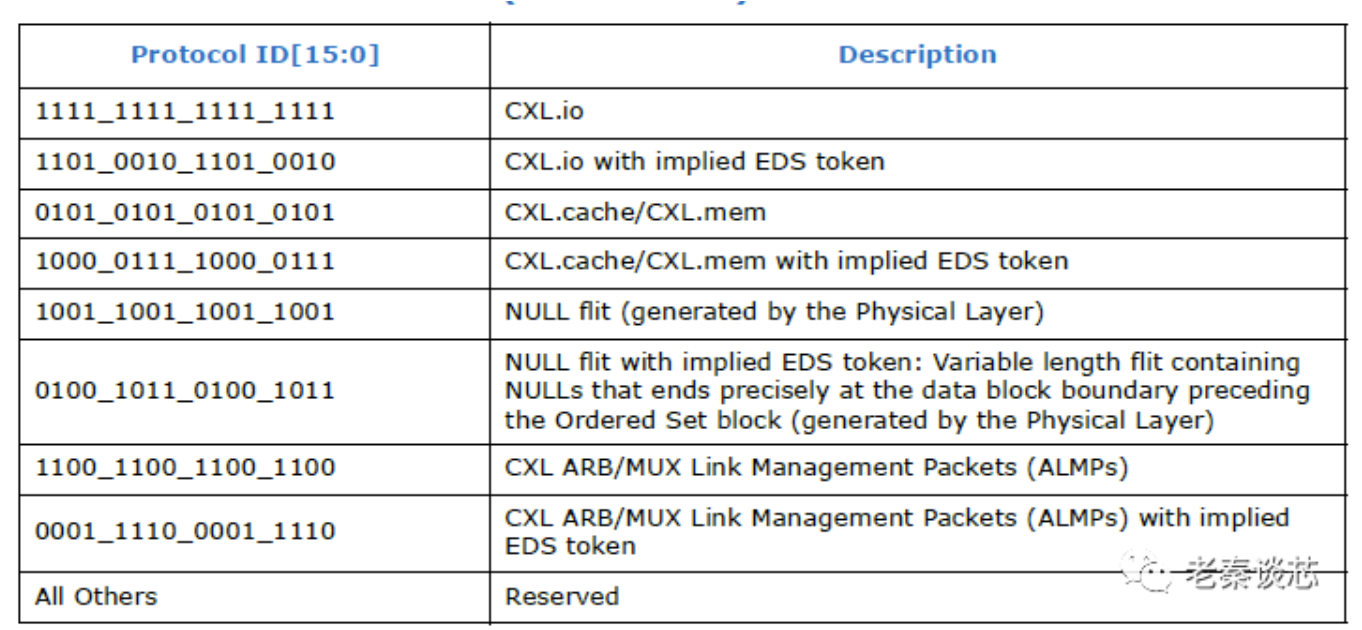

有序集塊(Ordered Set Block)和數(shù)據(jù)塊(Data Block)是PCIe里面的概念。有序集塊用于訓(xùn)練、進(jìn)入和退出電氣空閑、轉(zhuǎn)換到數(shù)據(jù)塊,以及時(shí)鐘容差補(bǔ)償?shù)龋@個(gè)放到講PCIe的時(shí)候再說(shuō)。數(shù)據(jù)塊用于傳輸從CXL鏈路層接收的flit。16-bit協(xié)議ID字段與從鏈路層接收到的每個(gè)528-bit(512-bit數(shù)據(jù)負(fù)載+16-bit CRC) flit相關(guān)聯(lián)。

6.2.2 Protocol ID[15:0]

16位協(xié)議ID字段指定傳輸?shù)膄lit是CXL.io、CXL.cache/CXL.mem還是其他有效負(fù)載。

當(dāng)鏈路層沒(méi)有有效flit時(shí),物理層插入NULL flit到數(shù)據(jù)流中。

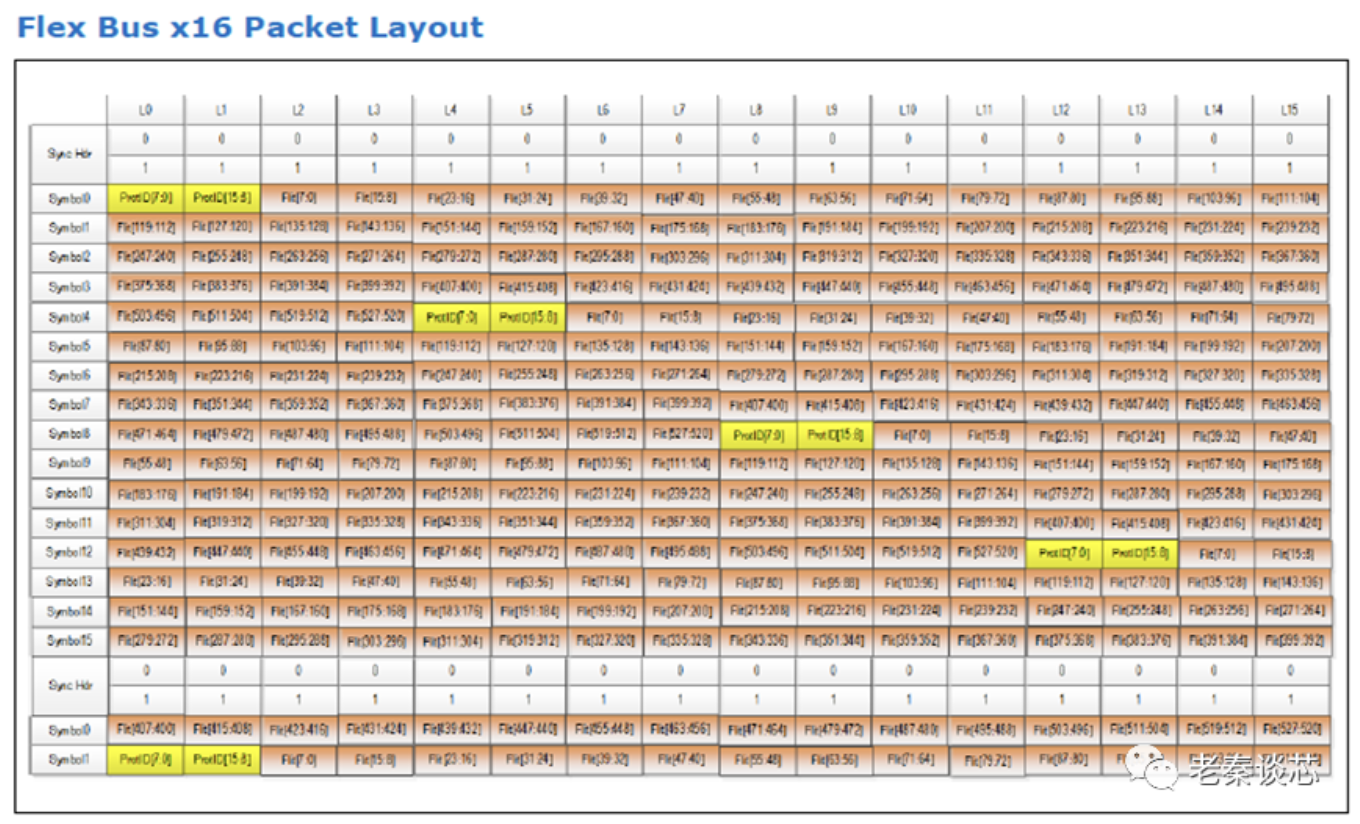

6.2.3 x16數(shù)據(jù)包

下圖顯示了x16鏈接的數(shù)據(jù)包布局。首先,16-bit傳輸協(xié)議ID被分成兩個(gè)8-bit,在Lane 0和Lane 1上傳輸;隨后是528-bit flit的傳輸,同樣是按照8-bit粒度拆分。

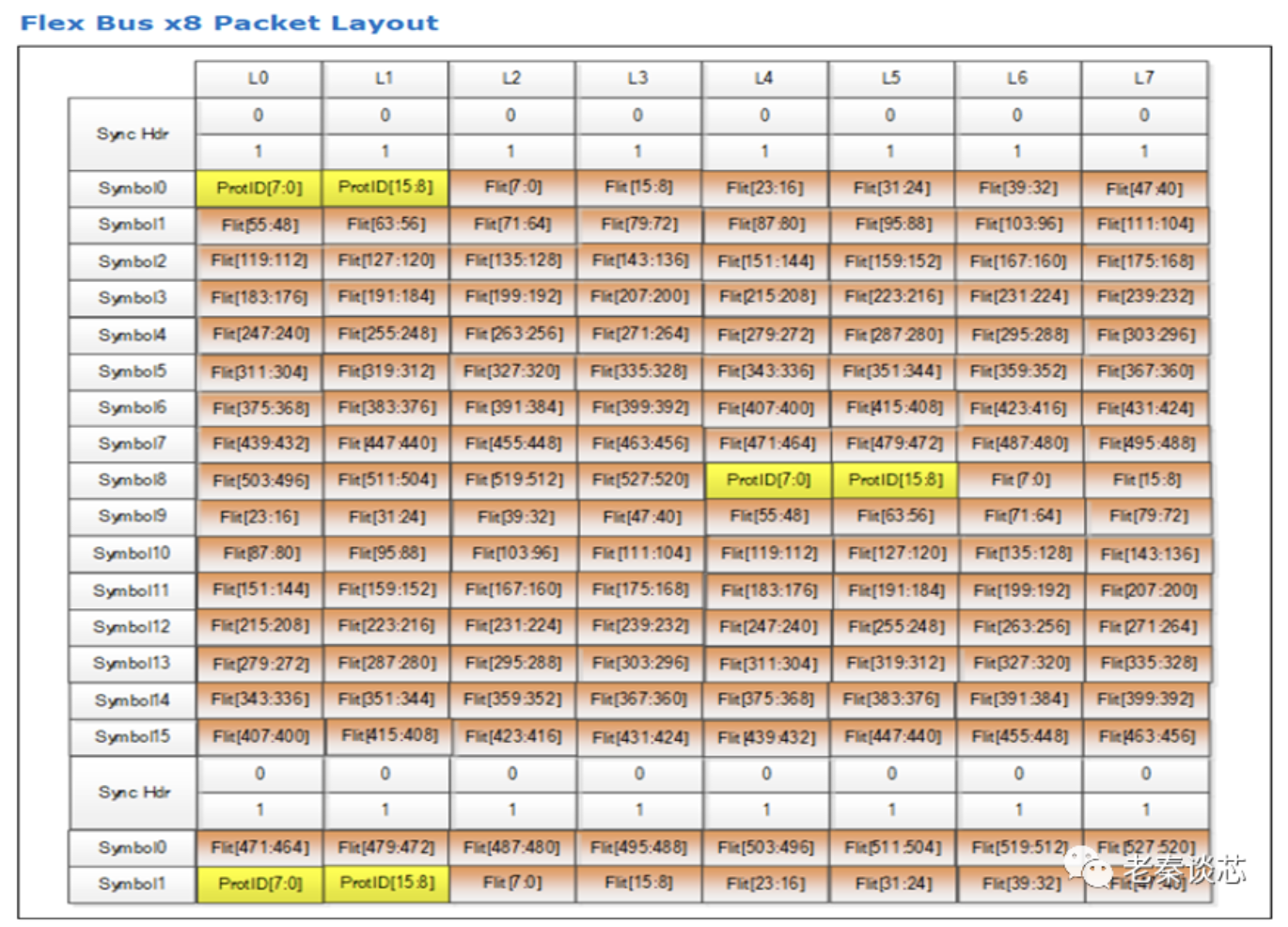

6.2.4 x8數(shù)據(jù)包

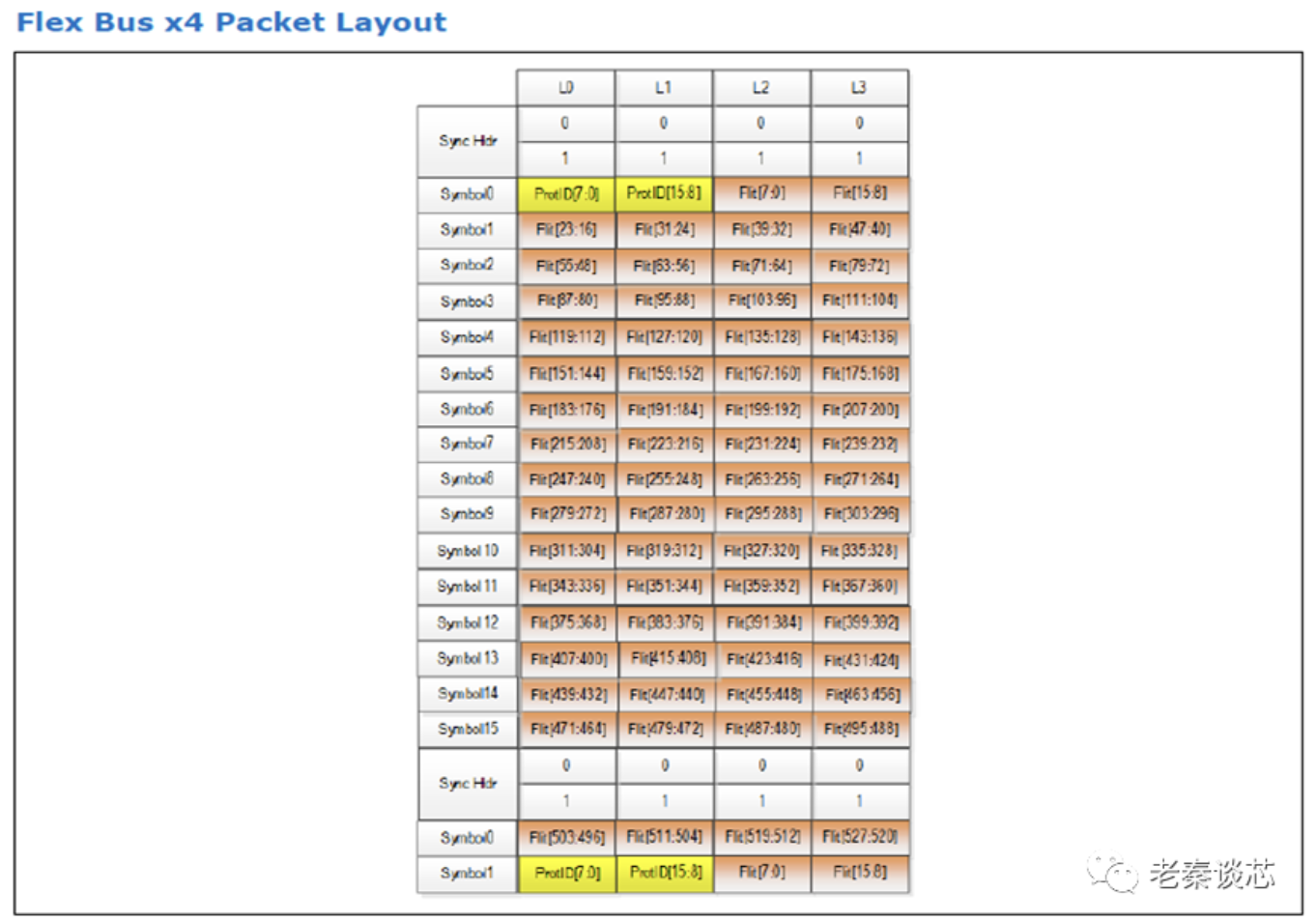

6.2.5 x4數(shù)據(jù)包

6.2.6 x2數(shù)據(jù)包

x2數(shù)據(jù)包布局與x4數(shù)據(jù)包布局非常相似,協(xié)議ID與通道0對(duì)齊。16-bit協(xié)議ID和528-bit flit以8-bit粒度在兩條Lane上傳輸。

6.2.7 x1數(shù)據(jù)包

x1數(shù)據(jù)包布局僅在降級(jí)模式下使用。16-bit協(xié)議ID后跟528-bit flit在一條Lane上傳輸。

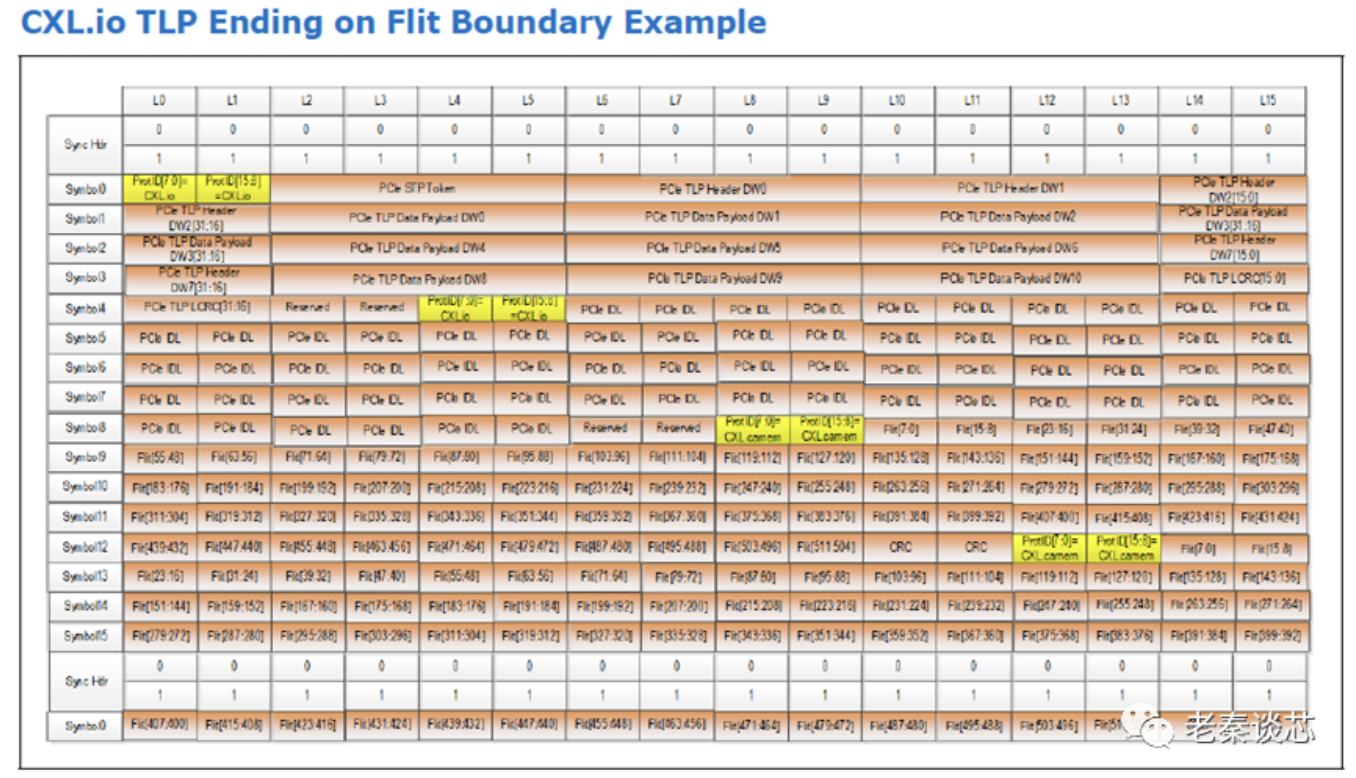

6.2.8 特殊情況:CXL.io – 何時(shí)TLP在Flit邊界上結(jié)束

對(duì)于CXL.io,如果TLP在flit邊界上結(jié)束,且沒(méi)有額外的CXL.io數(shù)據(jù)包要發(fā)送,但接收端仍然需要隨后的EDB(EnD Bad)指示,或IDLE flit,或DLLP,以在處理TLP之前確認(rèn)此TLP是完好的還是無(wú)效的。

下圖展示了這種場(chǎng)景,第一個(gè)CXL.io flit剛好封裝了一個(gè)TLP。為保證接收端正確處理,發(fā)送端需要在發(fā)送一個(gè)包含PCIe IDLE令牌的CXL.io flit。

6.2.9 幀錯(cuò)誤

物理層負(fù)責(zé)檢測(cè)幀錯(cuò)誤,并隨后啟動(dòng)Recovery以重新訓(xùn)練鏈路。以下是物理層檢測(cè)到的幀錯(cuò)誤:

- 同步頭錯(cuò)誤

- 協(xié)議ID幀錯(cuò)誤

- EDS插入錯(cuò)誤

- 528-bit的CXL.io flit中存在PCIe幀錯(cuò)誤

6.3 鏈路訓(xùn)練

6.3.1 PCIe vs Flex Bus.CXL

當(dāng)LTSSM從Detect狀態(tài)退出后,F(xiàn)lex Bus鏈路開(kāi)始訓(xùn)練,并根據(jù)PCIe LTSSM規(guī)則完成鏈路寬度協(xié)商和速度協(xié)商。在鏈路訓(xùn)練期間,下游端口通過(guò)PCIe備用模式協(xié)商機(jī)制啟動(dòng)Flex Bus模式協(xié)商。在以2.5 GT/s的速度進(jìn)入L0之前,完成Flex Bus模式協(xié)商。

Flex Bus模式的動(dòng)態(tài)硬件協(xié)商發(fā)生在LTSSM的Configuration狀態(tài)下的鏈路訓(xùn)練期間,通過(guò)交換PCIe 5.0基本規(guī)范定義的Modified TS1和TS2有序集來(lái)促進(jìn)。

6.4 Recovery.Idle和Config.Idle轉(zhuǎn)換到L0

PCIe規(guī)范要求從Recovery.Idle切換到L0,或從Config.Idle切換到L0,鏈路雙方需要傳輸和接收特定數(shù)量的連續(xù)空閑數(shù)據(jù)符號(hào)。當(dāng)Flex Bus的邏輯PHY處于CXL模式時(shí),會(huì)監(jiān)測(cè)NULL flits而不是空閑字符來(lái)啟動(dòng)到L0的轉(zhuǎn)換。當(dāng)處于CXL模式下Recovery.Idle或Config.Idle時(shí),如果接收到四個(gè)連續(xù)的NULL flit并且在接收到一個(gè)NULL flit之后發(fā)送了八個(gè)NULL flit時(shí),則下一個(gè)狀態(tài)為L(zhǎng)0。

第七章 交換機(jī)(Switching)

7.1 概覽

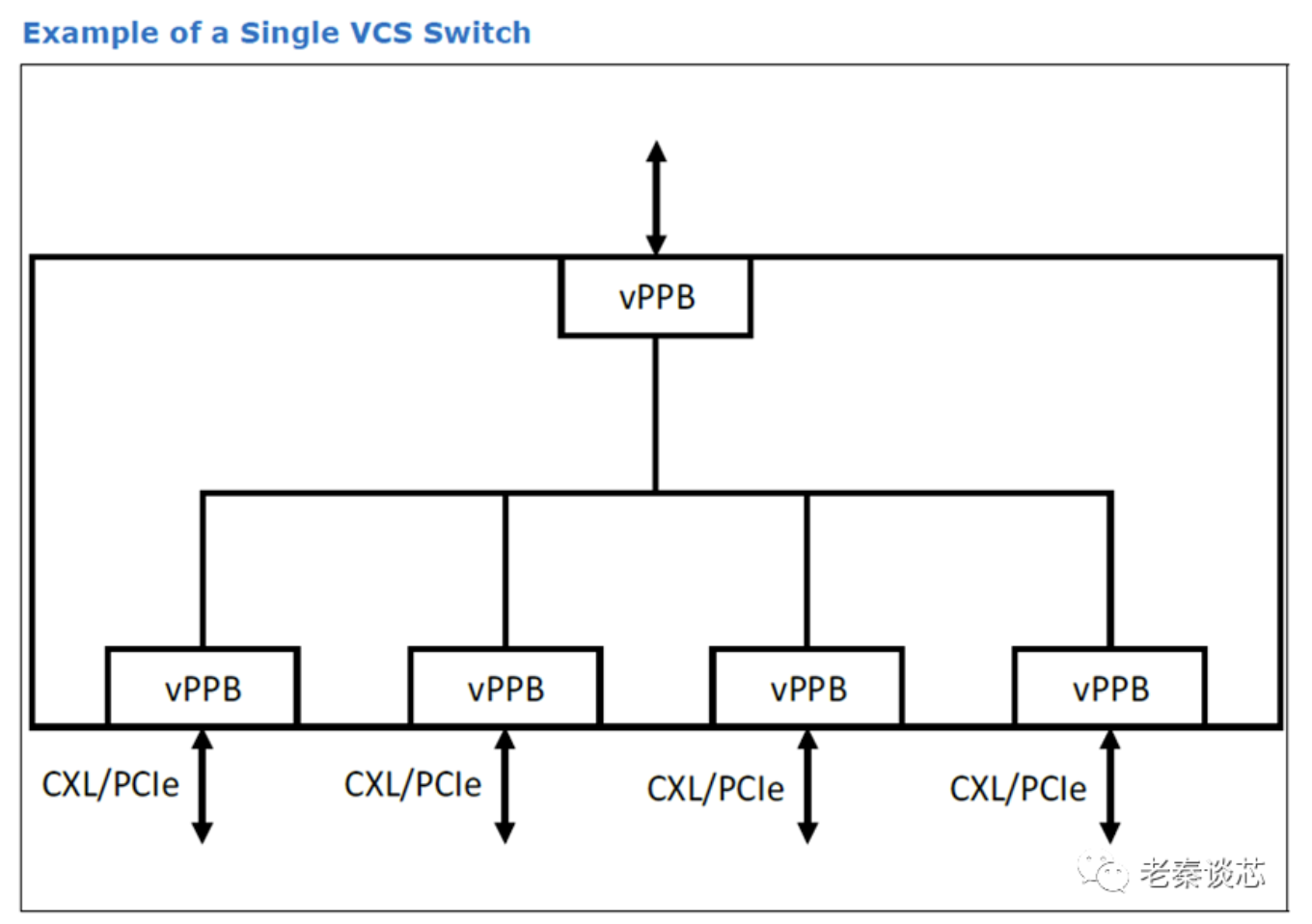

7.1.1 單VCS(Virtual CXL Switch)交換機(jī)

圖中的vPPB是virtual PCI-to-PCI bridge。單VCS交換機(jī)指的是有一個(gè)上游端口,若干個(gè)下游端口。單VCS交換機(jī)須遵守規(guī)則:

- 必須有一個(gè)上游端口(Upstream Switch Port,USP)

- 必須有一個(gè)或多個(gè)下游端口(Downstream Switch Port,DSP)

- DSP必須支持PCIe模式和CXL模式

- 所有non-MLD(包括PCIe和SLD)端口都支持vPPB下的單個(gè)虛擬層次結(jié)構(gòu)

- DSP必須能夠支持CXL 1.1鏈路

- 必須支持CXL 2.0擴(kuò)展DVSEC

- DVSEC定義了寄存器,支持CXL.io解碼和CXL.mem解碼

- Fabric Manager是可選的

解釋一下,F(xiàn)abric Manager是一個(gè)獨(dú)立于交換機(jī)或主機(jī)固件的實(shí)體,它控制與端口和設(shè)備的綁定和管理相關(guān)的系統(tǒng)方面。

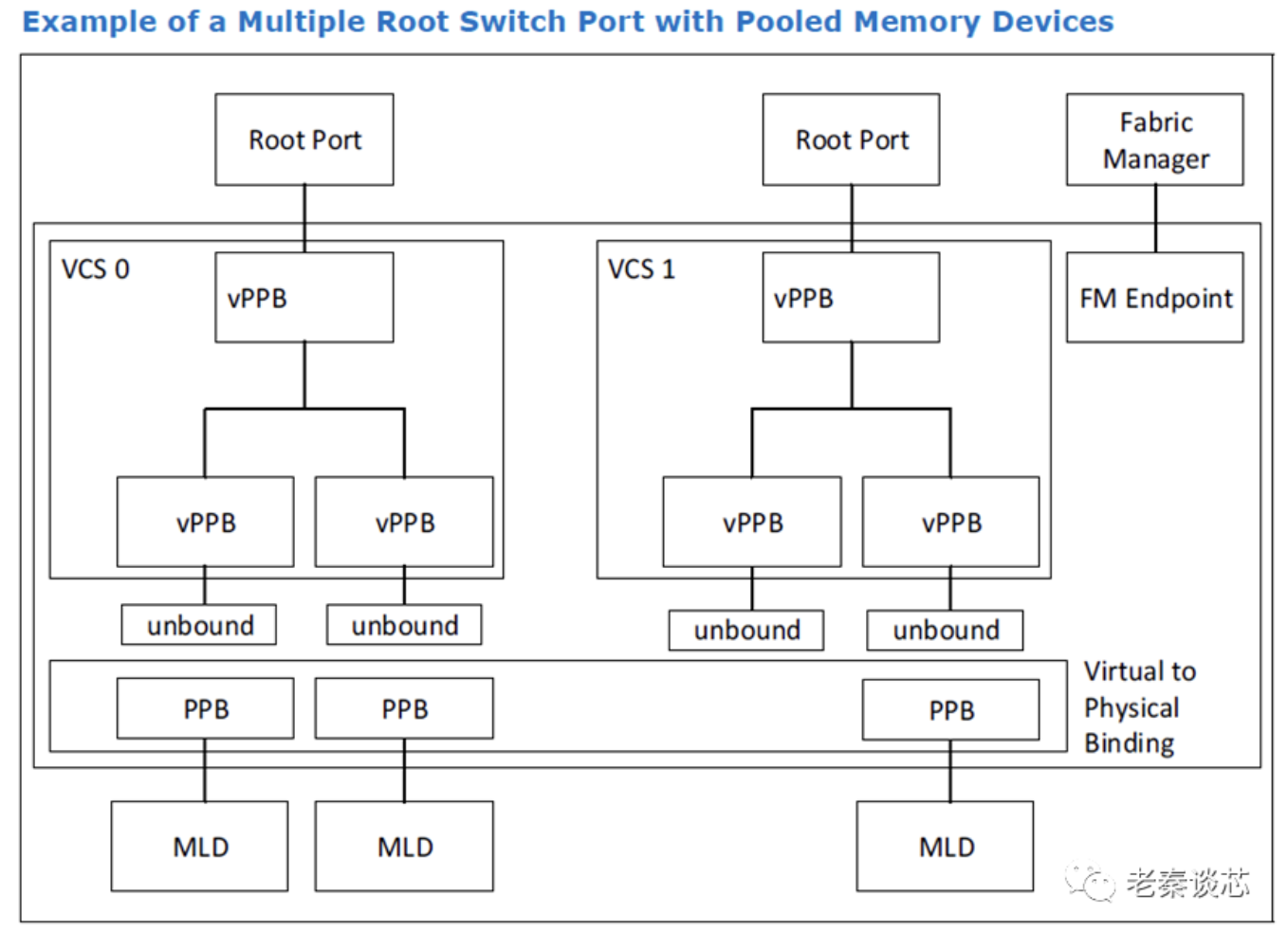

7.1.2 多VCS(Virtual CXL Switch)交換機(jī)

多VCS交換機(jī)須遵守規(guī)則:

- 多于1個(gè)USP

- 每個(gè)VCS有一個(gè)或多個(gè)DSP

- 上游vPPB到物理端口的綁定和VCS的結(jié)構(gòu)取決于交換機(jī)供應(yīng)商具體實(shí)現(xiàn)

- 每個(gè)DSP必須綁定到PPB或vPPB

- Fabric Manager是可選的

- 配置時(shí),每個(gè)USP及其關(guān)聯(lián)的DSP形成一個(gè)VCS交換機(jī)

- DSP必須支持在CXL或PCIe操作模式下運(yùn)行。

- 所有non-MLD端口都支持下游交換機(jī)端口下方的單個(gè)虛擬層次結(jié)構(gòu)。

- DSP必須能夠支持CXL 1.1鏈路

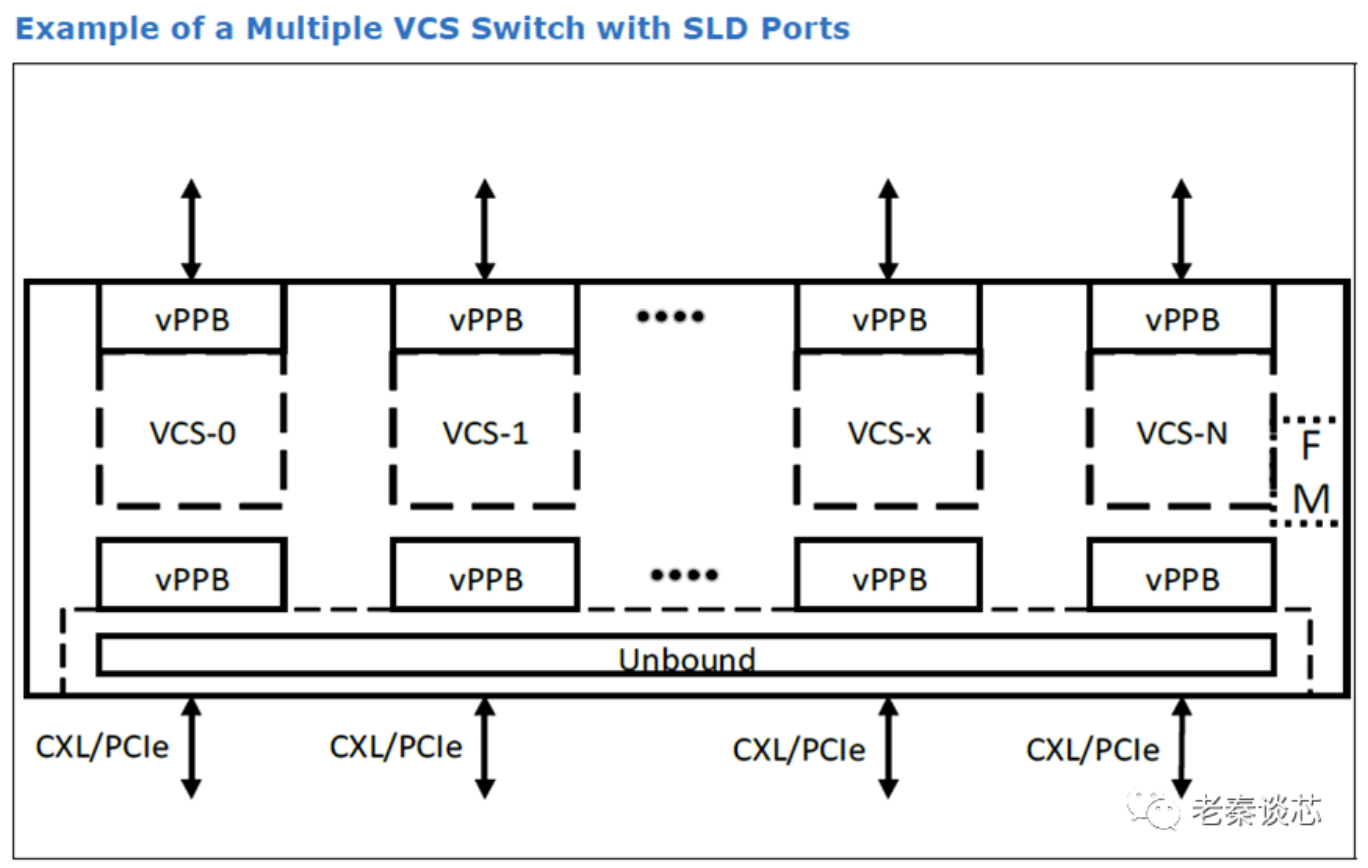

7.1.3 具有MLD端口的多VCS交換機(jī)

具有MLD端口的多VCS交換機(jī)由多個(gè)上游端口交換機(jī)和一個(gè)或多個(gè)下游MLD端口的組合組成。

具體規(guī)則不再列出。

7.2 交換機(jī)配置和組成

7.2.1 CXL交換機(jī)初始化選項(xiàng)

CXL交換機(jī)三種初始化方法:

1.靜態(tài)

2.FM在主機(jī)前啟動(dòng)

3.FM和主機(jī)同時(shí)啟動(dòng)

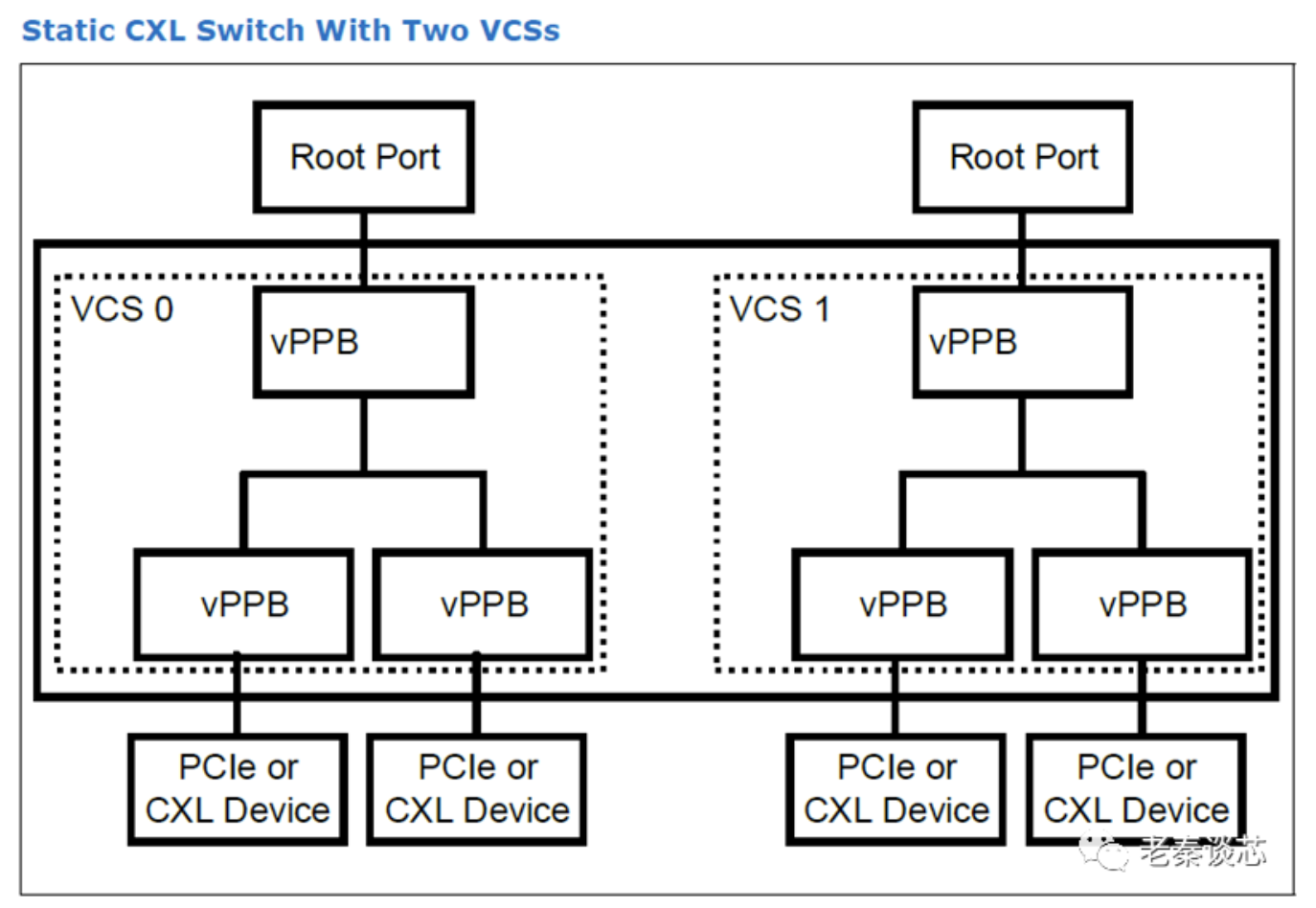

7.2.1.1 靜態(tài)初始化

下圖是靜態(tài)初始化的例子,下游vPB靜態(tài)綁定到端口,使用標(biāo)準(zhǔn)的PCIe機(jī)制支持設(shè)備熱插拔。

靜態(tài)交換機(jī)特性:

- 不支持MLD端口

- 不支持將端口重新綁定到不同的VCS

- 不需要FM

- 在交換機(jī)啟動(dòng)時(shí),使用特定的機(jī)制(例如SPI閃存中的配置文件)靜態(tài)配置所有VCS和下游端口綁定

- 支持CXL 1.1、CXL 2.0或PCIe下游端口

- VCS(包括vPBs)的行為與PCIe交換機(jī)相同,同時(shí)添加了對(duì)CXL協(xié)議的支持

- 當(dāng)主機(jī)啟動(dòng)時(shí),每個(gè)VCS都準(zhǔn)備好進(jìn)行枚舉

- 支持熱插拔

- 不支持異步移除CXL 2.0設(shè)備

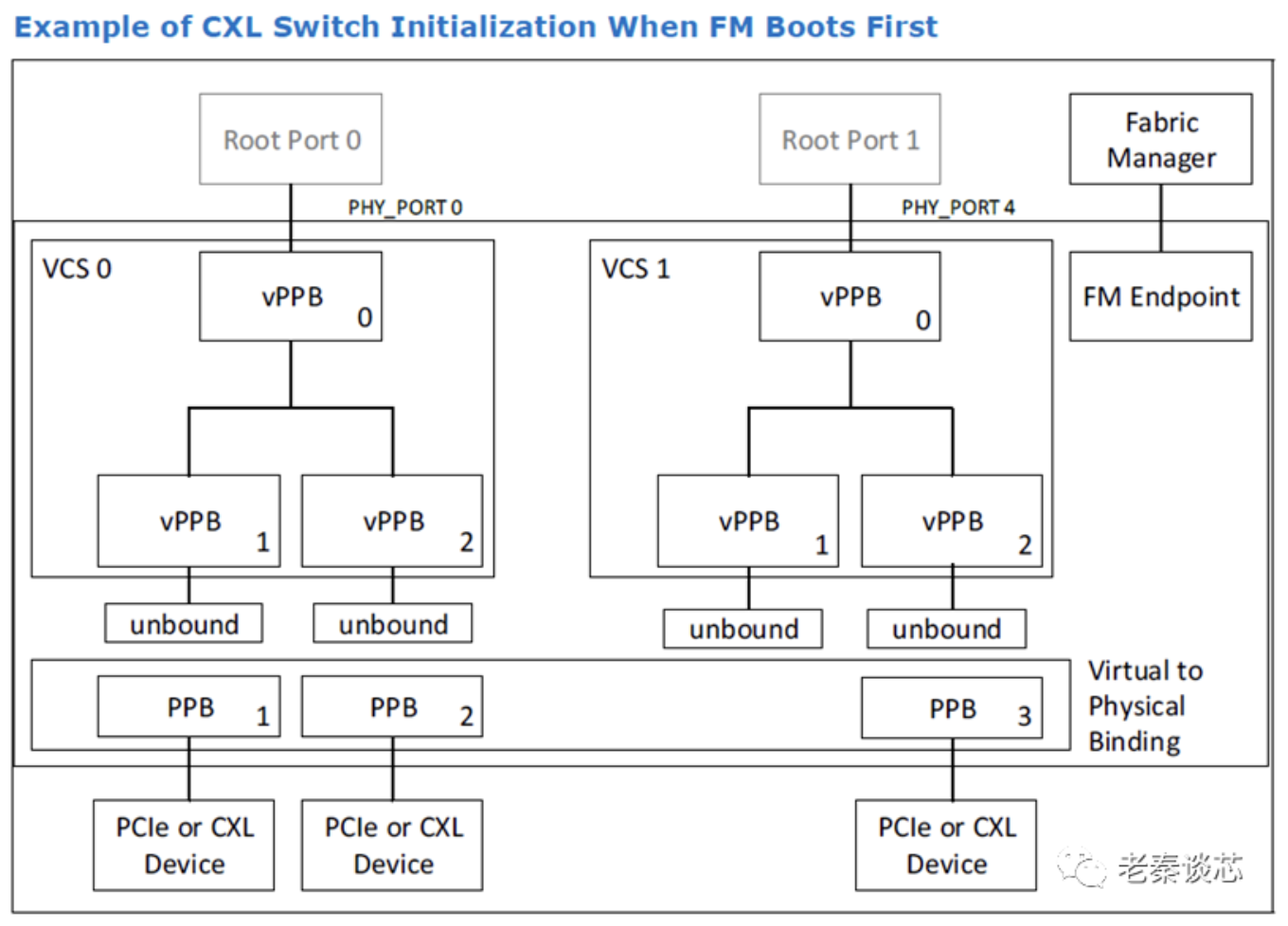

7.2.1.2 FM先啟動(dòng)

在FM先于主機(jī)啟動(dòng)的情況下,允許按照以下示例所述初始化交換機(jī)。

- Switch和FM啟動(dòng)

- 在本例中,下游vPPB靜態(tài)綁定到端口,使用標(biāo)準(zhǔn)PCIe機(jī)制支持設(shè)備的熱插拔

- 所有下游端口都沒(méi)有綁定到VCS,它們歸FM所有

- DSP鏈路建立,交換機(jī)通知FM

- FM向交換機(jī)發(fā)送BIND命令(VCS0、VPPB1、PHY_PORT_ID1)。交換機(jī)配置虛擬到物理綁定,如項(xiàng)中所述

- 交換機(jī)將vPPB虛擬端口號(hào)重新映射為物理端口號(hào)

- 交換機(jī)將vPPB連接器定義(PERST#、PRSNT#)重新映射到物理連接器

- 交換機(jī)禁用鏈路

- 所有物理的下游PPB功能都直接映射到vPPB

- FM擁有的PPB不再存在于該端口

- 當(dāng)主機(jī)啟動(dòng)時(shí),交換機(jī)已準(zhǔn)備好進(jìn)行枚舉。

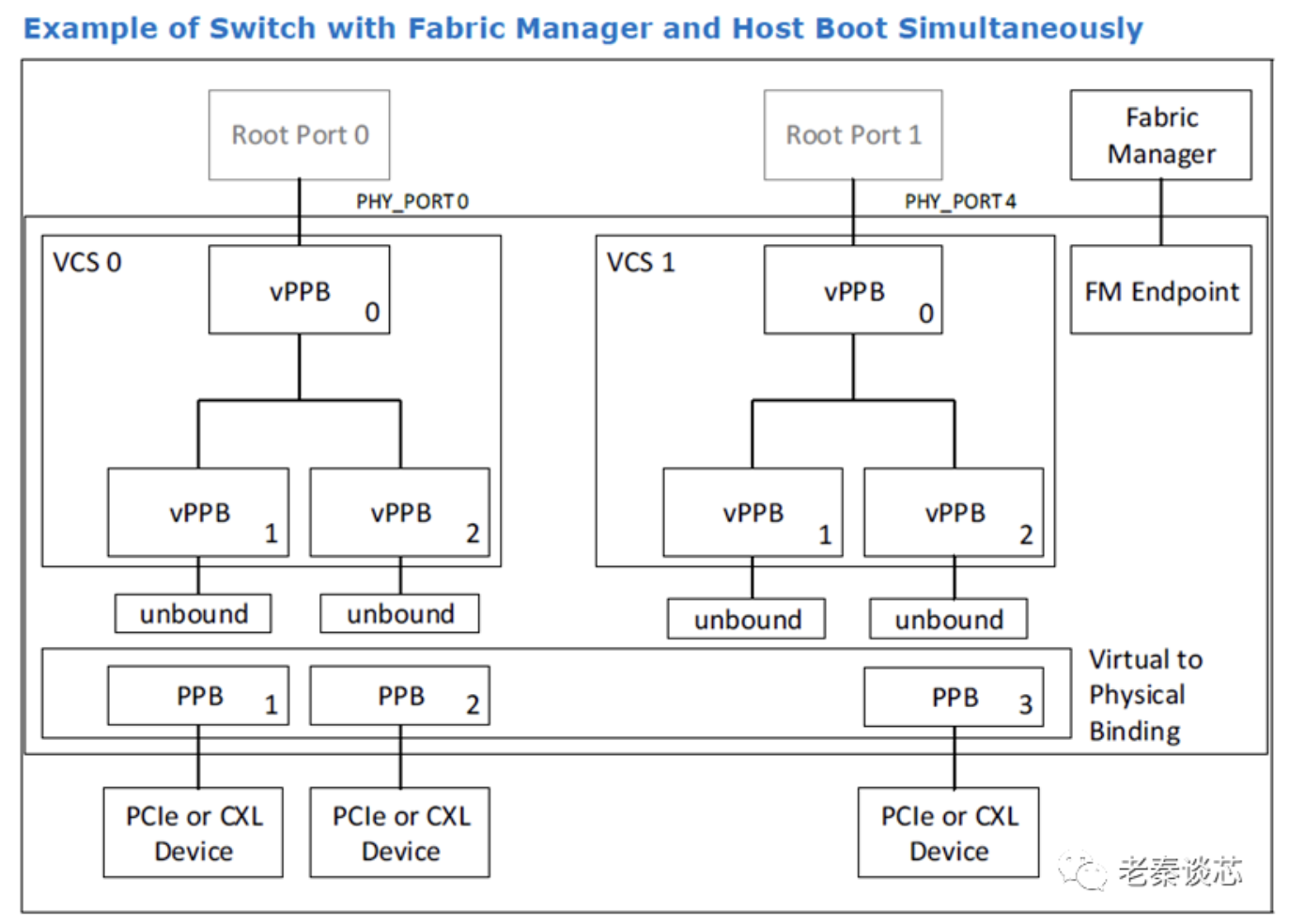

7.2.1.3 FM和主機(jī)同時(shí)啟動(dòng)

FM和主機(jī)同時(shí)啟動(dòng):

1.VCS是靜態(tài)定義的

2.每個(gè)VCS內(nèi)的vPPB被解除綁定,并作為鏈路斷開(kāi)呈現(xiàn)給主機(jī)

3.交換機(jī)發(fā)現(xiàn)下游設(shè)備并將其呈現(xiàn)給FM

4.主機(jī)枚舉VH并在上游PPB中配置DVSEC

5.FM執(zhí)行到vPPB的端口綁定

6.交換機(jī)執(zhí)行虛擬到物理的綁定

7.每個(gè)被綁定的端口都產(chǎn)生對(duì)主機(jī)的熱添加指示

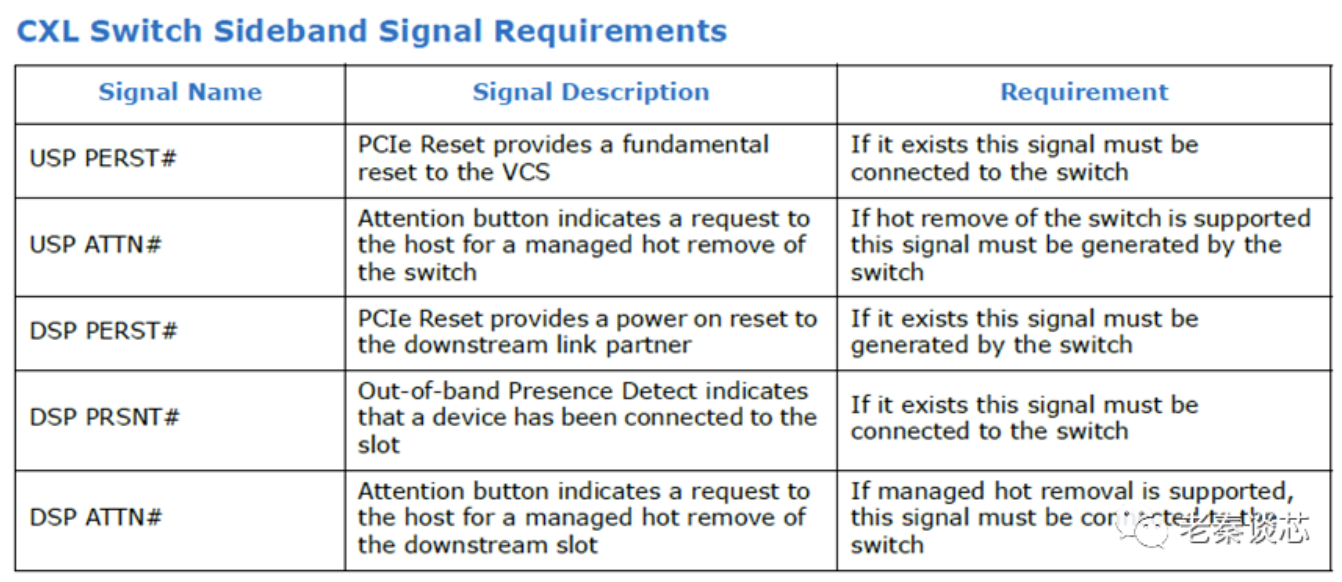

7.2.2 邊帶信號(hào)操作

下表表提供了支持熱插拔的最小邊帶信號(hào)集,其它邊帶信號(hào)可選。這些邊帶信號(hào)的行為與PCIe協(xié)議中定義的一致。

7.2.3 綁定和解綁

本節(jié)是關(guān)于CXL設(shè)備到vPPB的綁定和解綁。

7.2.4 MLD端口PPB和vPPB行為

MLD端口提供虛擬化接口,以便多個(gè)vPPB可以通過(guò)共享物理接口訪問(wèn)LDs。因此,綁定到MLD端口的vPPB的特性和行為與綁定到SLD端口的vPPB的特性和行為不同。本節(jié)定義了它們之間的區(qū)別。

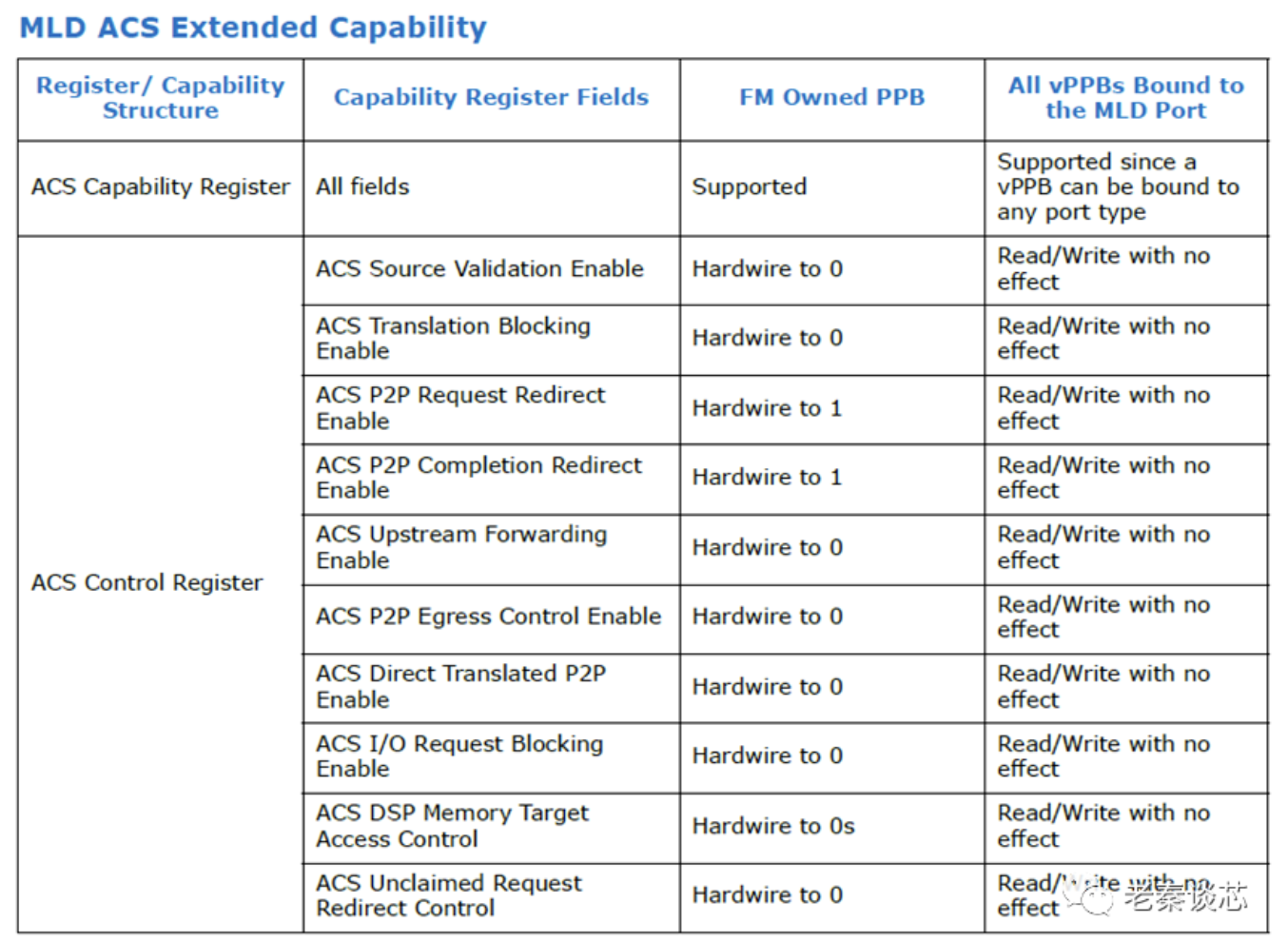

7.2.5 MLD ACS擴(kuò)展功能

CXL.io的請(qǐng)求事務(wù)和完成事務(wù)被路由到USP。

7.2.6 MLD PCIe擴(kuò)展功能

vPPB的PCIe擴(kuò)展能力結(jié)構(gòu)(Capability Structure)中的所有字段的行為應(yīng)與PCIe相同,但以下小結(jié)中的情況除外。

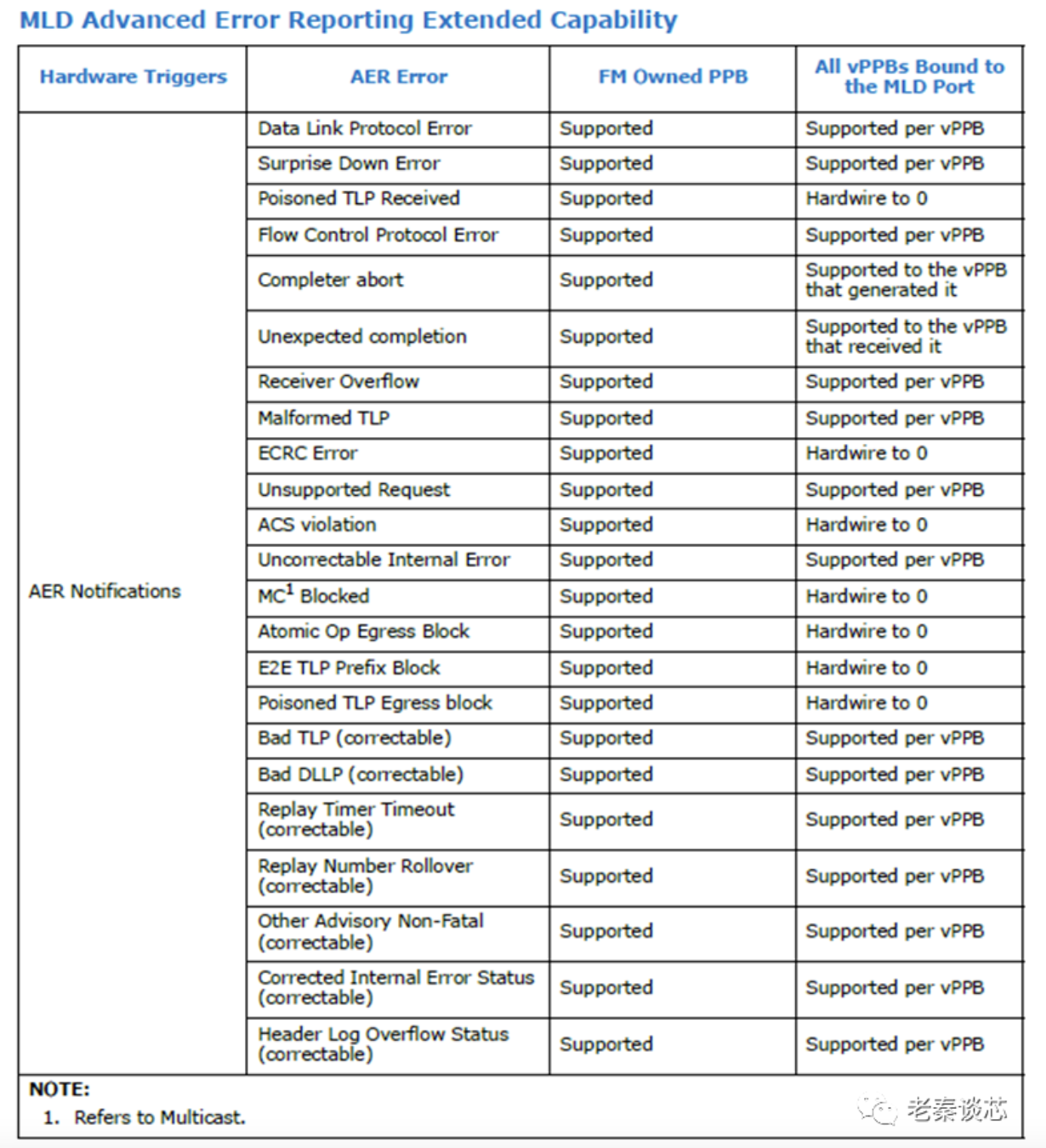

7.2.7 MLD AER(Advanced Error Reporting)擴(kuò)展功能

MLD端口中的AER分為Triggering、Notification和Reporting。

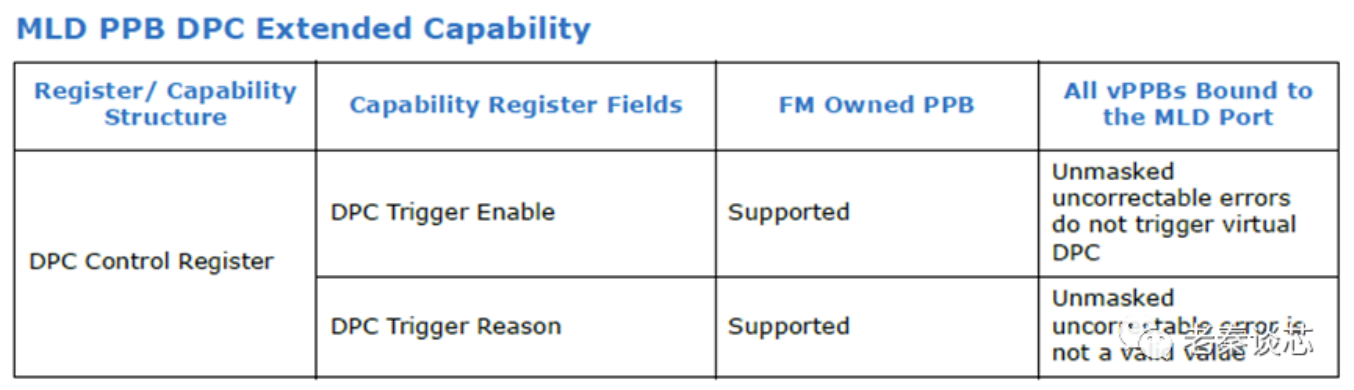

7.2.8 MLD DPC擴(kuò)展功能

7.3 CXL.io, CXL.cache/CXL.mem解碼和轉(zhuǎn)發(fā)

7.3.1 CXL.io

在VCS中,CXL.io流量必須遵守PCI Express規(guī)范中定義的交換機(jī)的相同請(qǐng)求、完成、地址解碼和轉(zhuǎn)發(fā)規(guī)則。

7.3.1.1 CXL.io解碼

當(dāng)TLP由PPB解碼時(shí),它根據(jù)PCIe基本規(guī)范中定義的規(guī)則,確定要路由TLP的目標(biāo)PPB。除非另有規(guī)定,PCIe基本規(guī)范中定義的所有規(guī)則都適用于CXL.io TLP的路由。

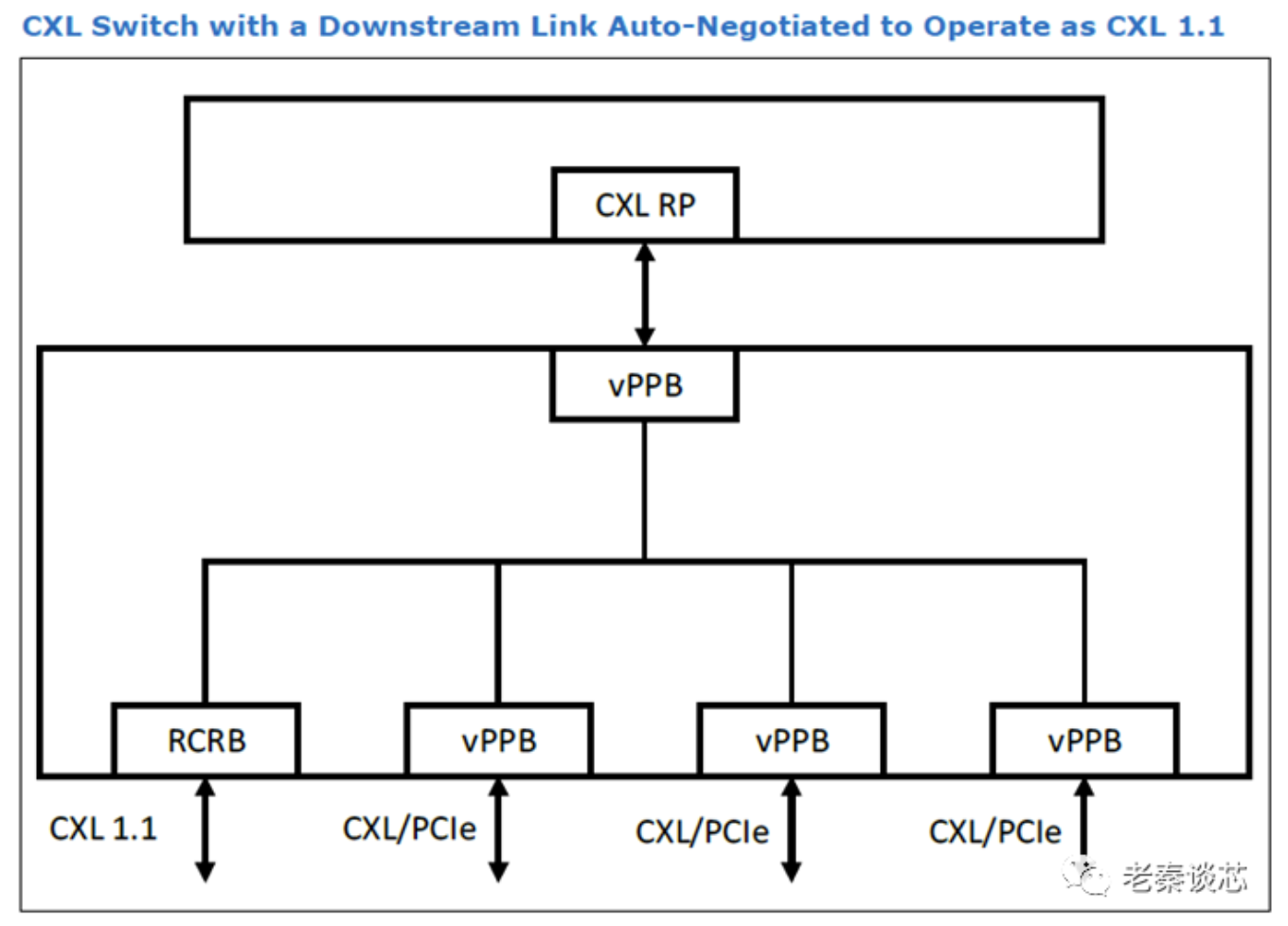

7.3.1.2 CXL 1.1 支持

FM擁有的PPB端口不支持CXL 1.1設(shè)備。CXL 1.1設(shè)備連接到交換機(jī)的話,在軟件中必須顯示為RCiEP設(shè)備。

7.3.2 CXL.cache

僅允許啟用VCS中的一個(gè)CXL SLD端口來(lái)支持Type 1或Type 2設(shè)備。USP上接收到的請(qǐng)求和響應(yīng)被路由到相關(guān)的DSP,反之亦然。因此,CXL.cache不需要額外的解碼寄存器。

7.3.3 CXL.mem

HDM解碼DVSEC功能包含定義內(nèi)存地址解碼范圍的寄存器。CXL.mem請(qǐng)求來(lái)自主機(jī)/RP,并通過(guò)交換機(jī)向下游流向設(shè)備,響應(yīng)來(lái)自設(shè)備,并向上游流向RP。

7.3.4 FM Owned PPB CXL Handling

暫時(shí)略過(guò)。

7.4 CXL交換機(jī)電源管理(PM)

7.4.1 CXL Switch ASPM L1

對(duì)ASPM L1的支持在第十章中描述。

ASPM(Active State Power Management)是PCIe協(xié)議中的一種硬件電源管理機(jī)制。

7.4.2 CXL Switch PCI-PM and L2

VCS中的vPPB對(duì)PME消息的處理規(guī)則與PCIe vPPB相同。

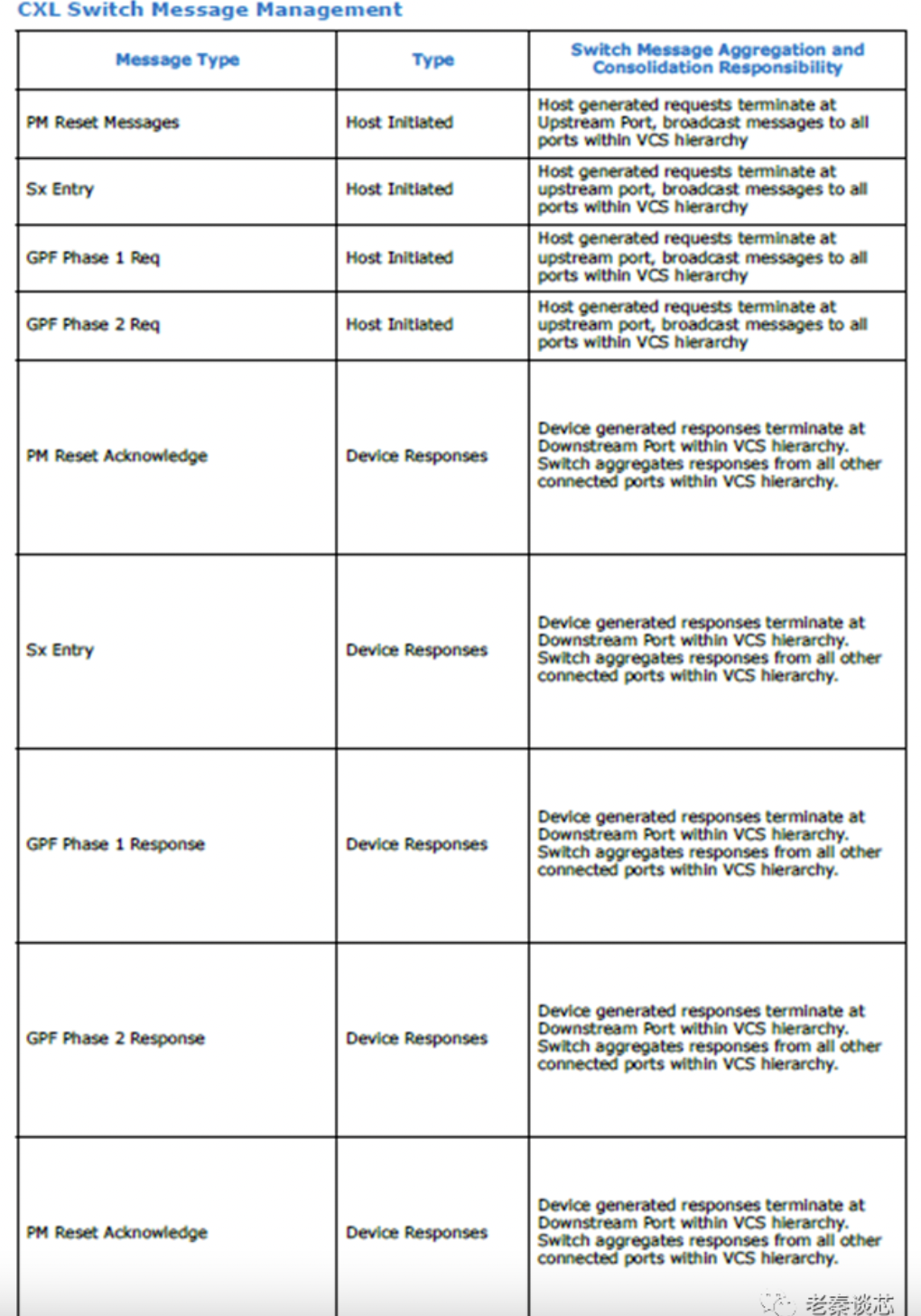

7.4.3 CXL Switch Message Management

CXL VDM屬于“Local – Terminate at Receiver”類型。當(dāng)層次結(jié)構(gòu)中存在交換機(jī)時(shí),該交換機(jī)實(shí)現(xiàn)消息聚合功能。所有主機(jī)生成的消息都終止于該交換機(jī),交換機(jī)聚合功能負(fù)責(zé)向下游端口重新生成這些消息。CXL設(shè)備生成的所有消息和響應(yīng)都由交換機(jī)聚合和合并,合并后的消息或響應(yīng)由交換機(jī)的上游端口生成,發(fā)送給主機(jī)。

PM消息信用交換發(fā)生在主機(jī)和交換機(jī)聚合端口之間,并且分別發(fā)生在交換機(jī)聚合端口和設(shè)備之間。

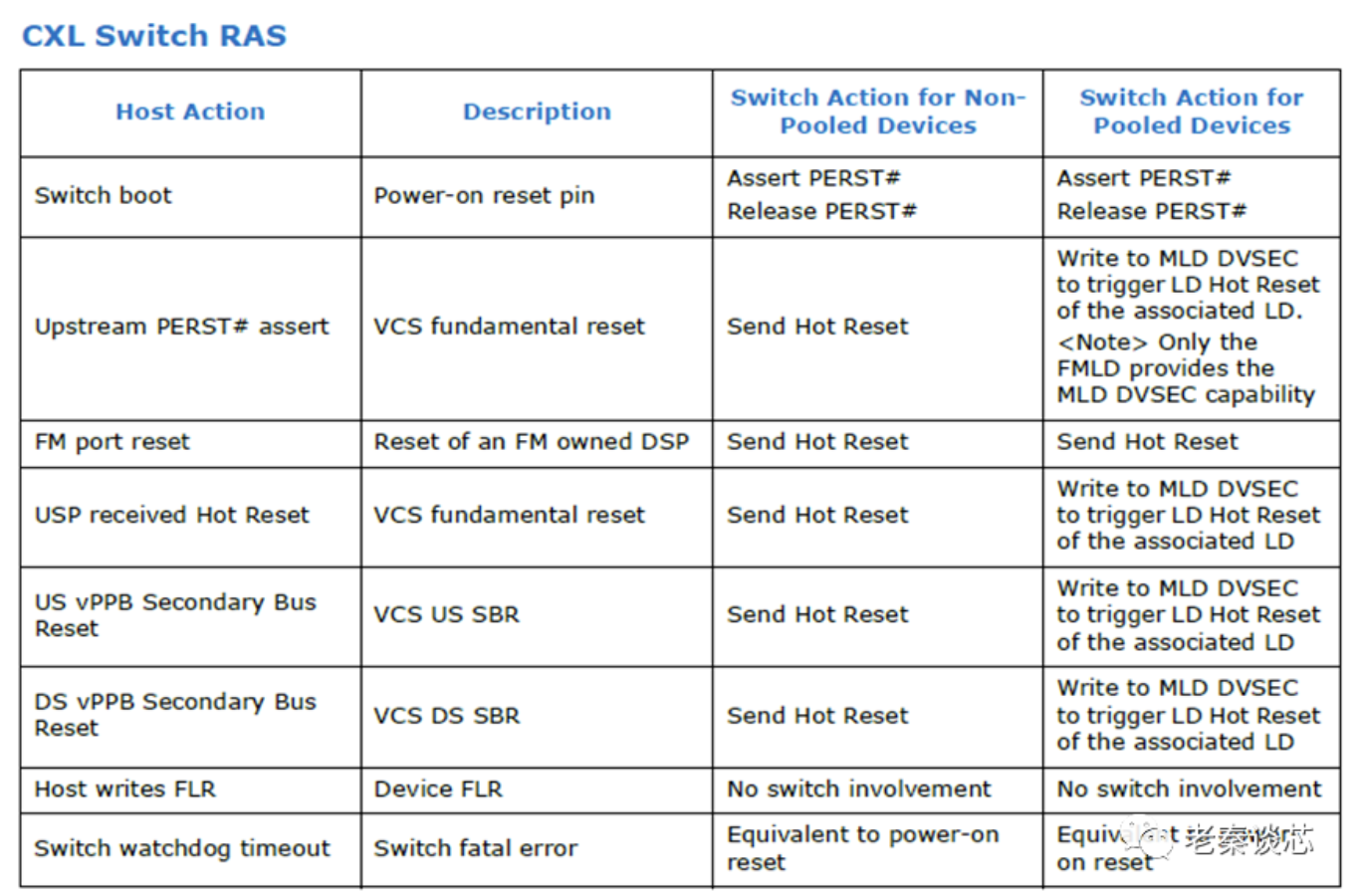

7.5 CXL交換機(jī)RAS

7.6 Fabric Manager應(yīng)用程序編程接口

暫時(shí)略過(guò),留給軟件開(kāi)發(fā)人員去頭疼吧。

總結(jié):本章中的很多概念是基于PCIe基本規(guī)范的,不過(guò)在PCIe基本規(guī)范中并沒(méi)有專門為Switch設(shè)立一章。但是在CXL協(xié)議中,Switch承擔(dān)了很多事情。

-

連接器

+關(guān)注

關(guān)注

99文章

15390瀏覽量

140593 -

交換機(jī)

+關(guān)注

關(guān)注

22文章

2747瀏覽量

101940 -

DSP芯片

+關(guān)注

關(guān)注

9文章

153瀏覽量

30755 -

PHY寄存器

+關(guān)注

關(guān)注

0文章

6瀏覽量

5420 -

PCIe接口

+關(guān)注

關(guān)注

0文章

121瀏覽量

10135

發(fā)布評(píng)論請(qǐng)先 登錄

分析802.11標(biāo)準(zhǔn)在物理層的定義

無(wú)線網(wǎng)絡(luò)物理層借口操作與功能

CAN總線不同的物理層

什么是以太網(wǎng)物理層?Ethernet物理層有哪些功能?

一窺CXL協(xié)議

WCDMA系統(tǒng)的物理層(FDD)

物理層 PPT課件

物理層的作用

WiMAX(IP-OFDMA)的物理層參數(shù)和幀結(jié)構(gòu)

3GPP LTE物理層概述

WLAN物理層關(guān)鍵通信技術(shù)

Flex Bus物理層的CXL幀和數(shù)據(jù)概述

Flex Bus物理層的CXL幀和數(shù)據(jù)概述

評(píng)論