板子lay的好,ESD沒煩惱。提高ESD靜電防護,PCB設計需要做好以下幾點:

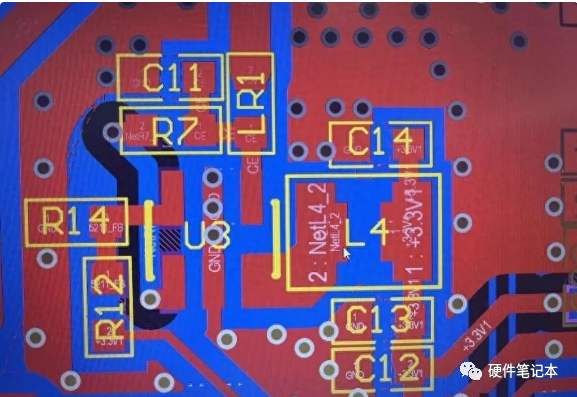

對于電源布局的整改,如圖1所示:

圖1

1、DCDC電源布局,在電壓輸出端經過電感,旁路電容和儲能電容的布局如上圖,旁路電容C14、C13盡量靠近電感輸出,取電壓最好是經過電容C12后取電。目的是電路可更好濾波,減少干擾。

2、所有通過電源線、信號線上的高頻旁路電容都盡量就近接地,以減小進入電路系統的ESD大電流,起到更好的吸收干擾的作用。

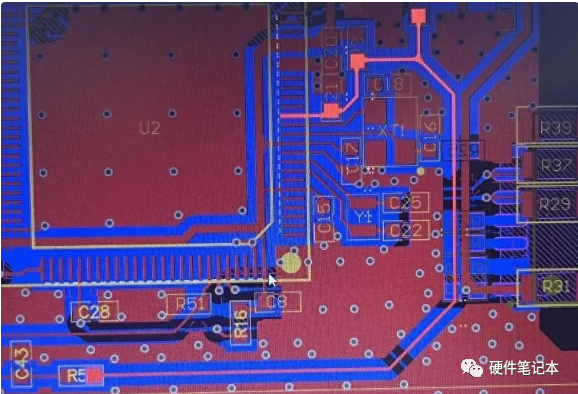

3、復位線、恢復出廠信號線要盡可能短。因為越長的走線就越難承受ESD能量,故元器件的布局盡可能湊近以減短走線長度。若實在無法避免,線的兩邊盡量有地包裹,如圖2所示。(感謝關注微信公眾號:硬件筆記本)目的是減少其他信號干擾,避免受到干擾使芯片無故重啟。同時也可在電路上加電容或電阻,可增大內阻,防止過大的干擾信號。

圖2

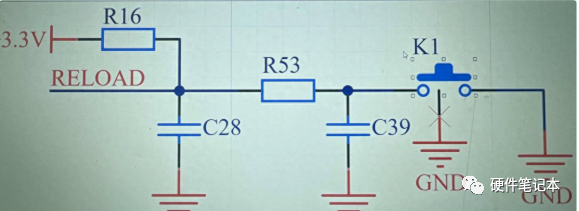

4、開關復位線布局也是同樣的原理,在電路上可加上一個π型濾波電路,如下圖圖3所示,可更好的消除外界干擾,防止芯片重置。

圖3

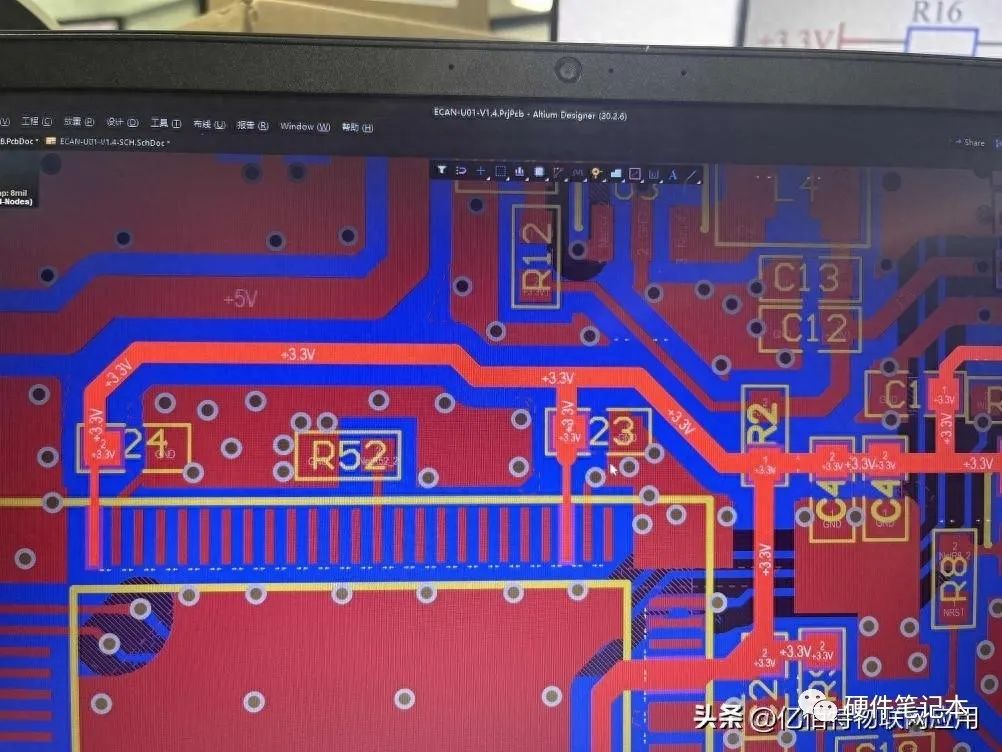

5、給芯片供電,電源走線盡量是先通過電容再流向芯片,對芯片起到保護作用。如圖4所示。

圖4

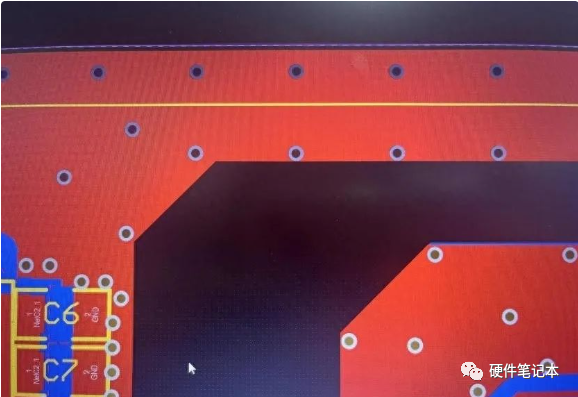

6、地線鋪銅盡量避免直角。盡量使用拐角大于90°,直角尖會產生干擾,會導致放電路徑不一致。如圖5所示。

圖5

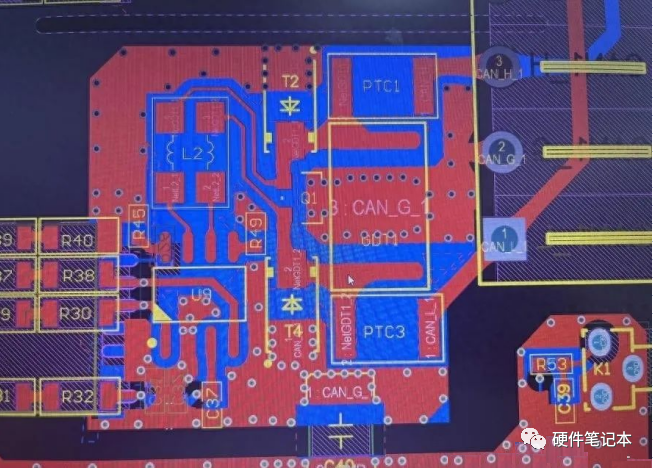

7、通訊線先經過保護器件,再經過防雷管放電,防雷管就近接地,再經過TVS放電。線盡量短,回路盡可能小,可快速消除干擾信號。(感謝關注微信公眾號:硬件筆記本)在地線上加上Y電容,可快速放電,消除靜電。

圖6

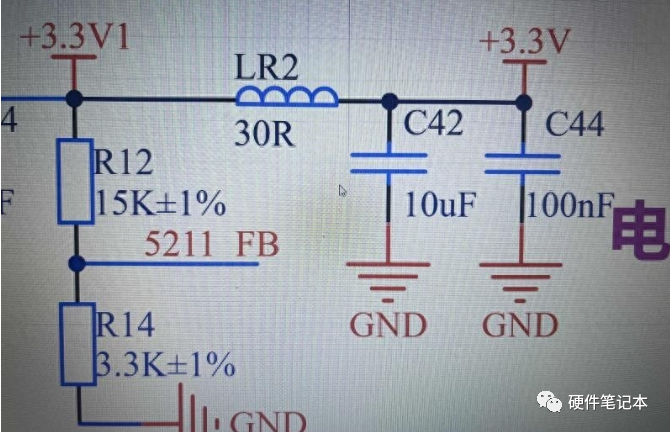

8、MCU和其他芯片可以分開取電,避免相互干擾,可在電路上加LC濾波電路。電路如圖所示:

圖7

9、也可使用多層板。多層板可大大改善系統抵抗ESD放電的能力。將第一層接地平面盡可能靠近信號走線層,可使用ESD瞬態放電在到達走線時能很快抵消。

10、加隔離。電氣隔離也是抑制靜電放電沖擊的一種方法。在PCB上加隔離芯片或者光耦、變壓器等,以及結合截止隔離和屏蔽可以很好抑制靜電放電沖擊。

總的來說,關于防止ESD靜電干擾的設計,電源平面、接地平面和信號線的布局是PCB ESD防護設計的重要措施之一。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2250瀏覽量

174861 -

pcb

+關注

關注

4345文章

23350瀏覽量

405621 -

DCDC

+關注

關注

29文章

862瀏覽量

72548 -

靜電防護

+關注

關注

11文章

203瀏覽量

47803

原文標題:板子lay的好,ESD沒煩惱

文章出處:【微信號:gh_a6560e9c41d7,微信公眾號:硬件筆記本】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何提高ESD靜電防護 PCB ESD防護設計的重要措施

如何提高ESD靜電防護 PCB ESD防護設計的重要措施

評論