一個(gè)有意思的題目。

X為一個(gè)32-bit的數(shù),那么 X+32 和 X+1,哪個(gè)消耗的資源更多?還是一樣多?

假如只允許用 LUT 實(shí)現(xiàn)

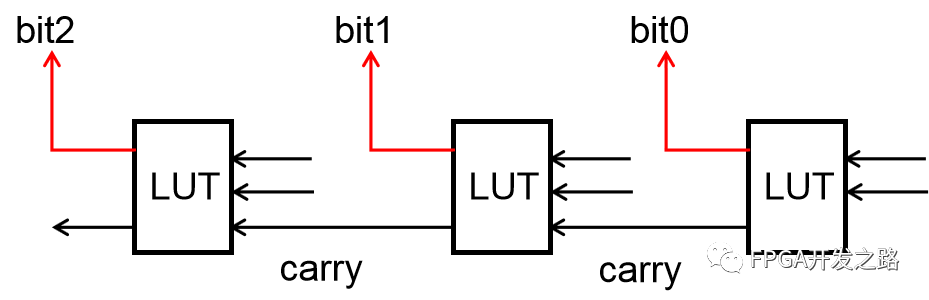

如圖1所示每個(gè)LUT可以完成1bit的加法,同時(shí)產(chǎn)生進(jìn)位(Xilinx LUT6可以有兩個(gè)輸出)。因此對(duì)于32bit的加法,則需要32個(gè)LUT。

圖1

假如我們要實(shí)現(xiàn)的是 A+B,A和B都是32-bit的,那么確實(shí)是需要32個(gè)LUT。那X+32和X+1的常數(shù)加法呢?

32可以表示為32'b0000...0010_0000,1可以表示為32'b0000....0000_0001。

對(duì)于 X+32,輸出值的低5bit可以直接表示為X[5:0],不需要LUT,其余值需要27個(gè)LUT實(shí)現(xiàn)加法運(yùn)算。

對(duì)于X+1,只能從bit 0開始相加計(jì)算進(jìn)位,總共需要32個(gè)LUT。

因此 X+1 消耗的資源更多。

假如是Vivado綜合,即使用Carry8

對(duì)于32bit的加法,需要4個(gè)carry8,那么是否意味著 X+32 和 X+1 有相同的資源消耗呢?

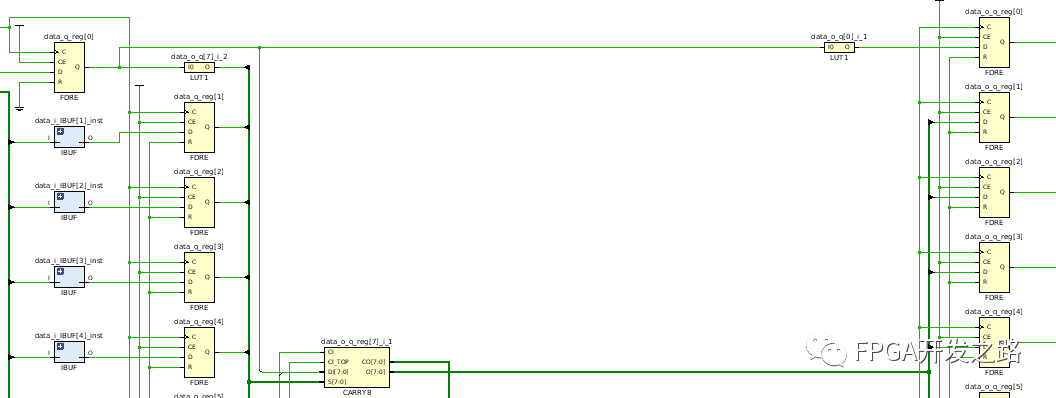

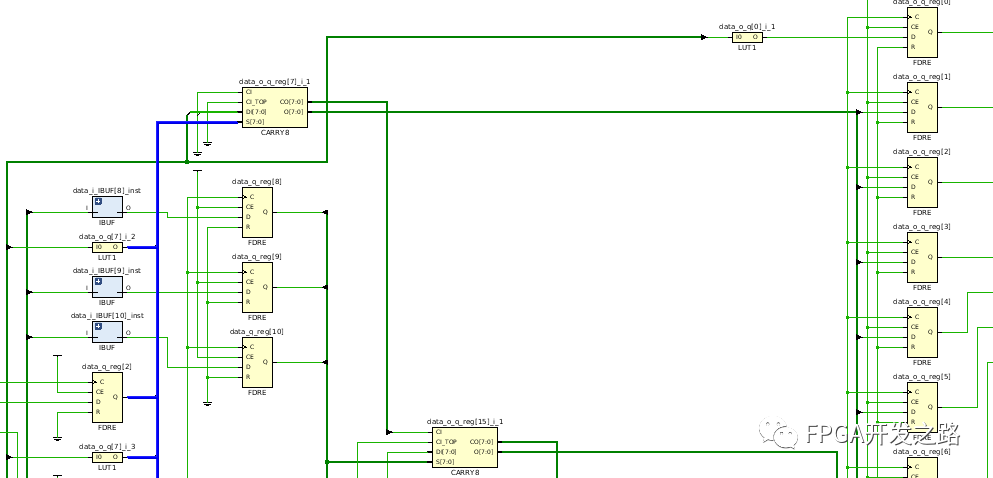

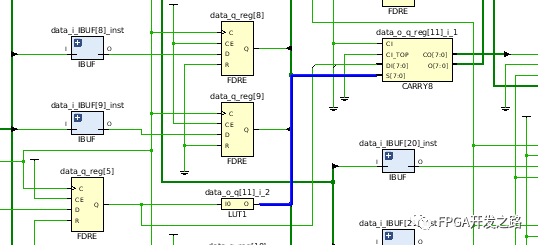

查看綜合結(jié)果(如下圖所示):

X+1 2個(gè)LUT1+4個(gè)Carry8 (LUT1實(shí)現(xiàn)的是取反的功能)

X+3 3個(gè)LUT1+4個(gè)Carry8 (bit0消耗2個(gè)LUT1,bit1消耗一個(gè)LUT1)

X+32 1個(gè)LUT1+4個(gè)Carry8 (bit5消耗1個(gè)LUT1)

因此從綜合結(jié)果看仍然是 X+1消耗的資源更多。當(dāng)然這僅僅考慮單個(gè)加法的結(jié)果,如果實(shí)際代碼中,加法器前面還有組合邏輯,這個(gè)LUT1應(yīng)該是會(huì)合并在前面的LUT中實(shí)現(xiàn),因而X+1和X+32會(huì)得到相同的資源消耗,即4個(gè)Carry8。

感興趣的讀者可以思考下 X-32會(huì)消耗多少LUT。

圖2 - X+1

圖3 - X+3

圖4 - X+32

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1644文章

22008瀏覽量

616514 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124790 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12805 -

運(yùn)算

+關(guān)注

關(guān)注

0文章

132瀏覽量

26161 -

Vivado

+關(guān)注

關(guān)注

19文章

834瀏覽量

68482

原文標(biāo)題:X+32 vs X+1 誰消耗的FPGA資源多

文章出處:【微信號(hào):FPGA開發(fā)之路,微信公眾號(hào):FPGA開發(fā)之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

花了1萬多的本錢了,FPGA PCIE X8 板子終于搞定了

VL53L1X初始化序列后SW待機(jī)消耗的問題如何處理?

簡談FPGA設(shè)計(jì)中不同設(shè)計(jì)方法資源消耗對(duì)比

小米5x和華為nova對(duì)比,華為nova和小米5x性能誰更強(qiáng)

CPU資源消耗的原因和解決方案

FPGA布局及資源優(yōu)化

FPGA中實(shí)現(xiàn)信號(hào)延時(shí)的資源消耗

9FGL02x1-04x1-06x1-08x1 系列數(shù)據(jù)表

9DBL02x2-04x2-06x1-08x1 系列數(shù)據(jù)表

9FGL02x1-04x1-06x1-08x1D 數(shù)據(jù)表

9FGL02x1-04x1-06x1-08x1 系列數(shù)據(jù)表

9DBL02x2-04x2-06x1-08x1 系列數(shù)據(jù)表

9FGL02x1-04x1-06x1-08x1D 數(shù)據(jù)表

X+32和X+1誰消耗的FPGA資源多

X+32和X+1誰消耗的FPGA資源多

評(píng)論