銅的電阻率取決于其晶體結(jié)構(gòu)、空隙體積、晶界和材料界面失配,這在較小的尺度上變得更加重要。傳統(tǒng)上,銅(Cu)線的形成是通過使用溝槽蝕刻工藝在低k二氧化硅中蝕刻溝槽圖案,然后通過鑲嵌流用Cu填充溝槽來完成的。不幸的是,這種方法產(chǎn)生具有顯著晶界和空隙的多晶結(jié)構(gòu),這增加了銅線電阻。該工藝中還使用了高電阻TaN襯墊材料,以防止鑲嵌退火工藝期間的銅擴(kuò)散。

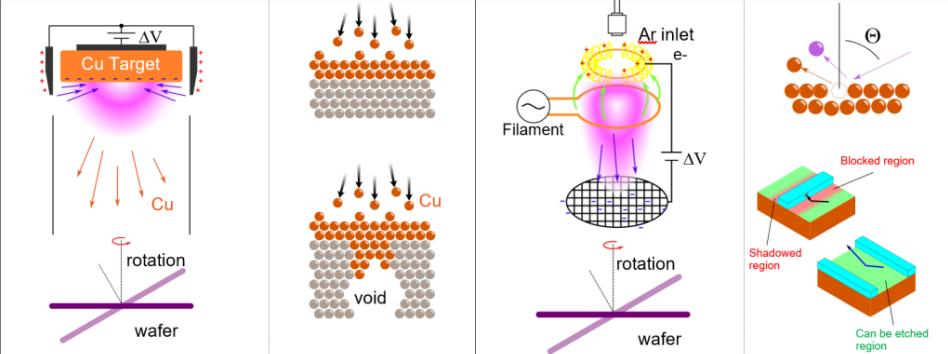

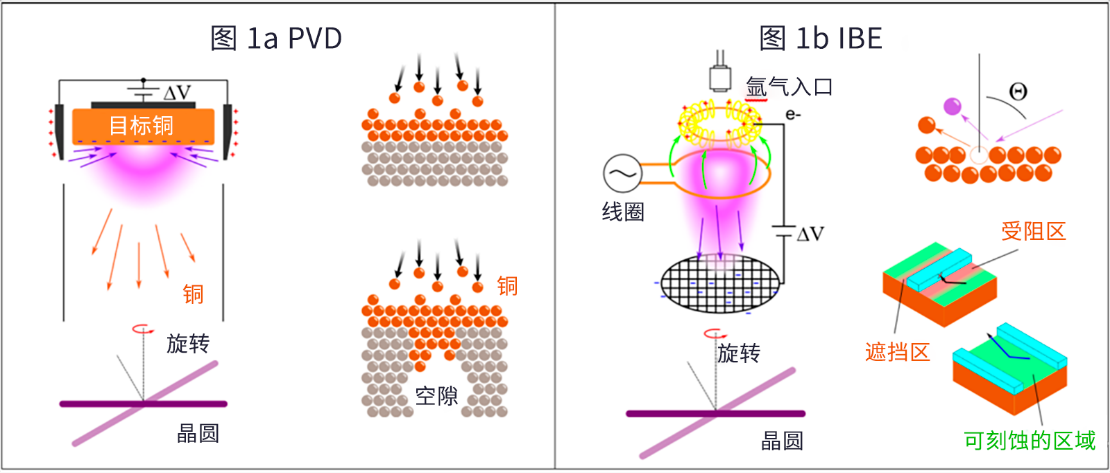

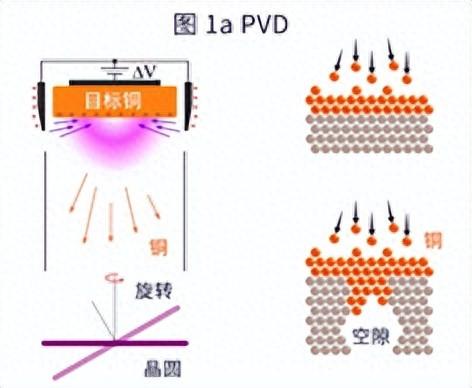

物理氣相沉積(PVD)可用于在高動(dòng)能(10至100eV之間)沉積銅,形成低電阻、致密的單晶結(jié)構(gòu)。PVD的一個(gè)缺點(diǎn)是PVD沉積具有視線擴(kuò)散并且只能在平坦表面上均勻沉積。它不能用于填充深孔或溝槽(圖1a)。為了形成孤立的線形狀,我們必須在平坦的表面上沉積均勻的銅層,然后通過離子束進(jìn)行物理蝕刻。

Cu不會(huì)與反應(yīng)氣體形成揮發(fā)性化合物,因此不能使用反應(yīng)離子蝕刻工藝。如果入射角非常高,離子束蝕刻 (IBE) 過程中產(chǎn)生的加速Ar離子可以去除Cu。不幸的是,由于掩模陰影效應(yīng),可蝕刻區(qū)域?qū)⑹艿较拗啤D1b顯示了當(dāng)掩模垂直于入射離子束時(shí)材料無法蝕刻的區(qū)域(紅色)。這種蝕刻失敗的發(fā)生是由于噴射原子路徑的陰影或阻塞。當(dāng)掩模平行于離子路徑時(shí),所有未掩模的區(qū)域都可以被蝕刻。因此,離子束蝕刻僅限于蝕刻任意長(zhǎng)長(zhǎng)度的線形掩模。

圖1:(1a)物理氣相沉積(PVD);(1b) 離子束蝕刻 (IBE)

圖1:(1a)物理氣相沉積(PVD);(1b) 離子束蝕刻 (IBE)

工藝步驟和虛擬制造過程

為了了解沉積和蝕刻對(duì)線路電阻的影響,英思特使用可見性沉積和蝕刻功能對(duì)PVD和 IBE蝕刻工藝進(jìn)行建模。PVD使用SEMulator3D中的30度角展度可見性沉積過程進(jìn)行再現(xiàn),該過程準(zhǔn)確地模擬了AR離子轟擊過程中噴射銅原子的隨機(jī)性質(zhì)。IBE在模型中使用具有2度角展度和60度極角傾斜的可見性蝕刻來再現(xiàn),以反映具有低光束發(fā)散度的網(wǎng)格加速離子的行為。

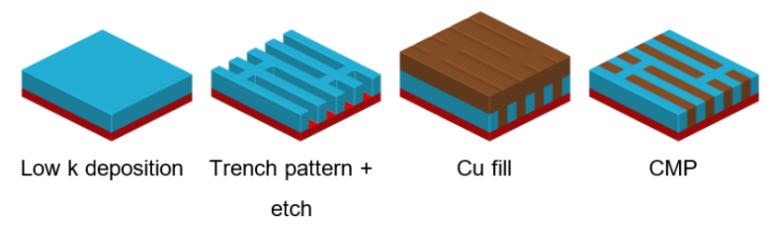

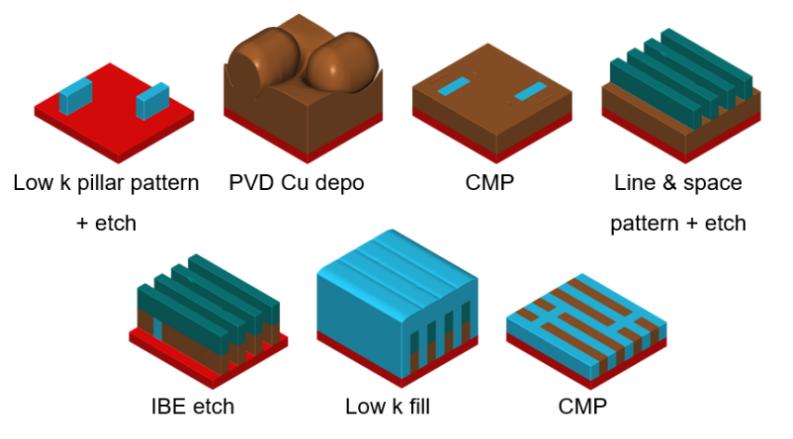

虛擬制造工藝中的其他工藝步驟已進(jìn)行調(diào)整,以適應(yīng)IBE和PVD限制。圖2顯示了使用鑲嵌銅填充(圖2a)和PVD/IBE工藝(圖2b)創(chuàng)建的相同結(jié)構(gòu)。

然后,英思特證明可以使用 PVD/IBE 線制造等效的16nm SRAM電路單元,同時(shí)遵守這些限制。由于線路中端上方的所有金屬層均由平坦表面制成,因此這使其成為 PVD/IBE 線的理想候選者,這與finFET 器件中復(fù)雜的互連拓?fù)洳煌?/p>

圖2a:鑲嵌填充銅線制造

圖2a:鑲嵌填充銅線制造  圖2b:PVD/IBE 銅線制造

圖2b:PVD/IBE 銅線制造

電阻結(jié)果及結(jié)論

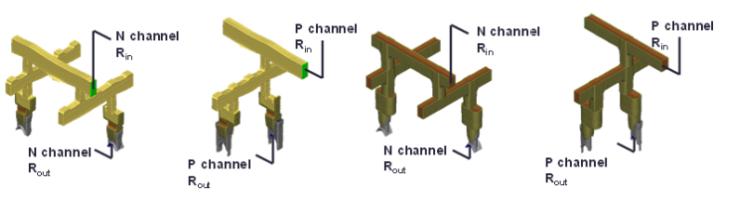

然后,我們針對(duì)鑲嵌流和物理氣相沉積測(cè)量從頂層金屬層到finFET P和N通道過孔的導(dǎo)線電阻。圖3顯示了P通道和N通道處電阻測(cè)量的起點(diǎn)和終點(diǎn)(所有其他絕緣材料都是透明的)。為了補(bǔ)償TaN襯墊和銅線之間的界面電阻,通過使用1nm的指數(shù)衰減常數(shù)作為距 TaN界面較近距離的函數(shù)來增加銅的電阻率。由于鑲嵌填充銅沉積預(yù)計(jì)不會(huì)完全結(jié)晶,因此銅的電阻率增加了50%。PVD/IBE銅工藝不使用TaN襯里,因此沒有應(yīng)用指數(shù)衰減函數(shù),該模型中使用了銅的體電阻率。圖3中包含比較鑲嵌流與 PVD的電阻率表。

圖3:P 和 N 通道電阻測(cè)量的起點(diǎn)和終點(diǎn)

圖3:P 和 N 通道電阻測(cè)量的起點(diǎn)和終點(diǎn)

英思特根據(jù)模型計(jì)算出的電阻值表明,與傳統(tǒng)的溝槽蝕刻和鑲嵌沉積相比,使用 IBE/PVD 制造方法可以將電阻降低67%。出現(xiàn)這種情況是因?yàn)镮BE/PVD中不需要TaN襯里,并且在此過程中CU電阻率較低。我們的結(jié)果表明,與金屬線形成過程中的鑲嵌填充相比,使用IBE/PVD可以提高電阻率,但代價(jià)是制造工藝更加復(fù)雜。

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28266瀏覽量

229016 -

蝕刻

+關(guān)注

關(guān)注

9文章

424瀏覽量

15823 -

蝕刻工藝

+關(guān)注

關(guān)注

3文章

52瀏覽量

11867 -

晶圓蝕刻

+關(guān)注

關(guān)注

0文章

17瀏覽量

5940

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

降低半導(dǎo)體金屬線電阻的沉積和刻蝕技術(shù)

求LCVD激光氣相沉積設(shè)備/激光直寫設(shè)備

半導(dǎo)體制程

《炬豐科技-半導(dǎo)體工藝》硅納米柱與金屬輔助化學(xué)蝕刻的比較

《炬豐科技-半導(dǎo)體工藝》GaAs/Al0.4Ga0.6As微加速度計(jì)的設(shè)計(jì)與制作

《炬豐科技-半導(dǎo)體工藝》GaN的晶體濕化學(xué)蝕刻

《炬豐科技-半導(dǎo)體工藝》InGaP 和 GaAs 在 HCl 中的濕蝕刻

《炬豐科技-半導(dǎo)體工藝》GaN、ZnO和SiC的濕法化學(xué)蝕刻

半導(dǎo)體電阻率的溫度依賴性

試述為什么金屬的電阻溫度系數(shù)是正的而半導(dǎo)體的是負(fù)的?

詳解SiGe的蝕刻和沉積控制

降低半導(dǎo)體金屬線電阻的沉積和刻蝕技術(shù)

降低半導(dǎo)體金屬線電阻的沉積和蝕刻技術(shù)

降低半導(dǎo)體金屬線電阻的沉積和蝕刻技術(shù)

評(píng)論