SDRAM是一種同步動(dòng)態(tài)隨機(jī)訪問(wèn)內(nèi)存,它具有內(nèi)置控制器,通過(guò)與CPU時(shí)鐘同步來(lái)工作,使得數(shù)據(jù)傳輸更為高效。SDRAM在內(nèi)存顆粒市場(chǎng)中占據(jù)主導(dǎo)地位,廣泛應(yīng)用于各種計(jì)算機(jī)系統(tǒng)和服務(wù)器中,為數(shù)據(jù)處理和存儲(chǔ)提供了快速且可靠的支持。 SDRAM具有高速度、高密度、低功耗等優(yōu)點(diǎn)。其內(nèi)部結(jié)構(gòu)采用Bank架構(gòu),允許同時(shí)進(jìn)行多個(gè)讀寫操作,從而提高了整體性能。此外,SDRAM還具有自動(dòng)刷新功能,能夠確保數(shù)據(jù)在長(zhǎng)時(shí)間內(nèi)保持正確性。 華芯微特已經(jīng)將SDRAM合封入芯片,合封的SDRAM大小根據(jù)芯片型號(hào)不同,具體見選型手冊(cè)。

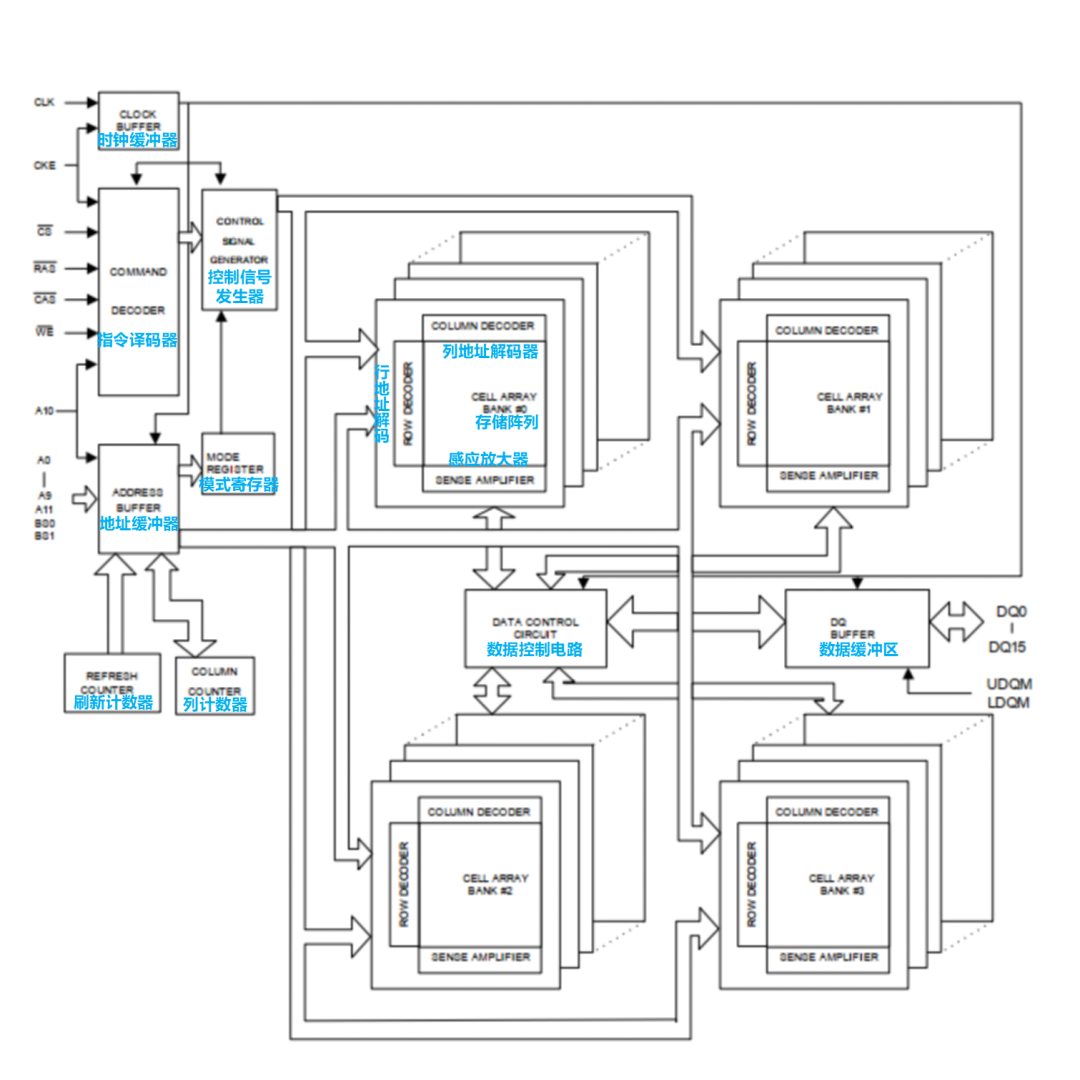

SDRAM 結(jié)構(gòu)框圖

SDRAM的內(nèi)部是一個(gè)存儲(chǔ)陣列,將數(shù)據(jù)“填”進(jìn)去,你可以它想象成一張表格。和表格的檢索原理一樣,先指定一個(gè)行(Row),再指定一個(gè)列(Column),我們就可以準(zhǔn)確地找到所需要的單元格,這就是內(nèi)存芯片尋址的基本原理。 為了詳細(xì)地介紹SDRAM以及它的使用,以某一款SDRAM數(shù)據(jù)手冊(cè)結(jié)構(gòu)框圖來(lái)分析, 內(nèi)部主要構(gòu)成部分如下圖所示:

01 SDRAM 信號(hào)線

CLK:同步時(shí)鐘信號(hào),提供SDRAM工作時(shí)鐘,所有輸入信號(hào)在CLK為上升沿時(shí)被采樣。 CKE:時(shí)鐘使能信號(hào)。時(shí)鐘使能進(jìn)入正常工作模式,時(shí)鐘失能進(jìn)入休眠模式或者自刷新模式。 CS :片選信號(hào),低電平有效。 CAS:列地址選通,當(dāng)為低電平時(shí)地址線表示為列地址。 RAS:行地址選通,當(dāng)為低電平時(shí)地址線表示為行地址。 WE:讀寫指令切換信號(hào)。低電平:寫使能;高電平:讀使能。 DQM[1:0]:輸入/輸出掩碼信號(hào),表示DQ數(shù)據(jù)的有效部分。當(dāng)DQM在讀取周期中被采樣為高時(shí),輸出緩沖器被置于Hi-Z(具有2的延遲)。在寫入周期中,采樣DQM高電平將以零延遲阻止寫入操作。 BS:BANK地址輸入,選擇要控制的BNAK。 A[12:0]:地址信號(hào)線,地址線A10控制著是否進(jìn)行在讀或?qū)懖僮髦螽?dāng)前L-Bank自動(dòng)進(jìn)行預(yù)充電。 DQ[15:0] :數(shù)據(jù)輸入輸出信號(hào)線。

對(duì)于DQM(Data I/O Mask)信號(hào),每個(gè)DQM控制屏蔽8bit數(shù)據(jù),對(duì)于這款SDRAM,它是16bit的,UDQM可屏蔽高8位,LDQM可屏蔽低8位。對(duì)于16bit的數(shù)0xDDFF,我們?nèi)绻恍韪?位寫入,低8位不寫入,在寫入時(shí)可以將UDQM置低,LDQM置高。

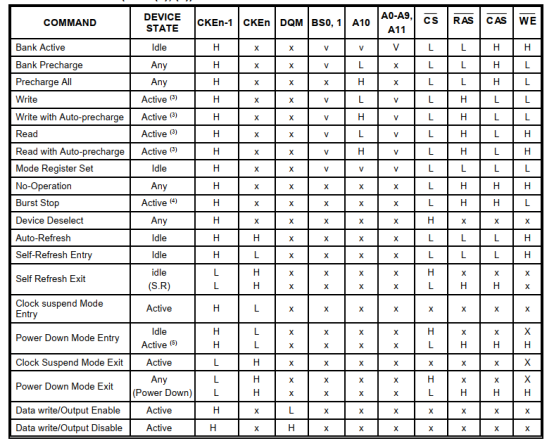

02 SDRAM 操作命令

NO-Operation:空操作命令,用于選中SDRAM,防止SDRAM接受錯(cuò)誤的命令,為接下來(lái)的命令發(fā)送做準(zhǔn)備。

Active (用于存儲(chǔ)單位尋址):激活命令,該命令必須在讀寫操作之前被發(fā)送,用于設(shè)置所需要的BANK和行地址 (同時(shí)設(shè)置) ,BANK地址由BS0(BA0),BS1(BA1)決定,行地址由A0~12決定。

Read / Write:讀/寫命令,在發(fā)送完激活命令后,并進(jìn)行讀寫再發(fā)送列地址就可以完成對(duì)SDRAM的尋址,并進(jìn)行讀寫操作。

Precharge:預(yù)充電指令,用于關(guān)閉BANK中所打開的行地址,準(zhǔn)備打開新行。進(jìn)行完讀寫操作后,要對(duì)同一BANK的另一行進(jìn)行尋址,就要將原來(lái)有效(打開)的行關(guān)閉,重新發(fā)送行/列地址。

Refresh:SDRAM存儲(chǔ)的數(shù)據(jù)需要不斷進(jìn)行刷新操作才能保存,用于刷新一行數(shù)據(jù),可以依次對(duì)所有的行進(jìn)行刷新操作。CKE引腳高電平為自動(dòng)刷新(Auto Refresh),CKE為低電平是自我刷新(Self Refresh)。

自動(dòng)刷新:依靠刷新計(jì)數(shù)器(行地址生成器)自動(dòng)依次生成要刷新的行地址刷新周期 (完成一次所有行的刷新所需要的時(shí)間) :64ms。自我刷新:用于休眠低功耗狀態(tài)下的數(shù)據(jù)保存。

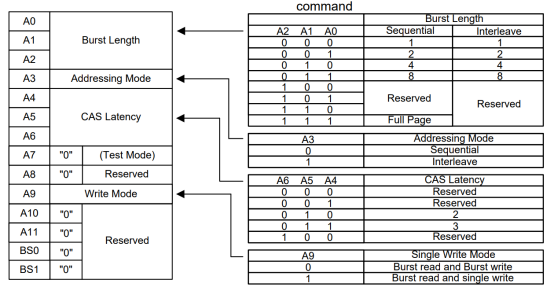

Mode Register Set:設(shè)置模式寄存器。SDRAM芯片內(nèi)部有一個(gè)邏輯控制單元,控制單元的相關(guān)參數(shù)由模式寄存器提供。該命令在每次對(duì)SDRAM進(jìn)行初始化時(shí)都需要用到。

具體模式設(shè)置,如下圖:

A0~A2:用來(lái)指定突發(fā)的長(zhǎng)度,1,2,4,8或者全頁(yè)突發(fā)。所謂的“突發(fā)”是指當(dāng)我們對(duì)一個(gè)地址進(jìn)行尋址并操作完成后,不必再重新對(duì)下一個(gè)地址進(jìn)行尋址,而是直接進(jìn)行操作。

A3:設(shè)置突發(fā)的類型,連續(xù)型和非連續(xù)型。

A4~A6:指定潛伏期的長(zhǎng)度,可以選擇延時(shí)2,3兩個(gè)周期。

A9:用來(lái)指定操作模式。

03 SDRAM容量計(jì)算

SDRAM總存儲(chǔ)容量 =行數(shù)×列數(shù)×L-Bank的數(shù)量×存儲(chǔ)單元的容量

Row Address : A0~A11

Column Address : A0-A8

Bank = 4

Data Width=16bit

Capacity=212x 29x 4bank x 16bit=128Mbit

04 SDRAM上電初始化過(guò)程

1、VDD (供輸入buffer和邏輯電路)和VDDQ(供輸出buffer)上電,此期間CKE保持低電平。2、開始時(shí)鐘并使CKE置高。

3、電源、時(shí)鐘都穩(wěn)定后,再等待200uS。

4、發(fā)出預(yù)充電命令。

5、發(fā)出多個(gè) (8個(gè)以上) 刷新命令 (REF)。

6、發(fā)出模式寄存器設(shè)置命令 (MRS),初始化模式寄存器 (DDR2 中還有EMRS,進(jìn)行ODT.OCD等功能的設(shè)置和調(diào)整)。

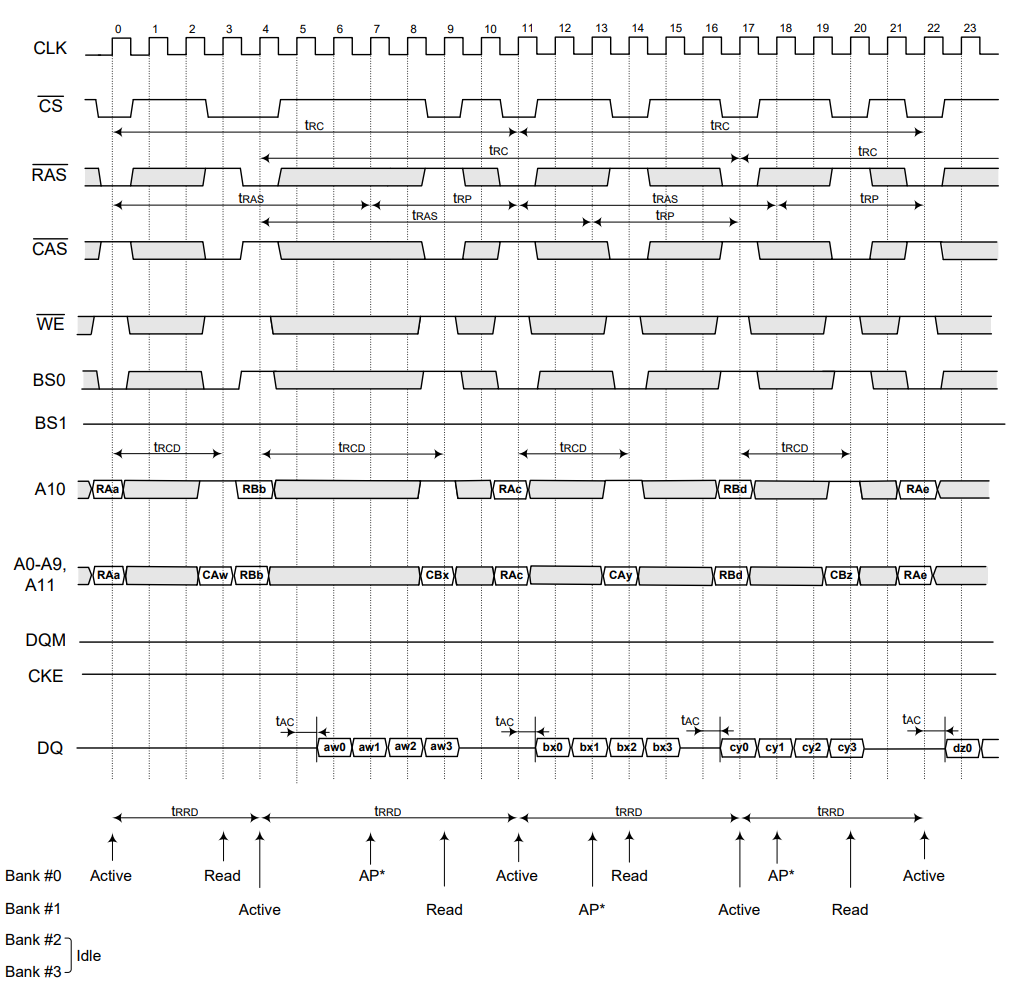

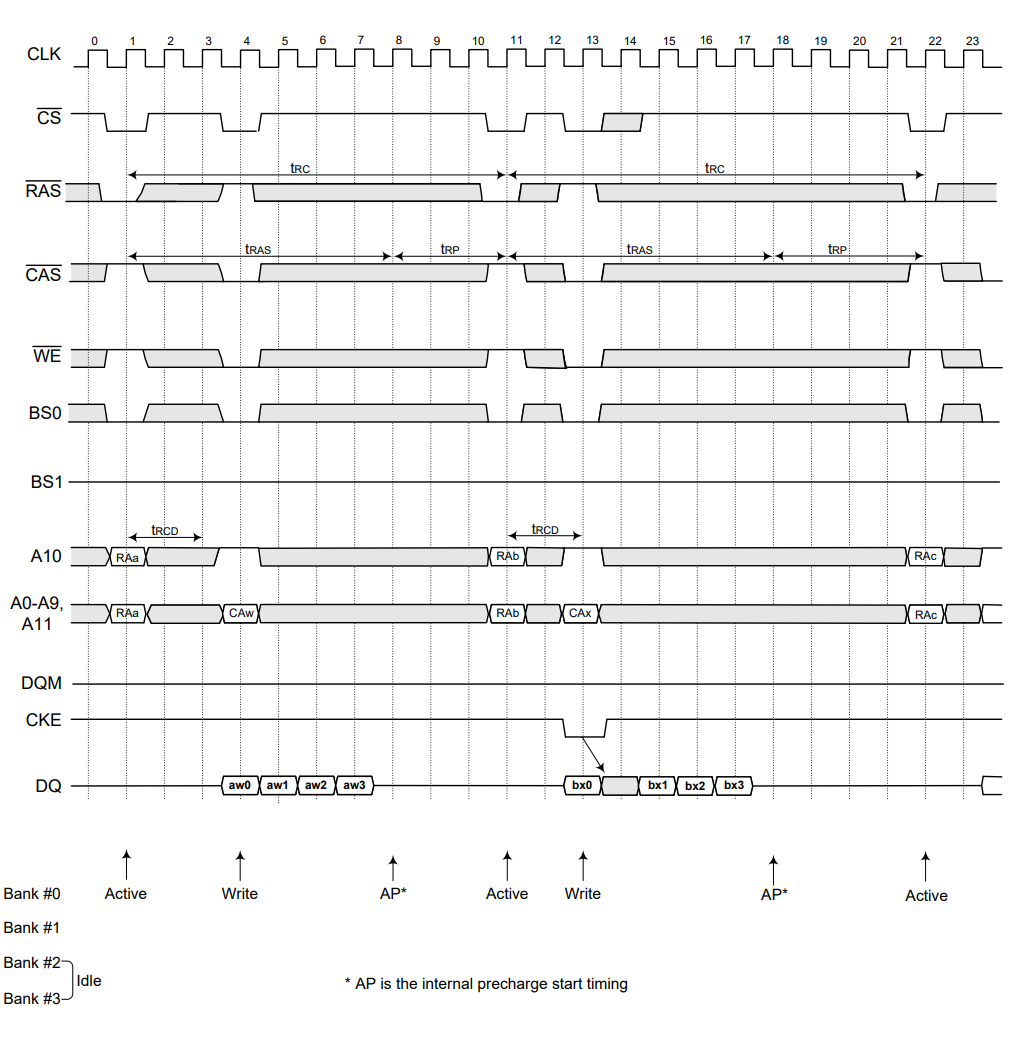

05 SDRAM 讀寫時(shí)序

這里從SDRAM手冊(cè)截取讀時(shí)序進(jìn)行分析,這里需要參考下圖的操作命令具體值與時(shí)序圖一起分析。

1.讀時(shí)序(Burst Length = 4, CAS Latency = 3, Auto-Precharge))

讀取數(shù)據(jù)過(guò)程:

1)發(fā)送激活命令,設(shè)置行地址和Bank地址。

2)設(shè)置列地址,發(fā)送讀命令。

3)將A10地址線拉高,自動(dòng)預(yù)充電使能。

4)開始執(zhí)行預(yù)充電。

5) 完成數(shù)據(jù)讀取。

2.寫時(shí)序(Auto-Precharge Write,Burst Length = 4)

寫過(guò)程跟讀取類似:

1)發(fā)送激活命令,設(shè)置行地址和Bank地址。

2)設(shè)置列地址,發(fā)送寫命令。

3)將A10地址線拉高,自動(dòng)預(yù)充電使能

4)開始執(zhí)行預(yù)充電。

5) 完成數(shù)據(jù)寫入。

-

芯片

+關(guān)注

關(guān)注

459文章

52287瀏覽量

437547 -

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56102 -

寄存器

+關(guān)注

關(guān)注

31文章

5425瀏覽量

123657

原文標(biāo)題:芯課堂|SDRAM工作原理及時(shí)序分析

文章出處:【微信號(hào):gh_ed4f95bde4df,微信公眾號(hào):華芯微特32位MCU】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

時(shí)序分析總結(jié)(以SDRAM時(shí)序約束為例)

SDRAM的基本工作原理是什么?怎么實(shí)現(xiàn)SDRAM控制器?

PDP4218三星V3屏電源工作原理及時(shí)序

SDRAM的原理和時(shí)序

SDRAM的工作原理

基于DDR SDRAM控制器時(shí)序分析的模型

關(guān)于SDRAM的時(shí)序控制研究方案分析

一種基于FPGA的SDRAM設(shè)計(jì)與邏輯時(shí)序分析

SDRAM工作原理及時(shí)序分析

SDRAM工作原理及時(shí)序分析

評(píng)論