中斷掛起位

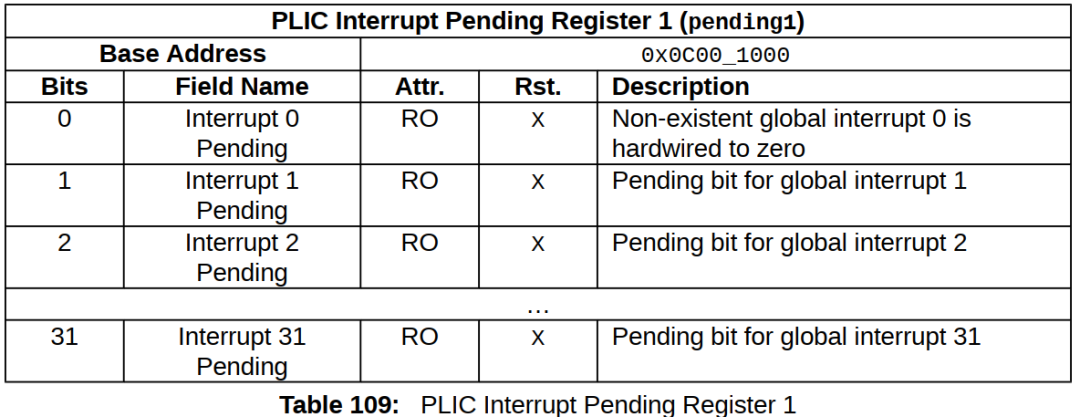

PLIC 內核中中斷源掛起位的當前狀態可以從掛起數組中讀取,組織為 32 位的 5 個字。中斷 ID 的掛起位存儲在字的位中。

因此,U54 內核有 5 個中斷掛起寄存器。表示不存在的中斷源 0 的字 0 的位 0 硬接線為零。

PLIC 內核中的掛起位可以通過設置相關的啟用位然后執行第 9.8 節中描述的聲明來清除

中斷使能

每個全局中斷都可以通過設置啟用寄存器中的相應位來啟用。使能寄存器作為 5 × 32 位字的連續數組進行訪問,其打包方式與未決位相同。使能字 0 的位0 表示不存在的中斷 ID 0,并硬接線為 0。

SiFive RV64 系統中的使能數組支持 64 位和 32 位字訪問。

PLIC Clock Gate Disable

PLIC 實現時鐘門控功能以在不活動時門控模塊時鐘節點。PLIC 時鐘門控在復位后被禁用,應在啟動代碼中啟用,除非 SiFive勘誤表另有規定。一旦啟用,時鐘僅在 PLIC 控制總線上或任何中斷線上有活動且相應中斷未運行時才可用。

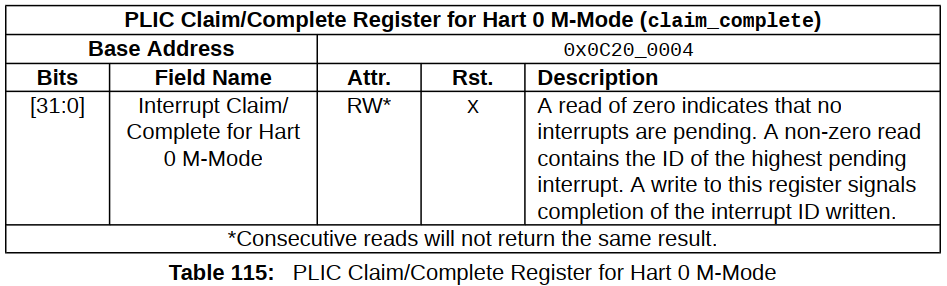

優先級閾值

U54 內核 支持通過閾值寄存器設置中斷優先級閾值。閾值是一個WARL字段,其中U54 內核支持的最大閾值為7。

U54 核心復合體屏蔽優先級小于或等于閾值的所有 PLIC 中斷。例如,閾值為零允許所有具有非零優先級的中斷,而值為 7則屏蔽所有中斷。如果閾值寄存器的值為 5,則不允許將優先級配置為從 1 到 5 的所有 PLIC 中斷傳播到 CPU。

-

內核

+關注

關注

3文章

1412瀏覽量

41182 -

中斷

+關注

關注

5文章

904瀏覽量

42581 -

RISC

+關注

關注

6文章

480瀏覽量

84781 -

LIC技術

+關注

關注

0文章

2瀏覽量

5080 -

sifive

+關注

關注

0文章

36瀏覽量

9570

發布評論請先 登錄

Linux內核中斷設計與實現

stm32上的中斷掛起和屏蔽與ARM內核中的掛起屏蔽是相同的嗎?

Linux 2.4.x內核軟中斷機制

MSP430的中斷

linux內核-時鐘中斷

STM32 中斷原理及外部中斷的實現

STM32自學筆記(二)中斷

LIC內核中斷掛起位和中斷使能

LIC內核中斷掛起位和中斷使能

評論