什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思

奇偶校驗是一種用于檢測二進制數(shù)據(jù)中錯誤的方法。它的基本原理是在二進制數(shù)據(jù)的末尾添加一個額外的位,使得數(shù)據(jù)中二進制 1 的數(shù)量為奇數(shù)或偶數(shù)。在這個額外的位上如果數(shù)據(jù)傳輸過程中發(fā)生了錯誤,就可以通過檢測這個位的奇偶性來確定錯誤的位置。

假設(shè)我們有一位二進制數(shù)據(jù),如1011,則它有三個二進制 1 和一個二進制 0。根據(jù)奇偶校驗的原理,我們可以在數(shù)據(jù)的末尾添加一個額外的位,使得數(shù)據(jù)的奇偶性變成奇數(shù)或偶數(shù)。如果我們選擇奇偶性為奇數(shù),那么需要在末尾添加一個二進制 1,即數(shù)據(jù)變成10111。如果數(shù)據(jù)傳輸過程中發(fā)生了錯誤,比如由于噪聲引起了一個二進制位的變化,那么這個錯誤就會影響到奇偶校驗位,從而導(dǎo)致奇偶性變成偶數(shù)。在接收端,我們通過檢測奇偶性是否正確來判斷數(shù)據(jù)是否正確。如果奇偶性不匹配,就說明數(shù)據(jù)傳輸過程中出現(xiàn)了錯誤。

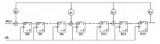

奇偶校驗電路就是用來實現(xiàn)奇偶校驗的電路。它通常由一個比特生成器、一個奇偶性判斷器和一個比特檢測器組成。比特生成器用來生成校驗位,奇偶性判斷器用來檢測數(shù)據(jù)的奇偶性,比特檢測器用來檢測數(shù)據(jù)是否正確。

奇偶校驗電路可以在很多地方使用。比如在串行通信中,數(shù)據(jù)通常是按位傳輸?shù)模虼撕苋菀壮霈F(xiàn)傳輸錯誤。使用奇偶校驗電路可以很快的檢測到這些錯誤,并且可以通過重新傳輸數(shù)據(jù)來修復(fù)數(shù)據(jù)錯誤。另外,奇偶校驗電路也可以用于存儲系統(tǒng)中,例如計算機內(nèi)存、磁盤和閃存等設(shè)備。通過在存儲的數(shù)據(jù)上添加奇偶校驗位,我們可以在讀取時檢測到數(shù)據(jù)是否正確,從而防止儲存和讀取錯誤。

總之,奇偶校驗是一種簡單的錯誤檢測解決方案,可以在許多應(yīng)用中使用。然而,它只能檢測一位的錯誤,對于多位錯誤的檢測就需要使用其他更復(fù)雜的校驗方法。

-

奇偶校驗

+關(guān)注

關(guān)注

0文章

15瀏覽量

8330 -

奇偶校驗電路

+關(guān)注

關(guān)注

0文章

3瀏覽量

2147

發(fā)布評論請先 登錄

【RA-Eco-RA6M4開發(fā)板評測】+初識篇

芯知識|廣州唯創(chuàng)電子語音芯片通信控制方式解析:多模式選擇與工程適配指南

基于Verilog語言實現(xiàn)CRC校驗

請問DAC3484的LVDS數(shù)字接口如何區(qū)分4個信道?

RAID 5 磁盤陣列的組成

RAID 5 性能優(yōu)化技巧

RAID 5 技術(shù)優(yōu)勢與應(yīng)用

串口通訊異常處理方法 串口設(shè)備連接方式

dac161p997這幾個寄存器全配置為0,當(dāng)發(fā)生錯誤時,dac161p997會不會依據(jù)錯誤的數(shù)據(jù)進行輸出?

raid 硬盤陣列優(yōu)缺點

嵌入式學(xué)習(xí)-飛凌嵌入式ElfBoard ELF 1板卡-串口通訊編程示例之串口硬件原理

飛凌嵌入式ElfBoard ELF 1板卡-串口通訊編程示例之串口硬件原理

UART串口通訊協(xié)議解析

雙模藍牙模塊UART串口和RS232在通訊領(lǐng)域的優(yōu)勢

如何通過I2C加載TPS2388x SRAM和奇偶校驗代碼

什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思

什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思

評論