文章來源:中國物理學會期刊網 原文作者:復旦大學陸葉、唐誠杰 編譯自 James McKenzie. Physics World,2023,(8):30

本文選自《物理》2023年第9期

英特爾共同創始人戈登·摩爾(Gordon Moore)在今年與世長辭,而他對半導體芯片晶體管密度持續增長的著名預測依舊聞名于世。詹姆斯·麥肯齊(James McKenzie)深入研究了這一60多年來仍然正確的預測,也就是大家所熟知的“摩爾定律”,但同時也提醒人們,這一定律的延續正日益困難,且成本不斷攀升。

當臺積電(TSMC)2022年宣布計劃興建一座新的集成電路制造工廠之時,引人注目的不僅僅是高達330億美元的造價,更重要的是這座即將在2025年于新竹啟動的新工廠會被用于制造世界上第一款“2納米”尺度的芯片。新芯片會比現有任何芯片更小、更快,且能效提高30%。新芯片將幫助極大提升從智能手機到電腦等電子設備的性能。

不過半導體行業對能夠制造出如此小尺度且性能強勁的芯片已經習以為常,早在1965年戈登·摩爾就提出了被后世稱為“摩爾定律”的著名預測,即在集成電路(芯片)上的晶體管數量每年都會翻倍。摩爾在《電子學》雜志上預測,到1975年,工業界有能力在一個面積為一平方英寸(6.25 cm2)的硅芯片上制造25萬個元器件。

雖然摩爾本人后來自謙地稱這個預測只是一個“野心勃勃的推測”,并且其在1975年將這個預測修改為每2年晶體管數量增加1倍,但這樣一個“推測”確實一直被事實驗證至今。實際上摩爾定律從未被確立為一個科學“定律”,更多的是對半導體行業發展的描述以及推動未來產業發展的路線。

展望未來

基礎物理學告訴我們,隨著晶體管的變小,其運行速度更快,所需功率更低。簡單的經濟學原理也告訴我們,當一個芯片上放置了更多的晶體管時,每個晶體管所需的制造成本也更低。摩爾在他1965年發表的文章中提到“元器件的成本幾乎與元器件數量成反比”。事實證明摩爾是個有遠見的人,他正確地預見了半導體技術的迅猛發展,雖然多年過去,晶體管尺縮技術的具體細節已經有了很大的變化,但摩爾對于集成電路發展的預測已經成為了現實。他成功預見了數字手表、家用電腦、智能手機(或被他稱為個人移動通訊設備)的出現,以及用電話線傳遞多種信息、自動駕駛技術的問世。

在一次IEEE Spectrum發起的摩爾定律50周年的采訪中,摩爾表示自己也很驚訝他的預測能夠持續如此之久,“我從沒想過有人能把這個定律記這么久”。對他來說,摩爾定律的延續是對半導體產業工程師創造力的贊美,他們一次又一次地找到了新的方法來縮小晶體管尺寸,“我覺得只有幾代(芯片)的持續,在那之后(我們)會碰到一些壁壘,但事實上這些壁壘不斷地被打破。

但在同一次采訪中,摩爾也指出兩個基本物理極限將最終阻止芯片進一步微型化。他回憶起物理學家斯蒂芬·霍金在訪問硅谷時說過的話,“沒有什么可以超過光速,而材料最終也是由有限大小的原子組成的。”換言之,芯片的速度和尺度都有限制。摩爾提出了一個警示:“這些是我看不到怎樣才能繞過去的基本問題。而在接下去的幾代芯片上,我們就會直面這些問題。”

那么,摩爾定律的終結真的要來了嗎?

更小、更快、更好

計算機的核心是中央處理單元(CPU),它是由晶體管連接在一起并形成能執行基本算術運算的集成電路。世界上第一款單芯片微處理器是英特爾在1971年發布的四位CPU,即Intel 4004。其擁有2300個晶體管,每個晶體管的尺寸為10 μm,售價為60美元。不過摩爾預測,集成電路上的晶體管數目會迅速提升。

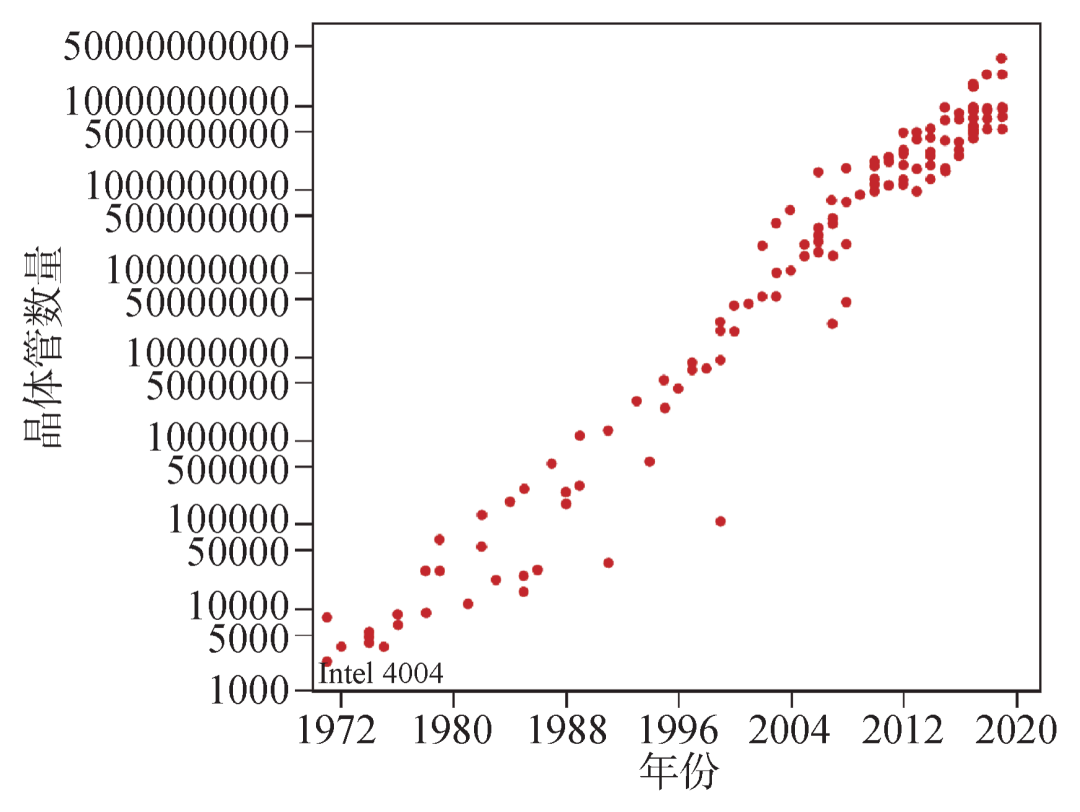

在80年代早期,產業界已經開始生產1 μm尺度的晶體管,單個芯片能容納的晶體管數目也達到10萬個,這個數字在90年代初已經達到了一百萬,21世紀初則接近了千萬,十年后更是已經過億。最新的利用“5 nm工藝”生產的CPU可以容納超過100億個晶體管,2019年英特爾已經能在一平方毫米的芯片上制造一億以上的晶體管了(圖2)。(不過現在的工藝名稱并不代表器件的實際尺寸,例如臺積電的2 nm芯片并不代表晶體管的實際物理尺寸能到2 nm。)

圖2 芯片上的晶體管數目在英特爾1971年發布第一款CPU芯片4004后快速上升。“摩爾定律”表明這個數目每兩年會翻一倍,但繼續這種趨勢正變得越加困難

現代集成電路制造是通過采用硅或其他半導體作為襯底,使用各種“光刻”技術逐層構建電路。制造工藝通常都涉及光或化學反應,除了極高的工藝制造水平之外,代工廠的潔凈程度也令人稱奇。

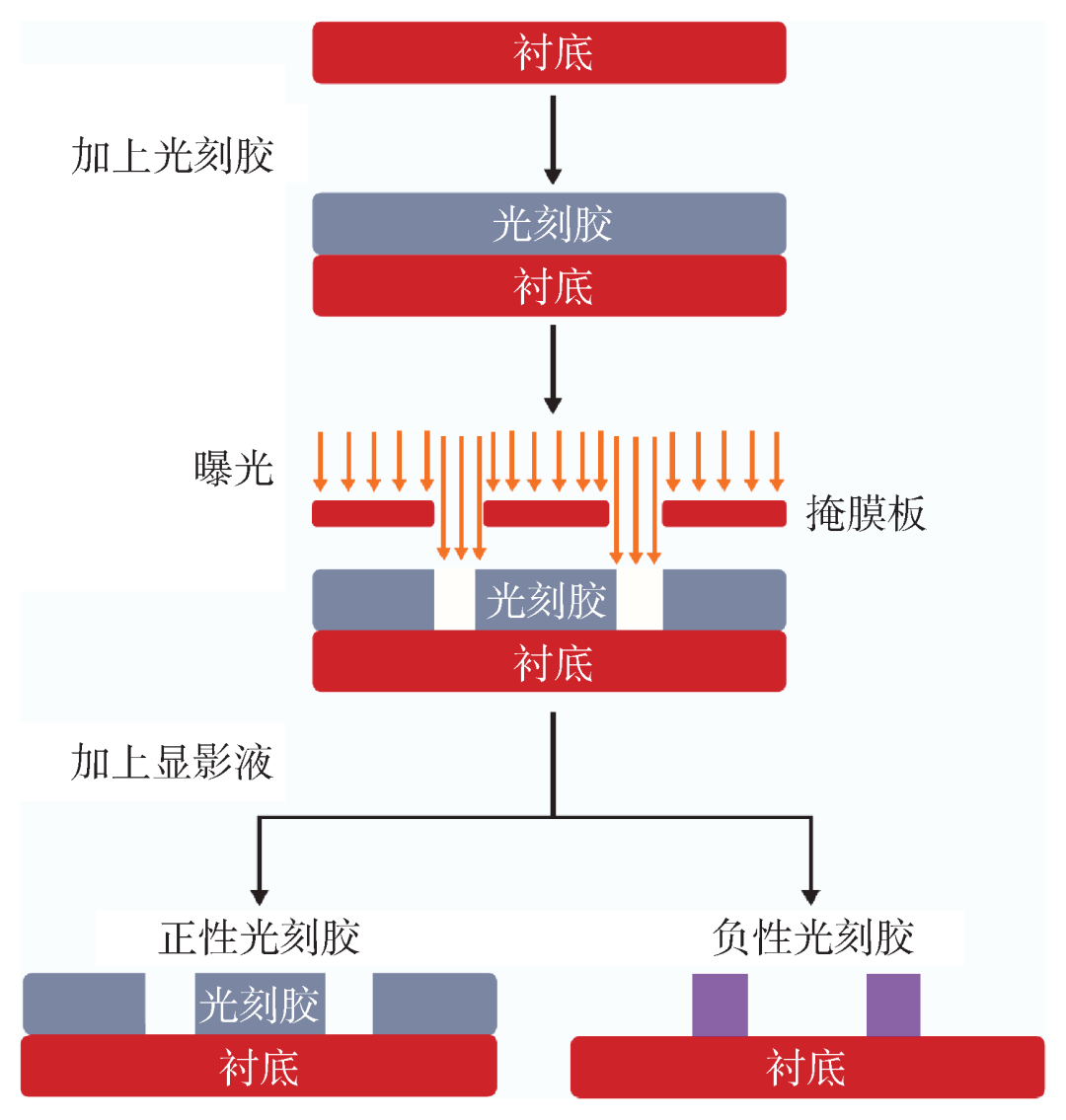

1971年英特爾生產的4004芯片采用“10 μm工藝”,也就意味著芯片上所有晶體管之間的間距不超過10 μm。為了達到這樣的小尺寸,英特爾率先使用了“光學掩模”技術,其本質上是一個大的、透明的玻璃板,部分被鉻覆蓋形成圖形,藍光通過掩模照射在晶片表面上。英特爾巧妙地使用光敏有機光刻膠覆蓋了晶圓,當光線照射到這些有機層的時候就會產生反應,未被曝光的區域則保持原樣,之后可以使用溶劑溶解掉那些被光線照射到的部分,從而把掩模上的原始圖案移到硅上(圖3),而完整地制造集成電路所需的器件都需要幾步掩模工藝完成。

圖3 光刻是制造更小晶體管的核心技術。這項技術通過在硅的表面涂覆能與光發生化學反應的光刻膠,結合有圖形的掩膜板,進一步采用光照和顯影來實現硅襯底表面的圖形化

為了讓集成電路晶體管尺縮延續,人們在掩模和晶圓之間引入了越來越精確的“投影透鏡”。例如,在80年代,“步進式***”的發展讓2 μm芯片成為可能。步進式***統治了90年代的光刻技術,直到250 nm尺度。

集成電路制造中最小尺度最終被兩個因素所限制:首先是光刻膠的最大分辨率,其次是能夠投影到晶圓上的圖像最小尺寸。這個最小尺寸也被稱為瑞利判據或衍射極限,由公式0.61λ/NA給出,其中λ是光的波長,NA是投影透鏡的數值孔徑。換句話說,光波長的一半定義了最小的投影尺寸。為了達到更小的尺度,光刻系統在多年的發展中逐漸轉向了比藍光(波長436 nm)波長更短的紫外光(波長365 nm),以及后來的深紫外光(波長248 nm),最新的***則采用了ArF準分子激光(193 nm)作為光源。而數值孔徑的提升,從早期系統的0.16到目前驚人的0.93,也很大程度上幫助了摩爾定律繼續延續。

向2 nm進軍

臺積電的工廠是如何實現2 nm工藝呢?即使對于193 nm波長的光來說,這個尺度也遠低于衍射極限。為了更小的尺度,大部分芯片制造廠都轉向了荷蘭ASML公司所開發的使用13.5 nm波長極紫外光的全新EUV***,這種光源已經接近X射線的范圍。這是令人難以置信的工程壯舉,它極大地推動了技術發展,進一步逼近了物理理論極限。在真空中用激光轟擊錫的熔融滴,產生EUV光,隨后被Zeiss提供的鏡片反射。每臺EUV***超過1.5億美元。盡管價格昂貴,但目前為止ASML公司已經售出了140多臺這樣的EUV***,作為唯一的供應商,ASML公司的技術能力事實上成為了半導體工業擴張的瓶頸。

根據報道,第一代用EUV技術制造的芯片已經被用于翻譯技術、搜索引擎、圖像識別及人工智能等科技上。我們的日常消費品中也有EUV技術的身影,最新款的手機芯片都需要用到ASML的設備來制造。

當然,材料科學與晶體管設計方面的進步也幫助了摩爾定律繼續延續,以“鰭式場效應晶體管”(FinFET)為例,它們在硅基底的表面使用隆起的鰭式結構。FinFET是3D堆疊式晶體管的先鋒,一些半導體公司已經做出了176層掩模層的設備,而半導體工業發展路線表明,接下來幾代器件可能采用超過600層掩模層的設備去制造。最新的2 nm工藝甚至使用了更高端的晶體管技術,也就是所謂的全環繞柵極技術(GAA),IBM公司已經采用這種晶體管技術制備了密度高達每平方毫米3.3億個晶體管的芯片,而IBM聲稱這種技術能在指甲蓋大小的芯片上容納超過500億個晶體管。這項技術將大大延長智能手機電池的壽命,減少數據中心的成本,且讓筆記本電腦運行更快。

突破物理限制

事實上業界正在嘗試一切可能的手段去延續摩爾定律。ASML正在著力發展1 nm光刻技術,這是值得期待的,畢竟2 nm工藝所生產的芯片相比3 nm工藝的芯片性能將提高15%,同時能耗減少25%。

摩爾定律當然尚未終結。雖然在2 nm的尺度物理上只有10個硅原子了,但是實際器件尺寸并不是2 nm,兩個柵極之間的距離可能達到50 nm,所以我們還有繼續尺縮的空間。

但另一方面,我們已經很難預見以后延續摩爾定律的關鍵創新是什么。2016年,來自德國、日本和美國的研究人員制造了一個由酞菁分子(phthalocyanine)和僅12個銦原子組成的晶體管,其柵極尺寸為0.167 nm,這可能是“摩爾定律的絕對硬極限”。為了不同的應用設計不同類型的芯片也是一種可行的方法,例如利用圖形處理單元(GPU)而不是CPU計算的AI技術,GPU能夠并行計算的特性提升了計算效率。

最后,將摩爾定律延續到多遠可能是一個純粹的經濟問題。就像相比于5 nm工廠150—200億美元的造價,臺積電的最新工廠成本高達330億美元,延續摩爾定律是一項風險極高的游戲。在這種情形之下,只有少數的幾個玩家有開發下一代芯片技術的資本。它們沒有放棄摩爾定律,但前面的道路將困難重重。

戈登·摩爾:個人經歷

戈登·摩爾(右)和英特爾共同創始人,中間是發明了第一塊集成電路的羅伯特·諾伊斯,左側是于1987年至1998年擔任英特爾CEO的安德魯·格魯夫

戈登·厄爾·摩爾于1929年1月3日出生在美國加州的佩斯卡德羅,1950年在加州大學伯克利分校獲得化學學士學位,之后在加州理工大學獲得了化學博士學位,并在1953—1956年期間在霍普金斯大學應用物理實驗室從事博士后研究,隨后他離開了學術界并加入了由物理學家威廉·肖克利建立的肖克利半導體實驗室(SSL)。

之后摩爾和其他七位同事一起在1957年辭職,并創辦了仙童半導體。也就是在1965年擔任仙童半導體研究總監期間,摩爾提出了他著名的“摩爾定律”。1968年,摩爾和鮑勃·諾伊斯離開了仙童并創建了著名的英特爾。摩爾在英特爾期間擔任過多個高級職位,包括主席與首席執行官(CEO)。摩爾還是一位慷慨的慈善家,于2000年設立了戈登/貝蒂·摩爾基金會,并捐贈了50億美元用于支持教育與環境項目。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52350瀏覽量

438611 -

英特爾

+關注

關注

61文章

10188瀏覽量

174283 -

半導體

+關注

關注

335文章

28771瀏覽量

235107 -

元器件

+關注

關注

113文章

4821瀏覽量

94719 -

摩爾定律

+關注

關注

4文章

638瀏覽量

79762

原文標題:延續摩爾定律的代價

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

摩爾定律終結,并不是真的到頭了

摩爾定律也適用于EPON芯片商用之路?

半導體行業的里程碑“摩爾定律”竟是這樣來的

摩爾定律推動了整個半導體行業的變革

摩爾定律,摩爾定律是什么意思

摩爾定律終結了嗎_摩爾定律或在2021終結

摩爾定律的終結真的要來了嗎

摩爾定律的終結真的要來了嗎

評論