如果FPGA沒有外部時(shí)鐘源輸入,可以通過調(diào)用STARTUP原語,來使用FPGA芯片內(nèi)部的時(shí)鐘和復(fù)位信號(hào),Spartan-6系列內(nèi)部時(shí)鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

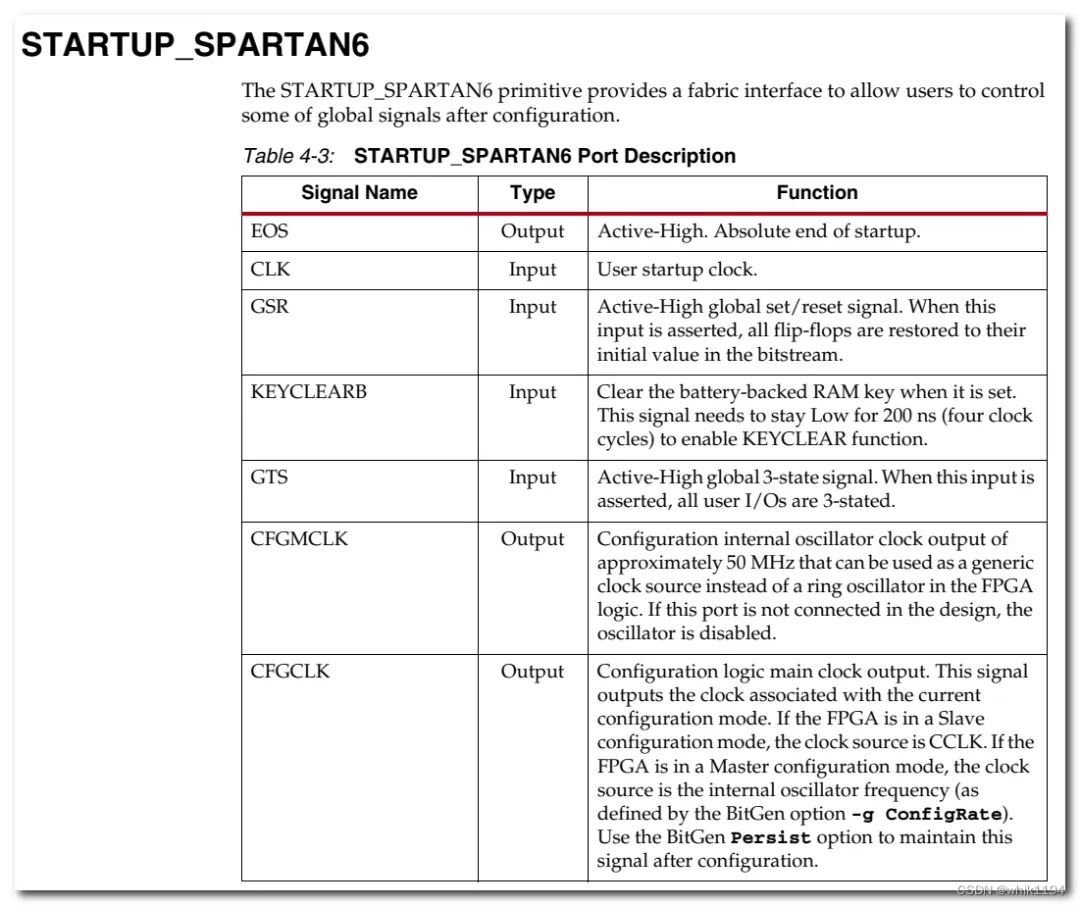

Spartan-6系列

wireclk_50m; wirerst_n; STARTUP_SPARTAN6STARTUP_SPARTAN6_inst( .CFGMCLK(clk_50m),//1-bitoutput:Configurationinternaloscillatorclockoutput. .EOS(rst_n),//1-bitoutput:ActivehighoutputsignalindicatestheEndOfConfiguration. );

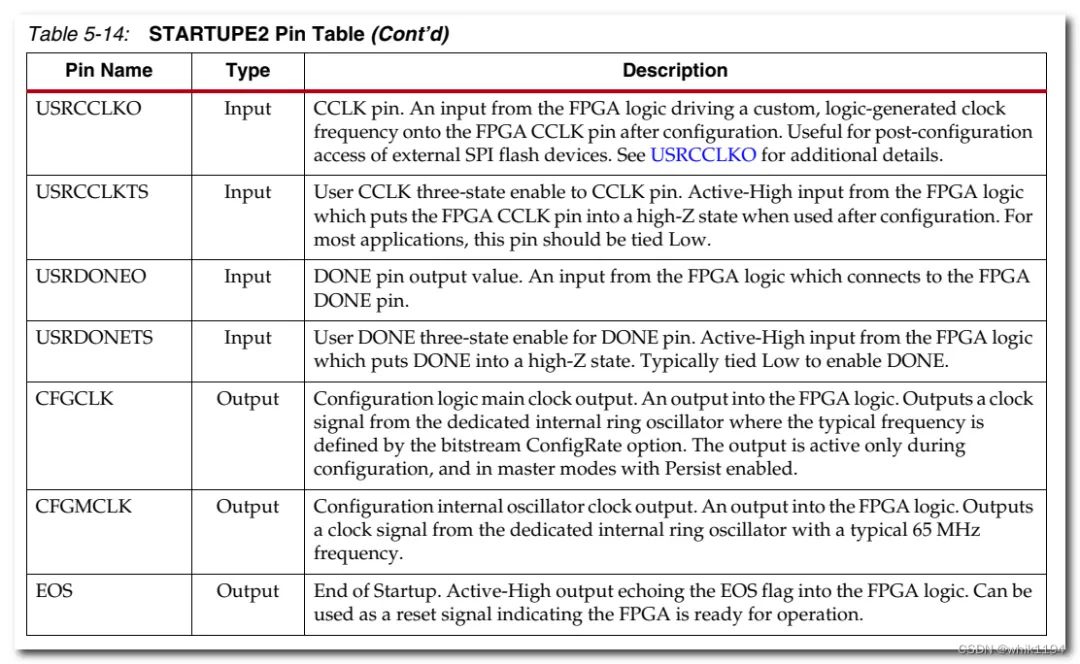

Artix-7(7系列)

wireclk_65m; wirerst_n; STARTUPE2STARTUPE2_ut0( .CFGMCLK(clk_65m),//1-bitoutput:Configurationinternaloscillatorclockoutput65MHz. .EOS(rst_n)//1-bitoutput:ActivehighoutputsignalindicatingtheEndOfStartup. );

分別可以參考文檔:

UG380:Spartan-6 FPGA Configuration

UG470:7 Series FPGAs Configuration

審核編輯:劉清

-

FPGA芯片

+關(guān)注

關(guān)注

3文章

249瀏覽量

40355 -

時(shí)鐘源

+關(guān)注

關(guān)注

0文章

98瀏覽量

16331 -

復(fù)位信號(hào)

+關(guān)注

關(guān)注

0文章

67瀏覽量

6587

原文標(biāo)題:Xilinx FPGA芯片內(nèi)部時(shí)鐘和復(fù)位信號(hào)使用

文章出處:【微信號(hào):mcu149,微信公眾號(hào):電子電路開發(fā)學(xué)習(xí)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

FPGA復(fù)位的可靠性設(shè)計(jì)方法

對于選擇同步化的異步復(fù)位的方案

基于Xilinx FPGA的復(fù)位信號(hào)處理

復(fù)位信號(hào)是什么意思?復(fù)位信號(hào)的作用?詳解Xilinx FPGA復(fù)位信號(hào)那些事

Xilinx FPGA的GTx的參考時(shí)鐘

Xilinx_FPGA_內(nèi)部結(jié)構(gòu)深入分析

FPGA設(shè)計(jì)中常用的復(fù)位設(shè)計(jì)

在FPGA開發(fā)中盡量避免全局復(fù)位的使用?(2)

Xilinx全局時(shí)鐘的使用和DCM模塊的使用

FPGA的理想的復(fù)位方法和技巧

Xilinx FPGA的同步復(fù)位和異步復(fù)位

Xilinx-DCM的使用方法技巧

Xilinx FPGA芯片內(nèi)部時(shí)鐘和復(fù)位信號(hào)使用方法

Xilinx FPGA芯片內(nèi)部時(shí)鐘和復(fù)位信號(hào)使用方法

評(píng)論