5.1.指令的本質

雖然把“總線”比喻成“高速公路”,但是兩者之間還是有很大的不同,在現實的高速公路上,汽車向著同一個方向前進,每個汽車有不同的目的地,在不同的路口下高速。但是在電路中,電子的傳輸速度是光速,信號會同時出現在所有的路口,也就是說不可能要求“總線”中的信號去哪個路口,不去哪個路口。

所以我們控制信號的手段是當數據信號在總線中的時候,可以通過控制哪些元件從“總線”中讀取信號或者控制哪些元件往總線中寫入數據的方式來達到控制整個電路運行的目的。

那么具體到電路中,應該如何實現控制信號進出總線呢?從第四章我們知道,存儲器(寄存器、內存)有兩個讀、寫兩個控制開關。讓我們好像找到了的“命門”,只要控制好這些讀、寫開關,當某個寄存器設置為讀,數據從寄存器傳導到總線,當某個寄存器設置為寫,實現把數據從總線讀入寄存器,如此就能控制好整個電路,讓它做我們想做的事情。

為了更加清楚的說明整個控制過程,我們再看看從內存中讀取數據相加的控制過程,具體計算步驟實現如下(表 5-1):

表 5-1 相加電路的實現步驟

| 步驟序號 | 步驟描述 | 設置 |

|---|---|---|

| 1 | 讀被加數 | 內存(M)的R=1;暫存寄存器(TR1)的W=1;其余開關=0 |

| 2 | 讀加數和相加一起 | 內存(M)的R=1;暫存寄存器(TR1)的R=1;暫存寄存器(TR2)的W=1;其余開關=0 |

| 3 | 保存結果 | 內存(M)的W=1;暫存寄存器(TR2)的R=1;其余開關=0 |

表中的每一行就是一個指令,指令是計算機程序發給計算機處理器的命令。每一個指令,我們通過完成幾個寄存器的讀寫設置,完成一個具有一定功能的動作組合。

5.2.指令寄存器

為了保存當前需要運行的指令,設置指令寄存器組,由指令操作碼和地址寄存器兩個8位寄存器組成。指令操作碼寄存器存放的指令的編號,通過指令譯碼器選擇執行的動作;地址寄存器指的是該指令執行過程中需要的內存地址。

圖 5-1 指令格式

表 5-2 電路支持的指令列表

| 操作碼 | 說明 |

|---|---|

| 0000 0000 | 讀取被加數 |

| 0000 0001 | 讀取加數,并相加 |

| 0000 0010 | 將相加的結果存儲內存 |

| 0000 0100 | 在常量寄存器中存入一個常量 |

| 0000 0101 | 把常量寄存器的數存到內存中 |

5.3.指令譯碼器

為了使得控制更加簡單,可以把每一個步驟(指令)設置一個開關,一鍵完成一個步驟。

進一步,可以在錯誤!未找到引用源。基礎上添加譯碼器,實現指令控制的電路。指令譯碼器的實現還是通過邏輯真值表來輔助設計。

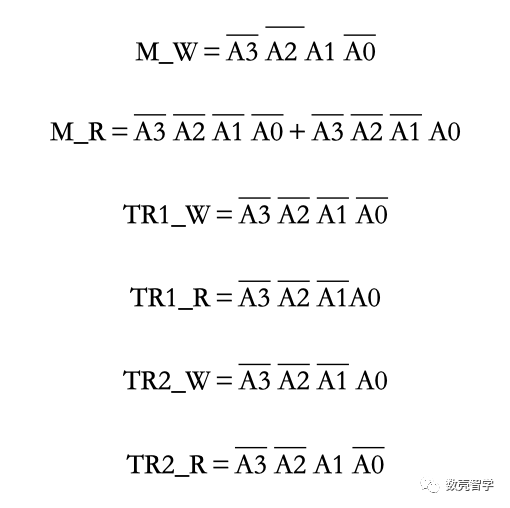

每個指令的操作碼對應多個寄存器的設置操作。比如從內存中讀取是指,并且把值放入加法的加數暫存器TR1中的指令,指令操作碼是 0000,需要將內存的R端口和加數暫存起TR1的W端口設置為1;執行加法的指令,指令操作碼是0001,需要同時設置M寄存器的R=1,暫存器TR1的R=1,暫存器TR2的W=1。根據(表 5-1),重新建立操作碼和寄存器設置的真值表如下表:

表 5-3 指令操作碼和設置動作的真值表

| 指令操作碼A3A2A1A0 | 指令描述 | 內存M | 加數暫存器TR1 | 和暫存器TR2 |

|---|---|---|---|---|

| W | R | W | R | W |

| 0 0 0 0 | 讀被加數 | 1 | 1 | |

| 0 0 0 1 | 讀加數,相加 | 1 | ||

| 0 0 1 0 | 存結果 | 1 |

邏輯表達式:

邏輯電路:

圖 5-2指令譯碼器電路圖

5.4.內存相加電路實現

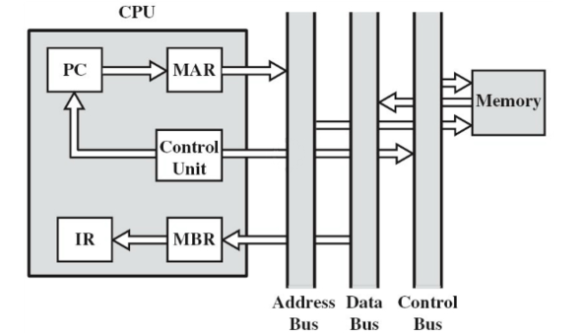

圖 5-3 基于內存的加法功能電路

圖 5-4 簡單內存示意圖

完成本章的內存相加功能,假設如圖 5-4 a、b、c的內存地址,讀取a、b的值,把相加的結果保存到c,完整指令步驟如下:

5.5.小節

本章提出一個如何將內存中的兩個數字相加的功能的問題,繪制以內存和加法器為主體的功能電路,同時,為了電路圖的布局更加的合理,引入“數據總線”、“地址總線”、“控制總線”的概念。

詳細的闡述指令的本質控制電路完成特定功能,解構指令譯碼器的內部解構,并提出增加指令寄存器,最后給出了較為完整的內存數據相加的邏輯電路。

但是本章對于指令寄存器的指令的加載和按順序執行指令的過程沒有闡述,下一章將重點解決這個問題。

-

寄存器

+關注

關注

31文章

5426瀏覽量

123683 -

內存

+關注

關注

8文章

3115瀏覽量

75057 -

指令

+關注

關注

1文章

615瀏覽量

36290 -

譯碼器

+關注

關注

4文章

312瀏覽量

51005

發布評論請先 登錄

一條指令的執行需要多少個時鐘周期

MOVX指令的執行過程

ARM與X862.ARM中指令的執行

淺談51單片機指令執行的過程

單片機MOVX指令執行時序深入分析

[STM32]STM32F407系列教程之三,c語言知識點鞏固 指令執行過程

![[STM32]STM32F407系列教程之三,c語言知識點鞏固 <b class='flag-5'>指令</b><b class='flag-5'>執行</b>過程](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

指令如何執行

指令如何執行

評論