傳統(tǒng)鎖相環(huán),環(huán)路帶寬、相位裕度與電荷泵電流、濾波器RC參數(shù)、分頻比、參考頻率等參數(shù)相關。

自偏置鎖相環(huán)通過將電荷泵電流、濾波器中的電阻等參數(shù)聯(lián)系在一起,可實現(xiàn)環(huán)路帶寬與參考頻率比值及阻尼因子近似為定值,進而解決傳統(tǒng)鎖相環(huán)面臨的問題。

**1. **自偏置鎖相環(huán)原理

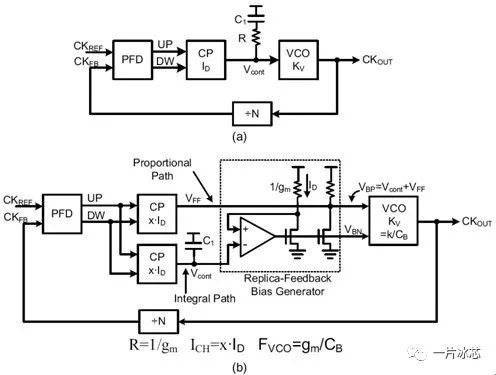

傳統(tǒng)二階鎖相環(huán)與自偏置鎖相環(huán)結構框圖分別如圖1(a)和(b)所示。

Fig1. 傳統(tǒng)鎖相環(huán)與自偏置鎖相環(huán)

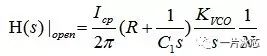

傳統(tǒng)的二階鎖相環(huán)的開環(huán)傳遞函數(shù)為:

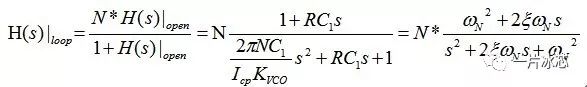

閉環(huán)傳遞函數(shù)為:

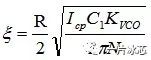

得到阻尼因子為:

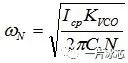

環(huán)路帶寬為:

為了環(huán)路穩(wěn)定性,要滿足ωN <ω ref /10;但是為了抑制VCO的相噪,又需要ωN盡可能大。對于傳統(tǒng)鎖相環(huán),濾波器中的R及電荷泵電流等參數(shù)一般都無法自適應調節(jié),環(huán)路帶寬和阻尼因子相對比較固定,從而限制了工作頻率。面對較寬的輸入?yún)⒖碱l率(如60820MHz),為了得到較好的噪聲性能,就需要做到帶寬跟隨輸入?yún)⒖碱l率,即實現(xiàn)ωN~ /ωref為常數(shù)。

為了實現(xiàn)ω N ~ /ωref ~和ξ是一個常數(shù),首先寫出RING-VCO的工作頻率表達式:

其中M為delay cell級數(shù),CB為VCO中delay cell輸出端寄生電容,ID為delay cell的尾電流,ω ref ~ =ωvco~ /N,為了使ωN /ωref是一個常數(shù),可以使I CP =xI D 。

但是此時阻尼因子會隨輸入?yún)⒖碱l率而變化,為了使阻尼因子不隨參考頻率而變化,可以在電荷泵電流用VCO的電流自偏置的前提下采用二極管連接的mos管做濾波器電阻,使其與1/sqrt(I D )成正比;為了實現(xiàn)濾波器中用二極管連接的mos管做電阻,需要使用兩個獨立的CP分別驅動電阻和電容,得到一條積分路徑、一條比例路徑,然后對兩條路徑上的電壓進行相加得到vctrl。

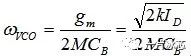

自偏置鎖相環(huán)應用框圖如圖2所示:

Fig2.自偏置鎖相環(huán)應用框圖

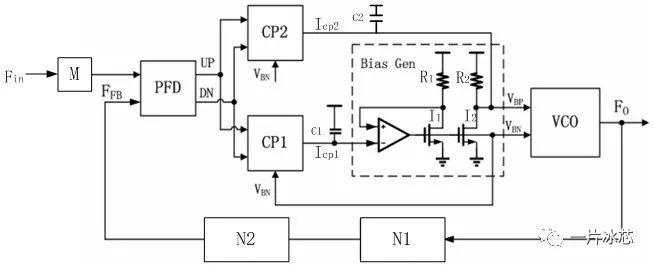

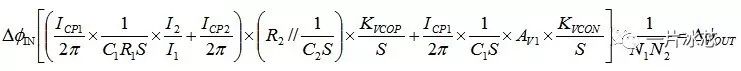

開環(huán)傳遞函數(shù)H(s)推導過程如下:

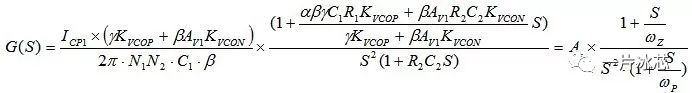

其中,AV1為CP1的輸出到VBN的小信號增益。設I CP2 =αI CP1 ,I 1 =βI 2 ,R 2 =γR 1 ,整理可得鎖相環(huán)的開環(huán)傳遞函數(shù)為:

其中

所以環(huán)路存在兩個在原點的極點,以及一個零點和一個非零極點。

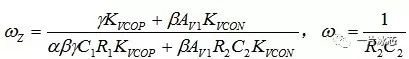

**2. **自偏置鎖相環(huán)設計指標

表1給出了自偏置鎖相環(huán)的設計指標

Table1. 自偏置鎖相環(huán)的設計指標

**3. **自偏置鎖相環(huán)測試結果

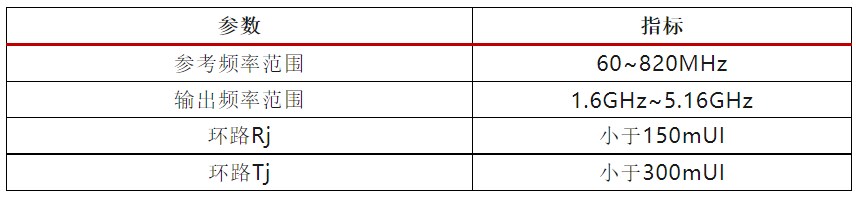

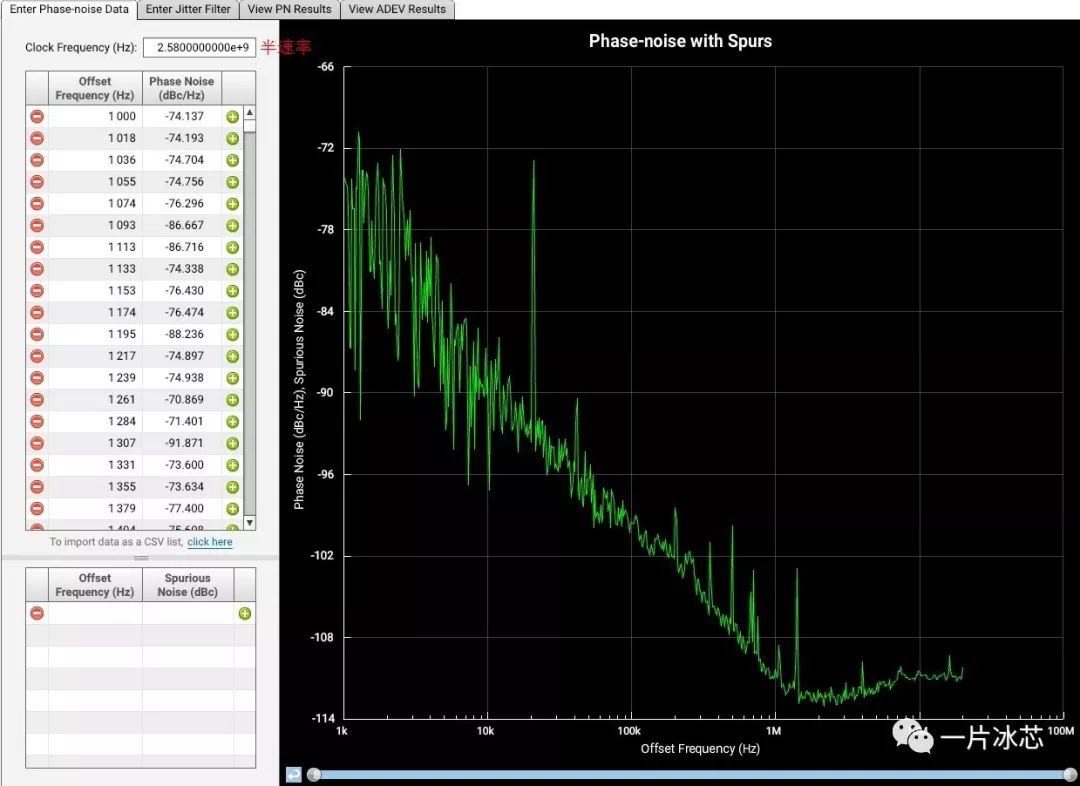

鎖相環(huán)時鐘無法直接測試,需要高速通道輸出。測試時通過TX端引出,TX數(shù)據(jù)給clock patten(010101),通過鎖相環(huán)時鐘打出, TX輸出數(shù)據(jù)眼圖可間接得到時鐘Rj。由于TX 并串轉換(PISO)采用的是半速率方式,用JitterLab積分時Clock Frequency要減半。

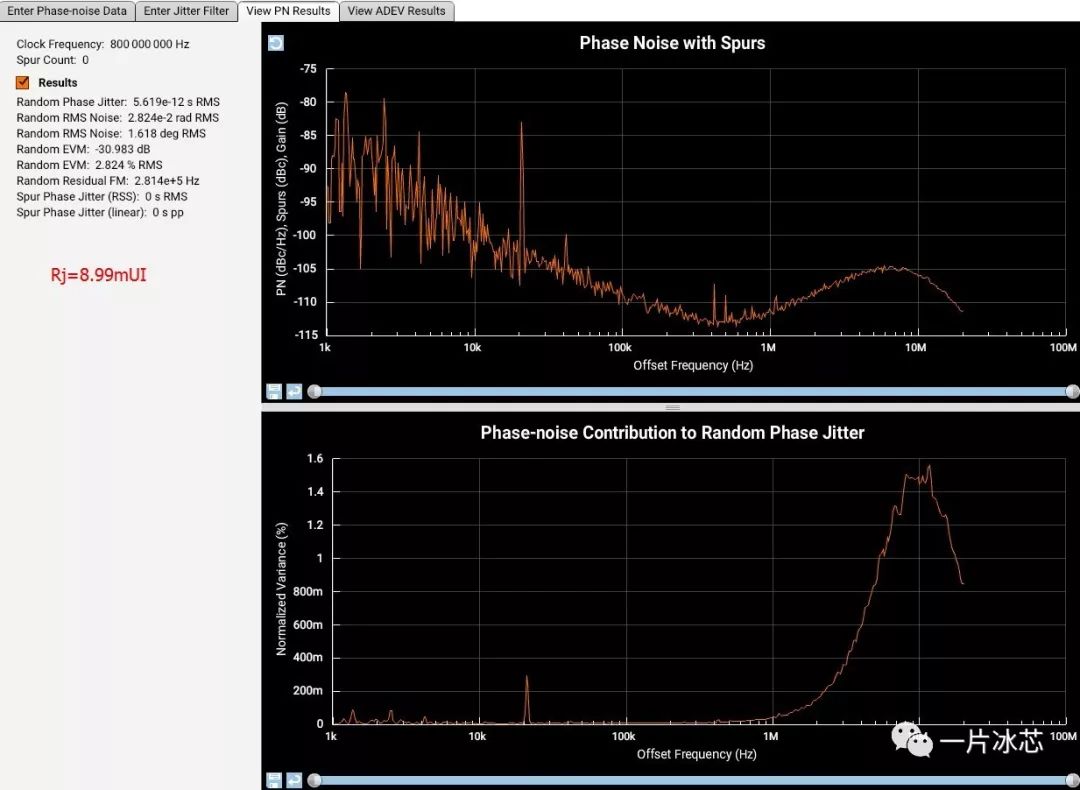

3.1 1.6GHz****相噪儀測試結果

Fig3. 相噪儀測試結果(導出到JitterLab工具)@1.6GHz

結論:Rj=8.99 x 14=126mUI<150mUI@BER=10e12,bitrate=1.6 GHz,滿足設計指標。

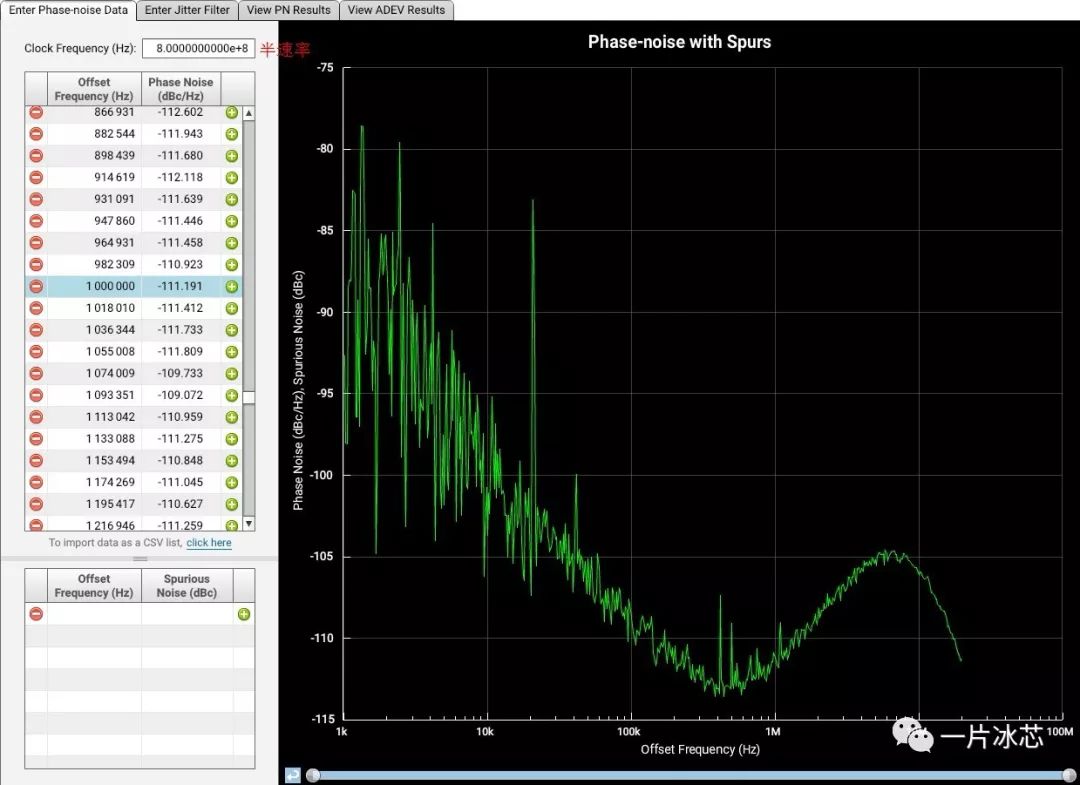

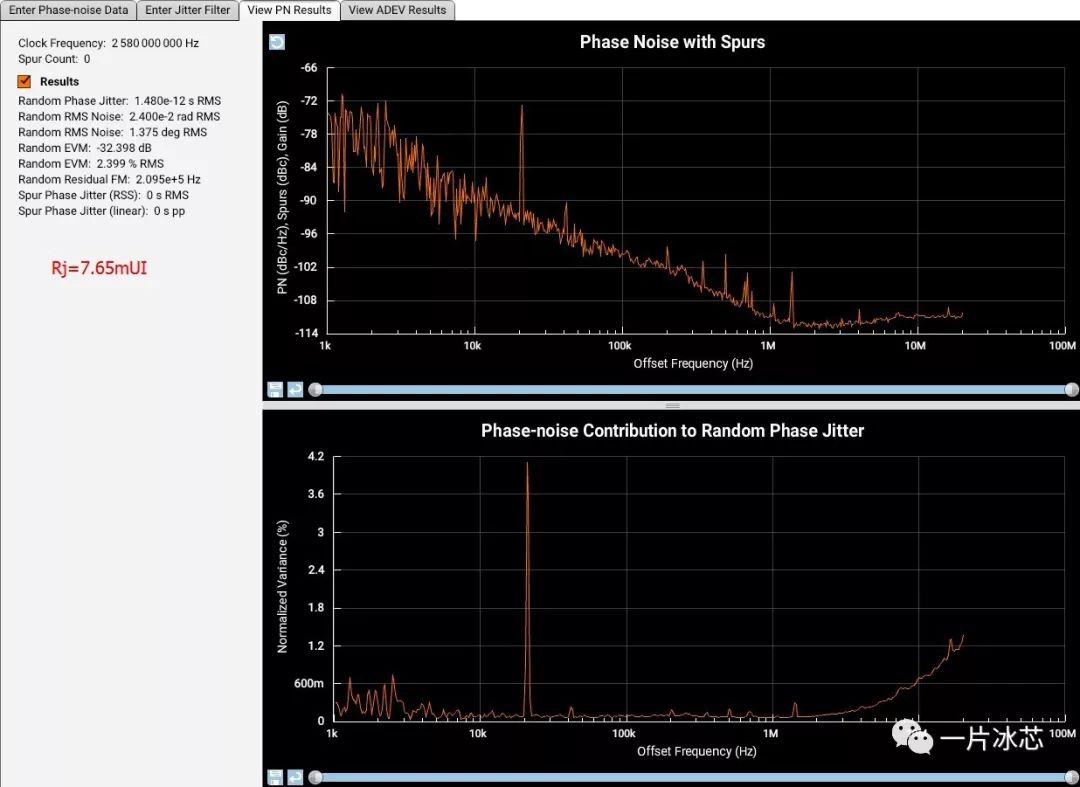

3.2 5.16GHz****相噪儀測試結果

Fig4. 相噪儀測試結果(導出到JitterLab工具)@5.16GHz

結論:Rj=7.65 x 14=107mUI<150mUI@BER=10e-12,bitrate=5.16 GHz,滿足設計指標。

**4. **自偏置鎖相環(huán)優(yōu)缺點

①頻率覆蓋范圍廣;

②特別適用于低壓場合;

③帶寬可跟隨參數(shù)頻率,阻尼因子近似恒定;

④雙電荷泵、濾波器電阻為有源電阻,環(huán)路較復雜;

⑤壓控振蕩器增益由兩路疊加而成。

-

鎖相環(huán)

+關注

關注

35文章

597瀏覽量

89571 -

濾波器

+關注

關注

162文章

8133瀏覽量

181880 -

VCO

+關注

關注

13文章

311瀏覽量

70157 -

電荷泵

+關注

關注

3文章

280瀏覽量

30081 -

壓控振蕩器

+關注

關注

10文章

164瀏覽量

29684

發(fā)布評論請先 登錄

什么是鎖相環(huán) 鎖相環(huán)的組成 鎖相環(huán)選型原則有哪些呢?

軟件鎖相環(huán)的設計與應用

模擬鎖相環(huán)應用實驗

鎖相環(huán)設計舉例

鎖相環(huán)原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

模擬鎖相環(huán),模擬鎖相環(huán)原理解析

鎖相環(huán)

詳解FPGA數(shù)字鎖相環(huán)平臺

自偏置鎖相環(huán)原理 自偏置鎖相環(huán)測試

自偏置鎖相環(huán)原理 自偏置鎖相環(huán)測試

評論