CMOS器件的輸入信號上升時間或下降時間統(tǒng)稱為輸入轉(zhuǎn)換時間,輸入轉(zhuǎn)換時間過長也稱為慢CMOS輸入。如果輸入信號上升時間過長,超過器件手冊允許的最大輸入轉(zhuǎn)換時間,則有可能在器件內(nèi)部引起大的電流浪涌,造成器件損壞或引起器件輸出電平翻轉(zhuǎn)(輸入原本為0,輸出為1;或者相反情況)。

1.慢CMOS輸入或浮空CMOS輸入的特征

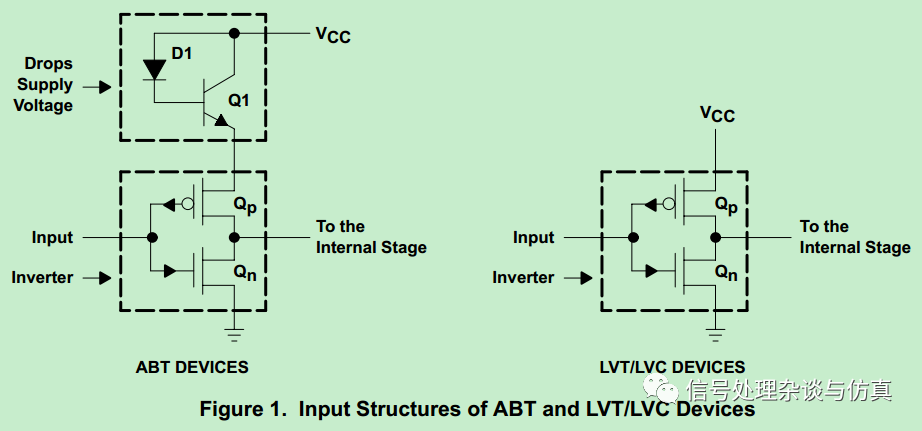

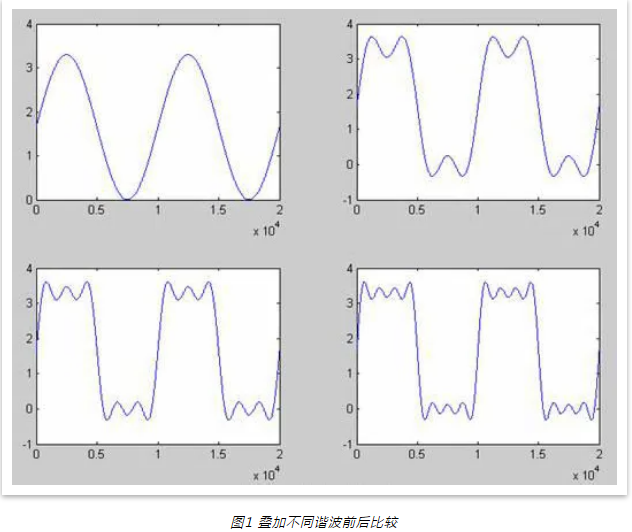

CMOS和BiCMOS系列器件都有一個CMOS輸入結(jié)構(gòu)。該結(jié)構(gòu)是一個反相器(包括連接VCC的一個p溝道晶體管和連接GND的一個n溝道晶體管),如圖1所示。

備注:圖1中的ABT器件采用BiCMOS技術(shù),Q1是雙極晶體管,Qp和Qn是CMOS管子,ABT器件的輸入為CMOS反相器(又叫倒相器、非門(NOT gate,非電路)和邏輯否定電路);關(guān)于CMOS反相器,參見文檔《CMOS功耗和Cpd計(jì)算》。

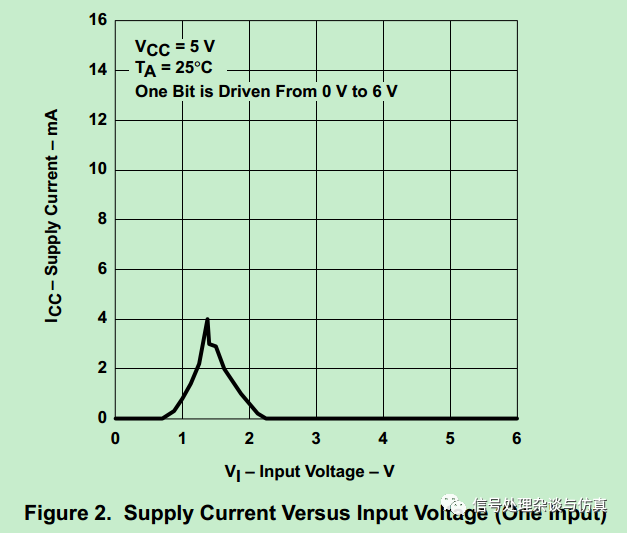

當(dāng)輸入為低電平,p溝道晶體管導(dǎo)通,n溝道晶體管截止,電流從VCC流出,節(jié)點(diǎn)被拉高;當(dāng)輸入為高電平,p溝道晶體管截止,n溝道晶體管導(dǎo)通,電流流入GND,節(jié)點(diǎn)被拉低。在兩種情況下,沒有電流從VCC流到GND。然而,當(dāng)從一個狀態(tài)轉(zhuǎn)換到另一個狀態(tài)時,輸入穿過閾值區(qū)域,使得n溝道晶體管和p溝道晶體管同時導(dǎo)通,在VCC與GND之間形成電流路徑。該電流浪涌可能是破壞性的,它取決于輸入在閾值區(qū)域(0.8~2V)的時間長度。每個輸入的供電電流(ICC)能夠升到幾mA,ICC在輸入(VI)約為1.5V時最大,見圖2。

備注:當(dāng)輸入穿過閾值區(qū)域,在VCC與GND之間的電流路徑也叫直通電流,直通電流會造成器件的瞬態(tài)功耗,詳情參見文檔《CMOS功耗和Cpd計(jì)算》。從圖2中看出,當(dāng)輸入電壓在閾值區(qū)域內(nèi)(0.8~2V)時,供電電流存在浪涌。

當(dāng)開關(guān)狀態(tài)在數(shù)據(jù)手冊指定的輸入轉(zhuǎn)換時間限值內(nèi)時,電流浪涌不是問題。對于具體器件,在數(shù)據(jù)手冊的推薦工作條件表中指定輸入轉(zhuǎn)換時間限值,例子如圖3所示。

2.慢輸入沿率

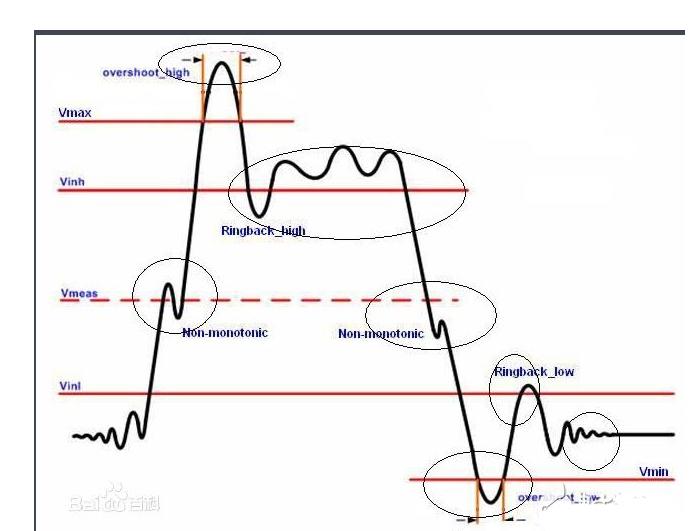

隨著速度增加,邏輯器件已經(jīng)對慢輸入沿率更敏感。慢輸入沿率與噪聲(當(dāng)輸出開關(guān)時,在電源上產(chǎn)生)一起能夠引起大量輸出錯誤或振蕩。如果沒有用到的輸入管腳懸空或者未保持在一個有效的邏輯電平值,類似現(xiàn)象也能夠發(fā)生。

這些功能問題是由在器件電源系統(tǒng)引起的電壓瞬態(tài)造成的,在開關(guān)過程中,當(dāng)輸出負(fù)載電流(IO)流過寄生引線電感時產(chǎn)生電壓瞬態(tài),見圖4。

因?yàn)槠骷膬?nèi)部電源節(jié)點(diǎn)用作整個集成電路的電壓參考,感應(yīng)電壓尖峰VGND影響出現(xiàn)在內(nèi)部門結(jié)構(gòu)的信號方式【指VI′=VI-VGND】。例如,當(dāng)器件地節(jié)點(diǎn)的電壓升高時,輸入信號VI′看起來在幅度上減小。如果發(fā)生閾值違背(指輸入信號原本為高電平,由于VI′小于器件輸入端高電平的閾值VIH,造成輸出錯判為低電平;反之亦成立),這種不期望現(xiàn)象隨后能夠錯誤地改變輸出。

對于一個慢的輸入上升沿,如果在GND的電壓變化足夠大【VGND】,器件的相對輸入信號VI′看起來被驅(qū)動返回穿過輸入閾值區(qū)(0.8~2V),輸出開始從相反方向開關(guān)(指0變成1,1變成0)。如果最壞情況(所有輸出同時開關(guān),造成瞬態(tài)負(fù)載電流較大)頻繁發(fā)生(參見圖2和圖3),慢輸入沿被重復(fù)地驅(qū)動返回穿過閾值區(qū),引起輸出振蕩。因此,不應(yīng)該違背器件的最大輸入轉(zhuǎn)換時間,也就不會造成對電路或外部封裝的損壞。

-

CMOS

+關(guān)注

關(guān)注

58文章

5997瀏覽量

238235 -

反相器

+關(guān)注

關(guān)注

6文章

315瀏覽量

44095 -

晶體管

+關(guān)注

關(guān)注

77文章

9990瀏覽量

140862 -

輸入信號

+關(guān)注

關(guān)注

0文章

472瀏覽量

12852 -

CMOS器件

+關(guān)注

關(guān)注

0文章

72瀏覽量

11825

發(fā)布評論請先 登錄

示波器的那些事-示波器上升時間

數(shù)字電路測量示波器探頭的上升時間和帶寬

關(guān)于信號上升時間和傳輸延時的關(guān)系

BOB示波器信號上升時間的劣化

BOB示波器輸入信號上升時間的測量

信號完整性分析:信號上升時間

高速pcb設(shè)計(jì)中的信號上升時間是如何定義的

淺談?wù)袷?b class='flag-5'>上升時間及影響

信號頻率和上升時間的關(guān)系

請問示波器怎么測量波形上升時間?

信號上升時間與帶寬的關(guān)系 一文看懂!!!

CMOS器件的輸入信號上升時間為什么不能太長?

CMOS器件的輸入信號上升時間為什么不能太長?

評論