邏輯單元在FPGA器件內(nèi)部,用于完成用戶邏輯的最小單元

邏輯單元在ALTERA叫作(Logic Element,LE)LE,在XILNX中叫作LC(LOGIC CELL).

1.邏輯單元與邏輯陣列

邏輯單元(Logic Element,LE)在FPGA器件內(nèi)部,用于完成用戶邏輯的最小單元。一個(gè)邏輯陣列包含16個(gè)邏輯單元以及一些其他資源, 在一個(gè)邏輯陣列內(nèi)部的16個(gè)邏輯單元有更為緊密的聯(lián)系,可以實(shí)現(xiàn)特有的功能。

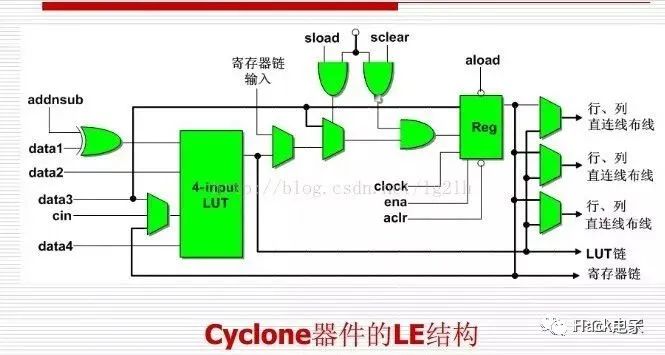

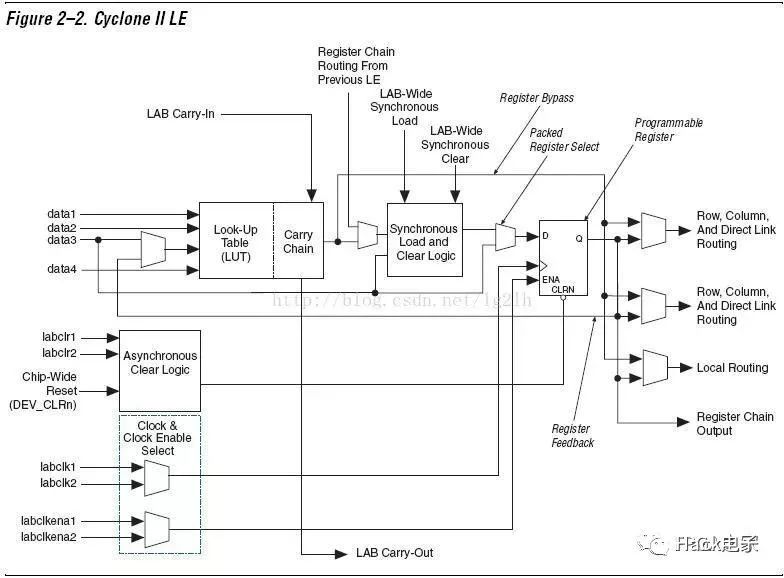

一個(gè)邏輯單元主要由以下部件組成:一個(gè)四輸入的查詢表(LookUp Table,LUT),一個(gè)可編程的寄存器,一條進(jìn)位鏈,一條寄存器級(jí)連鏈。

1、查詢表:用于完成用戶需要的邏輯功能,CYCLONEⅡ系列的查詢表是4輸入1輸出的,可以完成任意4輸入1輸出的組合邏輯。

2、可編程寄存器:可以配置成D觸發(fā)器,T觸發(fā)器,JK觸發(fā)器,SR觸發(fā)器。每個(gè)寄存器包含4個(gè)輸入信號(hào),數(shù)據(jù)輸入、時(shí)鐘輸入、時(shí)鐘使能、復(fù)位輸入。

一個(gè)邏輯單元包含3個(gè)輸出,兩個(gè)用于驅(qū)動(dòng)行連接、列連接、直接連接,另外一個(gè)用于驅(qū)動(dòng)本地互聯(lián)。這三個(gè)輸出是相互獨(dú)立的。輸出信號(hào)可以來(lái)自于查詢表也可以來(lái)自于寄存器。

一個(gè)LE主要由兩部分組成:查找表LUT+可編程寄存器

1.本地互連通路

是邏輯陣列的重要組成部分,芯片級(jí)設(shè)計(jì)思路上的考慮與節(jié)省我們就不討論,從實(shí)際運(yùn)用出發(fā),直接看看這個(gè)互連通路是干什么用的。本地互連通路提供了一種邏輯陣列內(nèi)部的連接方式, 邏輯陣列內(nèi)部還包含一種對(duì)外的高速連接通路,稱之為直接連接通路。

直接連接通路連接的是相鄰的邏輯陣列,或者與邏輯陣列相鄰的M4K存儲(chǔ)器塊、乘法器、鎖相環(huán)等。

CYCLONEⅡ系列FPGA的邏輯單元有兩種工作模式:普通模式和算數(shù)模式。普通模式適合于一般的邏輯運(yùn)算。算數(shù)模式適用于實(shí)現(xiàn)加法器、計(jì)數(shù)器、累加器、比較器等。

邏輯陣列的主體是16個(gè)邏輯單元,另外還有一些邏輯陣列內(nèi)部的控制信號(hào)以及互連通路。前面所講的互聯(lián)通路和直接連接通路就是邏輯陣列中的部分。

邏輯陣列還包括一些控制信號(hào):兩個(gè)時(shí)鐘信號(hào),兩個(gè)時(shí)鐘使能信號(hào),兩個(gè)異步復(fù)位信號(hào),一個(gè)同步復(fù)位信號(hào),一個(gè)同步加載信號(hào)。

2.內(nèi)部連接通路

在FPGA內(nèi)部存在各種連接通路,連接不同的模塊,比如邏輯單元之間、邏輯單元與存儲(chǔ)器之間。FPGA內(nèi)部資源是按照行列的形式排列的,所以連接通路也分為行列的。行連接又分為R4連接、R24連接和直接連接。R4連接就是連接4個(gè)邏輯陣列,或者3個(gè)邏輯陣列和1個(gè)存儲(chǔ)塊, 或者3個(gè)邏輯陣列和1個(gè)乘法器。簡(jiǎn)單地說(shuō)就是連接4個(gè)模塊吧。R24就是24個(gè)模塊。列連接是C4,C16,含義不用說(shuō)了吧,是連接4個(gè)模塊和16個(gè)模塊。

ALTERA的LE內(nèi)部結(jié)構(gòu)如圖

*

*

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21960瀏覽量

614066 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123327 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12775 -

邏輯單元

+關(guān)注

關(guān)注

0文章

25瀏覽量

5214

原文標(biāo)題:FPGA基礎(chǔ)之邏輯單元的基本結(jié)構(gòu)

文章出處:【微信號(hào):ZYNQ,微信公眾號(hào):ZYNQ】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于BIST利用ORCA結(jié)構(gòu)測(cè)試FPGA邏輯單元的方法

FPGA學(xué)習(xí)筆記-關(guān)于FPGA資源

FPGA學(xué)習(xí)筆記匯總(7.13更新)

【案例分享】玩轉(zhuǎn)FPGA必學(xué)的復(fù)雜邏輯設(shè)計(jì)

時(shí)序邏輯:FPGA/ASIC電路結(jié)構(gòu)

FPGA硬件基礎(chǔ)知識(shí)FPGA的邏輯單元工程文件免費(fèi)下載

FPGA硬件基礎(chǔ)之FPGA的邏輯單元的工程文件免費(fèi)下載

Altera FPGA CPLD學(xué)習(xí)筆記

FPGA學(xué)習(xí)筆記:邏輯單元的基本結(jié)構(gòu)

FPGA學(xué)習(xí)筆記:邏輯單元的基本結(jié)構(gòu)

評(píng)論