**1 **技術背景

講負壓之前先介紹兩個技術背景,以便更好地理解芯片中為什么需要負壓。

**1.1 **高速緩存

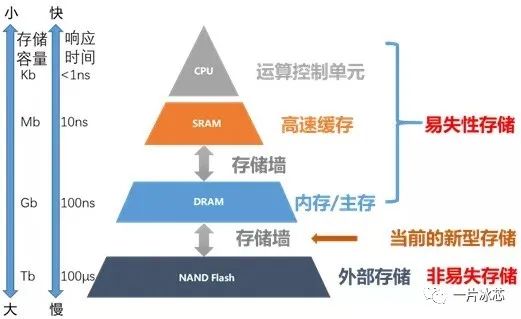

SRAM是目前最成熟的易失性高速存儲器,通常由6管(6T)實現數據的讀寫,可以用做CPU和內存(DRAM)之間的高速緩存。NAND Flash是一種非易失性存儲,你電腦、手機中的照片或文件就存儲在Flash中。

DRAM速度介于SRAM和Flash之間,也是一種易失性存儲器。常見存儲架構呈金字塔型,如圖1所示。近年以美國公司Everspin和Crossbar為代表的MRAM和RRAM逐漸走向產品化。

MRAM和RRAM特點是速度快、非易失、與CMOS工藝兼容。現代存儲架構之所以采用圖1所示,是因為設備中有的地方要高速,有的地方要大容量、非易失,說白了就是需求不同。MRAM和RRAM具有SRAM的高速和Flash的非易失,但Everspin和Crossbar產品目錄中最大容量只有1GB,未來如果能把容量做大、成本做低,大有改變現代存儲架構之勢。

為了進一步提高6T SRAM的寫入速度,在寫入數據時在bit line引入負壓,以加快1到0的放電速度。

Fig1. 常見存儲架構

1.2****閾值電壓調整

調整FDSOI工藝中RBB器件背柵電位可實現閾值電壓可調,進而實現低功耗。其中PMOS和NMOS背柵電位從0→+2V和0→-2V變化時閾值電壓逐漸增大,這就是負壓在IC中的另一個應用。

2 高速SRAM****讀寫電路

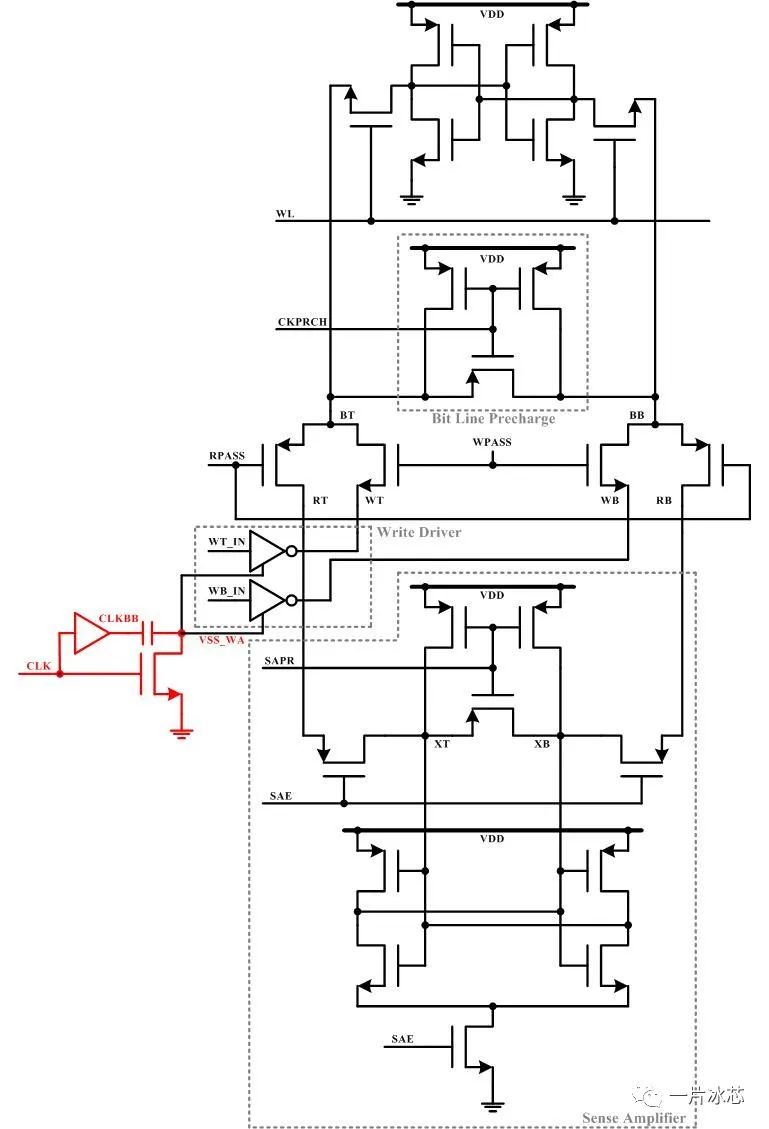

圖2給出了1 bit高速SRAM的讀寫電路 ,其中最上面的6個管子為前邊提到的6T存儲單元,最下邊的靈敏放大器(Sense Amplifier)用于數據的讀取,中間包含寫驅動(Write Driver)電路、預充電路以及WPASS和RPASS通路。為提高速度,數據寫入和讀出6T memory cell之前都要進行預充,即把BT、BB、XT和XB預充到高電平。

數據寫入時WPASS和RPASS都置高,通過WT_IN和WB_IN對6T memory cell寫入數據。數據讀出時WPASS和RPASS都置低,通過靈敏放大器讀出6T memory cell中存儲的數據。寫入和讀出時WL都要打開,預充時WL都要關閉。

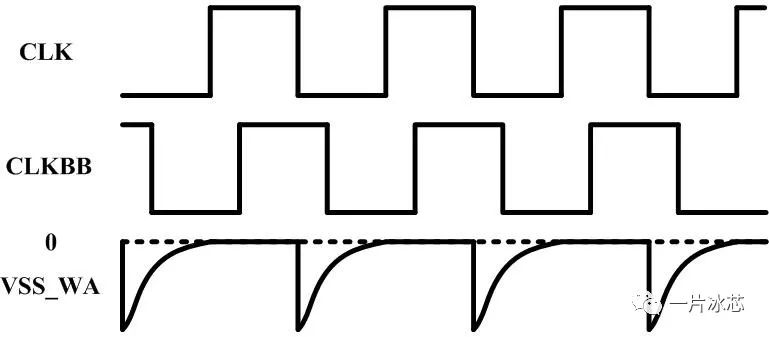

圖2左側紅色部分為負脈沖產生電路,利用電容兩端電壓不能突變這一特性產生的負脈沖VSS_WA作為Write Driver的GND,在WL開啟瞬間給6T memory cell提供一條快速放電通路,以提高寫入速度,時序圖如圖3所示。

Fig2. 高速SRAM讀寫電路

Fig3. 負脈沖產生時序圖

**3 **背柵電位調整電路

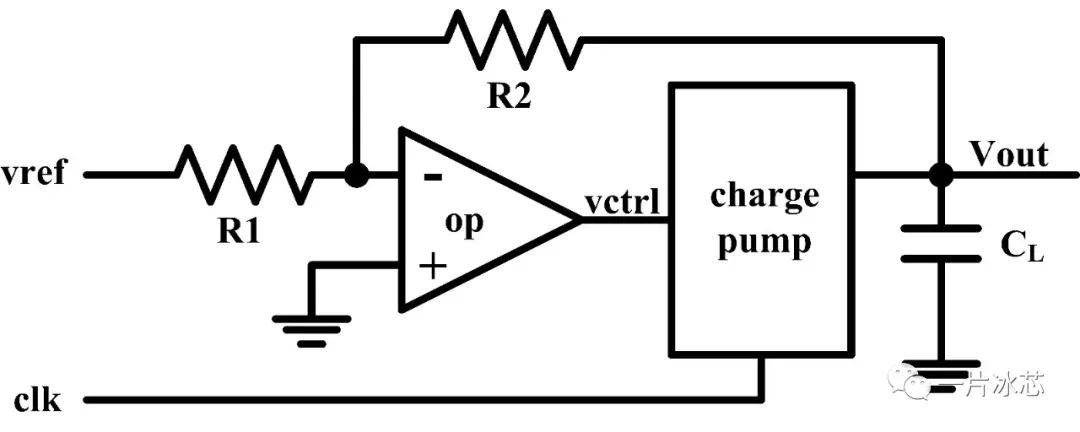

圖4給出了帶負反饋的電荷泵電路,用于產生精確的負電壓。調整vref大小即可改變Vout值。

Fig4. 背柵電位調整電路

根據負反饋原理,運放負端為虛地點,有如下表達式成立:

(vref-0)/R1=(0-Vout)/R2

Vout=-(R2/R1)*vref

假設vref為0.8V,R2/R1為2.5,Vout為-2V。Vout可用于調整FDSOI工藝RBB器件N管的背柵電位。圖4中的電荷泵需要多級級聯,以解決器件耐壓問題。

**4 **思考與討論

① 圖2 SRAM讀寫操作之前把BT、BB、XT、XB預充到VDD為什么可以提高讀寫速度?

② 圖2 靈敏放大器中的SAE與WL同時開啟可以嗎?

③ 如何提高讀取速度?

④ WPASS通路為什么用N管?RPASS通路為什么用P管?

⑤ 讀的時候為什么需要用靈敏放大器?

⑥ 圖4電荷泵如何實現?

⑦ 參考圖4你能否設計一個電路得到+2V電壓?

⑧ 圖4能否改成自適應結構?自適應調整器件背柵電位,以監測PVT變化,進而平衡速度和功耗。

-

放大器

+關注

關注

145文章

14103瀏覽量

216300 -

NAND

+關注

關注

16文章

1719瀏覽量

137822 -

CMOS工藝

+關注

關注

1文章

59瀏覽量

15885 -

電容電壓

+關注

關注

0文章

76瀏覽量

11433 -

SRAM存儲器

+關注

關注

0文章

88瀏覽量

13585

發布評論請先 登錄

高頻變壓器中傳導EMI產生機理

電源擾動及地彈噪聲的產生機理

轉子磁場的產生機理及在空間的分布

分析開關電源電磁干擾的各種產生機理

電磁干擾的產生機理資料下載

枕頭缺陷的產生機理和原因分析

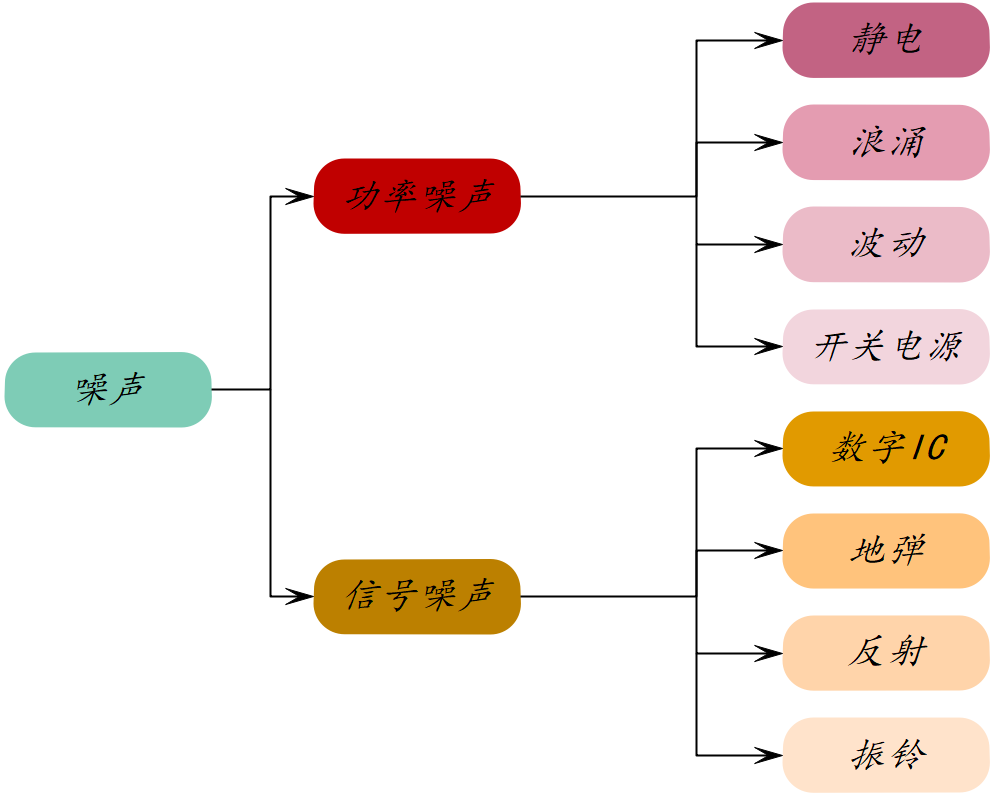

簡述噪聲的產生機理和來源

聊聊芯片中的負壓產生機理及其應用

聊聊芯片中的負壓產生機理及其應用

評論