本文繼續(xù)簡(jiǎn)單介紹一下基于FPGA的以太網(wǎng)ARP通信,該項(xiàng)目主要用于實(shí)現(xiàn)FPGA端以太網(wǎng)接口和上位機(jī)進(jìn)行ARP請(qǐng)求和應(yīng)答的功能。

RGMII接口

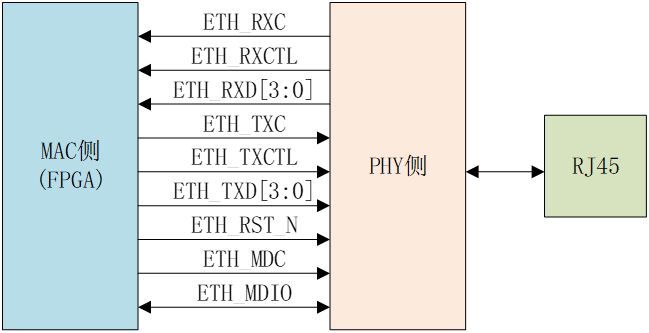

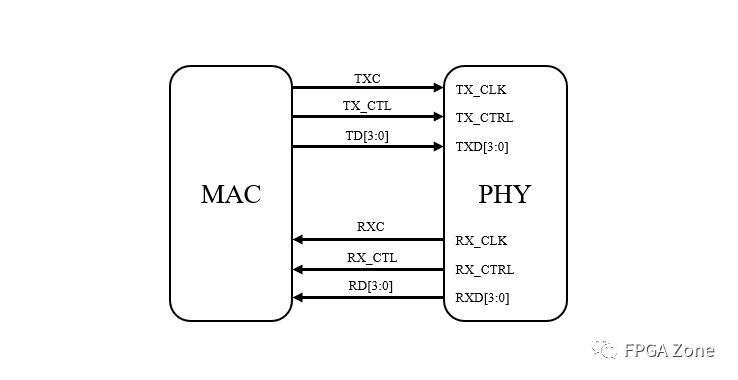

以太網(wǎng)的通信離不開物理層PHY芯片的支持,以太網(wǎng)MAC和PHY之間有一個(gè)接口,常用的接口有MII、RMII、GMII、RGMII等。

MII (媒體獨(dú)立接口):MII支持10Mbps和100Mbps的操作,數(shù)據(jù)位寬為4位,在100Mbps傳輸速率下,時(shí)鐘頻率為25Mhz。

RMII (Reduced MII):RMII是MII的簡(jiǎn)化版,數(shù)據(jù)位寬為2位,在100Mbps傳輸速率下,時(shí)鐘頻率為50Mhz。

GMII (Gigabit MII):GMII接口向下兼容MII接口,支持10Mbps、100Mbps和1000Mbps的操作,數(shù)據(jù)位寬為8位,在1000Mbps傳輸速率下,時(shí)鐘頻率為125Mhz。

RGMII (Reduced GMII):RGMII是GMII的簡(jiǎn)化版,數(shù)據(jù)位寬為4位,在1000Mbps傳輸速率下,時(shí)鐘頻率為125Mhz,在時(shí)鐘的上下沿同時(shí)采樣數(shù)據(jù)。在100Mbps和10Mbps通信速率下,為單個(gè)時(shí)鐘沿采樣。

在千兆以太網(wǎng)中,常用的接口為RGMII和GMII接口。RGMII接口的優(yōu)勢(shì)是同時(shí)適用于10M/100M/1000Mbps通信速率,同時(shí)占用的引腳數(shù)較少。但RGMII接口也有其缺點(diǎn),就是在PCB布線時(shí)需要盡可能對(duì)時(shí)鐘、控制和數(shù)據(jù)線進(jìn)行等長(zhǎng)處理,且時(shí)序約束相對(duì)也更為嚴(yán)格。

ETH_RXC :接收數(shù)據(jù)參考時(shí)鐘,1000Mbps速率下,時(shí)鐘頻率為125MHz,時(shí)鐘為上下沿同時(shí)采樣;100Mbps速率下,時(shí)鐘頻率為25MHz;10Mbps速率下,時(shí)鐘頻率為2.5MHz,ETH_RXC由PHY側(cè)提供。

ETH_RXCTL (ETH_RX_DV):接收數(shù)據(jù)控制信號(hào)。

ETH_RXD :四位并行的接收數(shù)據(jù)線。

ETH_TXC :發(fā)送參考時(shí)鐘,1000Mbps速率下,時(shí)鐘頻率為125MHz,時(shí)鐘為上下沿同時(shí)采樣;100Mbps速率下,時(shí)鐘頻率為25MHz;10Mbps速率下,時(shí)鐘頻率為2.5MHz,ETH_TXC由MAC側(cè)提供。

ETH_TXCTL (ETH_TXEN):發(fā)送數(shù)據(jù)控制信號(hào)。

ETH_TXD :四位并行的發(fā)送數(shù)據(jù)線。

ETH_RESET_N :芯片復(fù)位信號(hào),低電平有效。

ETH_MDC :數(shù)據(jù)管理時(shí)鐘,該引腳對(duì)ETH_MDIO信號(hào)提供了一個(gè)同步的時(shí)鐘。

ETH_MDIO :數(shù)據(jù)輸入/輸出管理,該引腳提供了一個(gè)雙向信號(hào)用于傳遞管理信息。

RGMII接口時(shí)序

PHY芯片的RGMII接口時(shí)序,其時(shí)鐘、控制信號(hào)和數(shù)據(jù)的對(duì)齊方式,一般由MDIO接口或者硬件上的特殊引腳進(jìn)行配置。

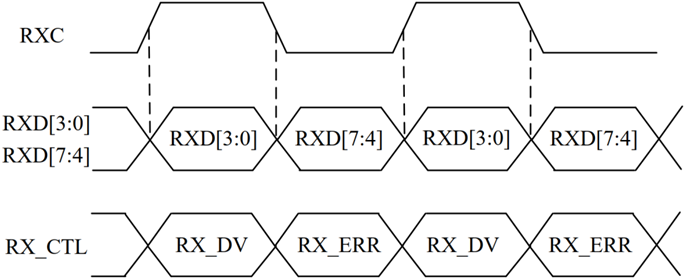

接收時(shí)序

RXC的上下邊沿與RXD和RX_CTL信號(hào)對(duì)齊,相位相同。

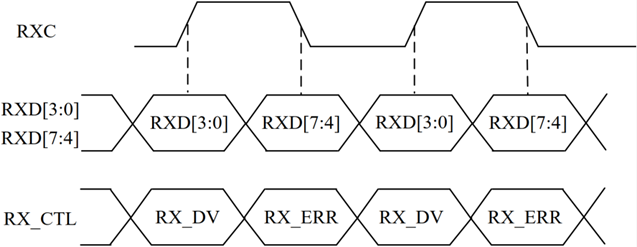

RGMII接收端口時(shí)鐘和控制/數(shù)據(jù)信號(hào)增加延時(shí)的時(shí)序圖如下:

RXC的上下邊沿與RXD和RX_CTL信號(hào)的中間位置對(duì)齊,RXC的時(shí)鐘周期為8ns,單個(gè)高電平或者低電平為4ns,RXC相對(duì)于RXD和RX_CTL延時(shí)約2ns。

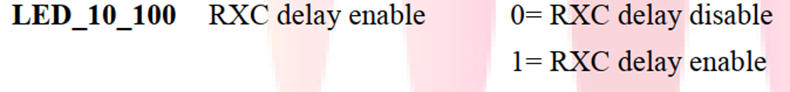

YT8511 RGMII接收端口的信號(hào)對(duì)齊模式由硬件上的特殊引腳外接上下拉電阻進(jìn)行配置,如下圖所示,當(dāng)管腳LED_10_100接上拉電阻時(shí),表示RXC時(shí)鐘相對(duì)于RXD信號(hào),會(huì)增加約2ns的延時(shí)。

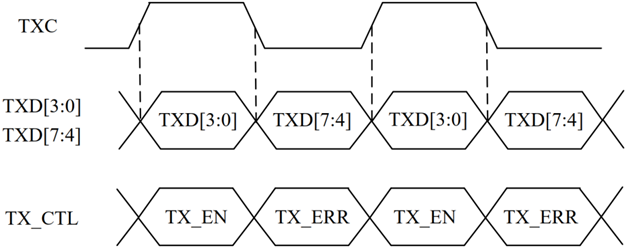

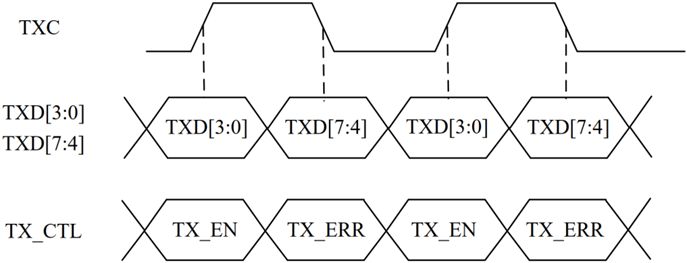

發(fā)送時(shí)序

RGMII發(fā)送端口正常模式下,需要滿足TXC的上下邊沿與TXD和TX_CTL信號(hào)對(duì)齊,相位相同。YT8511在硬件上面沒有做TX端的delay模式,可根據(jù)實(shí)際情況,選擇是否在代碼中進(jìn)行延時(shí)(因?yàn)橐话銓?duì)端設(shè)備的接收端會(huì)有延時(shí)處理的功能,因此發(fā)送端也可以不延時(shí)),延時(shí)后的時(shí)序圖如下所示:

由RGMII的接口時(shí)序可知,RGMII發(fā)送端口在TXC時(shí)鐘的上升沿傳輸TXD的低4位和TX_CTL的使能信號(hào);下降沿傳輸TXD的高4位和TX_CTL的錯(cuò)誤信號(hào)(實(shí)際上是使能信號(hào)和錯(cuò)誤信號(hào)的異或值);RGMII接收端口在RXC時(shí)鐘的上升沿傳輸RXD的低4位和RX_CTL的使能信號(hào);下降沿傳輸RXD的高4位和RX_CTL的錯(cuò)誤信號(hào)(實(shí)際上是使能信號(hào)和錯(cuò)誤信號(hào)的異或值)。

實(shí)現(xiàn)功能

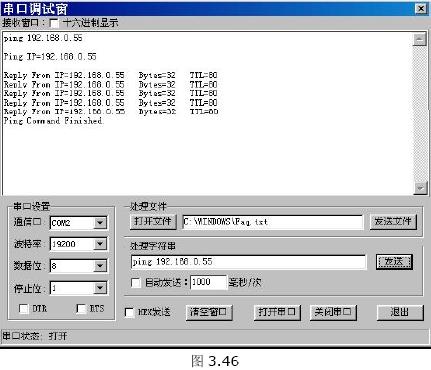

該項(xiàng)目采用FPGA端以太網(wǎng)接口,和上位機(jī)實(shí)現(xiàn)ARP請(qǐng)求和應(yīng)答的功能。當(dāng)上位機(jī)發(fā)送ARP請(qǐng)求時(shí),F(xiàn)PGA返回ARP應(yīng)答數(shù)據(jù),當(dāng)FPGA發(fā)送ARP請(qǐng)求時(shí),上位機(jī)返回ARP應(yīng)答數(shù)據(jù)。

功能測(cè)試

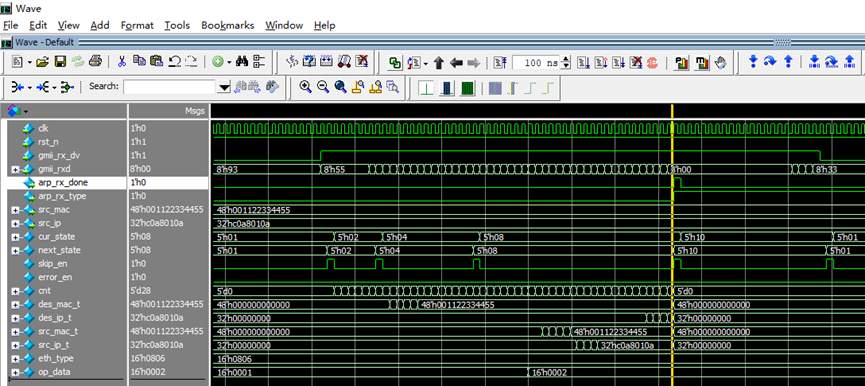

ARP接收

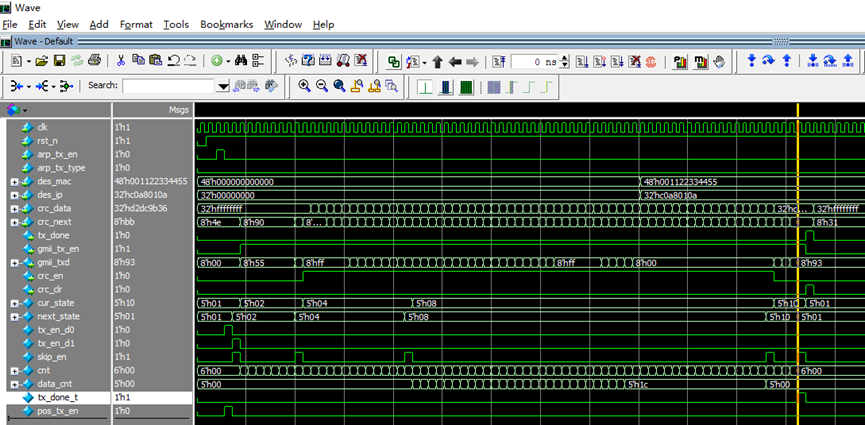

ARP發(fā)送

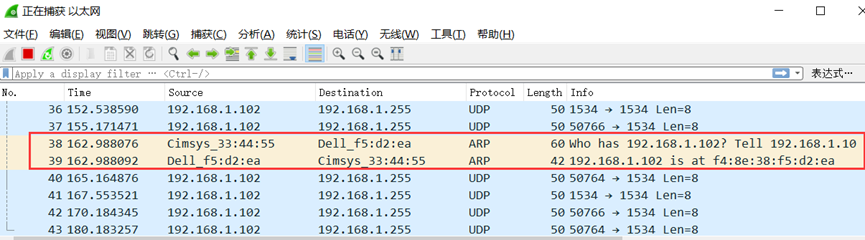

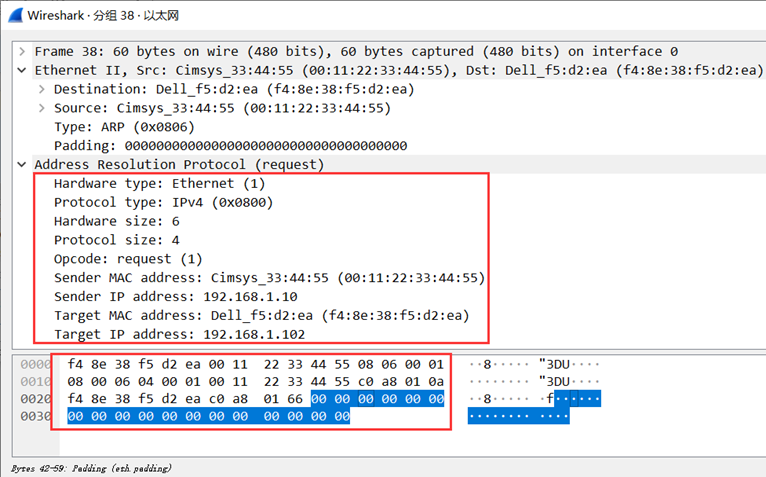

利用上位機(jī)端wireshark軟件抓取FPGA端發(fā)來的ARP請(qǐng)求數(shù)據(jù)包,如下圖所示:

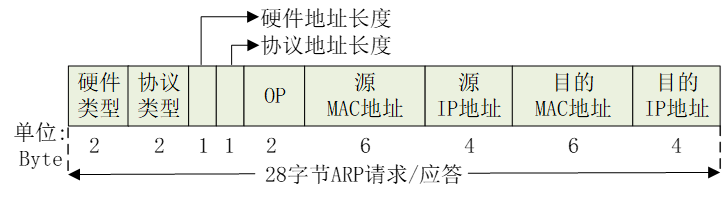

下圖中下方紅框?yàn)镕PGA發(fā)送的16進(jìn)制數(shù)據(jù)(去掉前導(dǎo)碼、SFD和CRC值),可以看到,后面的18個(gè)0就是我們?cè)诎l(fā)送時(shí)填充的18個(gè)字節(jié)數(shù)據(jù)。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21989瀏覽量

615209 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5600瀏覽量

175095 -

接口

+關(guān)注

關(guān)注

33文章

8967瀏覽量

153344 -

通信

+關(guān)注

關(guān)注

18文章

6185瀏覽量

137472 -

ARP

+關(guān)注

關(guān)注

0文章

50瀏覽量

14960

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的以太網(wǎng)ARP通信測(cè)試(一)

【小梅哥2017力作】詳細(xì)的FPGA以太網(wǎng)設(shè)計(jì)教程,76頁(yè)精華PDF

【AC620 FPGA試用體驗(yàn)】以太網(wǎng)ARP幀發(fā)包實(shí)例(手動(dòng)CRC)

【正點(diǎn)原子FPGA連載】第二十五章以太網(wǎng)ARP測(cè)試實(shí)驗(yàn)-領(lǐng)航者ZYNQ之FPGA開發(fā)指南

基于BL706 emac實(shí)現(xiàn)通過以太網(wǎng)發(fā)送一個(gè)ARP裸數(shù)據(jù)包的例程

基于以太網(wǎng)接口的TCP/IP 實(shí)驗(yàn)

基于FPGA的萬(wàn)兆以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的實(shí)時(shí)以太網(wǎng)(PowerLink)星載通信技術(shù)

在工業(yè)以太網(wǎng)領(lǐng)域采用FPGA的好處

用以太網(wǎng) Ping的方式對(duì) MAX10 FPGA 開發(fā)套件進(jìn)行測(cè)試

FPGA如何為以太網(wǎng)和千兆以太網(wǎng)解決低功耗問題

基于FPGA的千兆以太網(wǎng)ARP和UDP的實(shí)現(xiàn)

基于FPGA的UDP千兆以太網(wǎng)光通信

基于FPGA的UDP RGMII千兆以太網(wǎng)通信方案

基于FPGA的以太網(wǎng)ARP通信測(cè)試(二)

基于FPGA的以太網(wǎng)ARP通信測(cè)試(二)

評(píng)論