2023年11月10日,芯行紀科技有限公司(簡稱“芯行紀”)在中國集成電路設(shè)計業(yè) 2023 年會暨廣州集成電路產(chǎn)業(yè)創(chuàng)新發(fā)展高峰論壇(簡稱“ICCAD 2023”)中正式宣布推出數(shù)字實現(xiàn)布局布線工具AmazeSys。

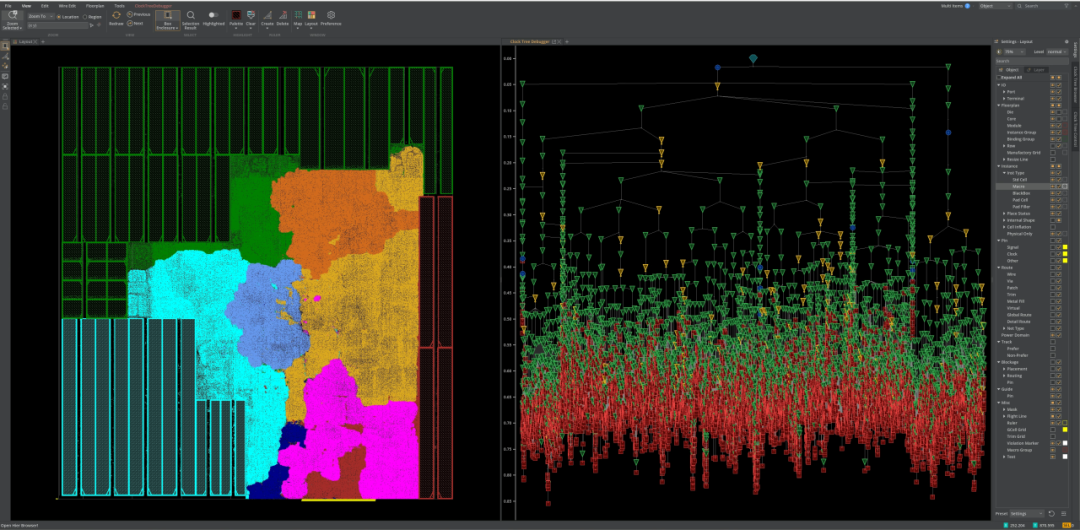

作為全新一代數(shù)字芯片物理設(shè)計實現(xiàn)工具,AmazeSys包含宏單元布局規(guī)劃、電源規(guī)劃、布局、時鐘樹綜合、布線、優(yōu)化、寄生參數(shù)提取以及時序功耗分析等物理實現(xiàn)全功能模塊,支持先進工藝制程下的超大規(guī)模設(shè)計,可服務(wù)數(shù)字芯片從Netlist到GDS的完整后端設(shè)計流程,完成從設(shè)計端到制造端的交付功能。以實力出色的智能特性將設(shè)計效率提升至新高度,帶來嶄新的開發(fā)體驗。

內(nèi)嵌先進的機器學習引擎內(nèi)核,AmazeSys能夠為SoC開發(fā)人員提供針對性更強的高度智能化和量身推薦的優(yōu)化方案,從全局角度分析設(shè)計內(nèi)容,平衡且快速達成性能、功耗和面積(PPA)等設(shè)計指標。全新的分布式數(shù)據(jù)結(jié)構(gòu)支持分布式優(yōu)化,動態(tài)合理分配硬件資源,允許多個任務(wù)同步運行,將算力效能最大化,加速設(shè)計收斂進程。基于完全自主的簽核級別寄生參數(shù)提取和時序功耗分析引擎,AmazeSys的結(jié)果輸出與業(yè)界標準簽核工具高度一致,顯著減少迭代輪次。友好的多功能界面為開發(fā)人員提供前所未有的設(shè)計體驗,可從多維度實時查看并修改,同步獲取反饋。

AmazeSys將為復(fù)雜程度愈發(fā)增加的芯片設(shè)計端和工藝不斷更新迭代的芯片制造端帶來新的創(chuàng)新元素,完全自主研發(fā)的過程能確保系統(tǒng)各個環(huán)節(jié)都能快速匹配和滿足客戶的需求。憑借其強大的關(guān)鍵核心技術(shù)引擎和獨特的基礎(chǔ)數(shù)據(jù)架構(gòu),布局布線全流程將被賦予耳目一新的智能化表現(xiàn)。

關(guān)于芯行紀

芯行紀科技有限公司(X-Times Design Automation Co., LTD)匯聚全球杰出EDA技術(shù)支持和研發(fā)精英,著力于自主研發(fā)符合3S理念(Smart、Speedy、Simple)的數(shù)字實現(xiàn)EDA平臺,包含新一代布局布線技術(shù),同時提供高端數(shù)字芯片設(shè)計解決方案,可大幅度提升芯片設(shè)計效率,并助力實現(xiàn)芯片一次性快速量產(chǎn),在人工智能、智能汽車、5G、云計算等集成電路領(lǐng)域為眾多合作伙伴的高速發(fā)展和產(chǎn)業(yè)騰飛保駕護航。

-

集成電路

+關(guān)注

關(guān)注

5420文章

12008瀏覽量

367725 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1075瀏覽量

55534 -

機器學習

+關(guān)注

關(guān)注

66文章

8499瀏覽量

134299

原文標題:芯行紀宣布推出布局布線工具AmazeSys

文章出處:【微信號:gh_2894c3fc5359,微信公眾號:芯行紀】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

行芯科技提供Signoff工具鏈一站式解決方案

芯行紀獲評2025年度南京市瞪羚企業(yè)

解決噪聲問題試試從PCB布局布線入手

芯行紀榮登2025中國IC設(shè)計Fabless100排行榜之TOP10 EDA公司

消防弱電系統(tǒng)綜合布線能用多芯線嗎

行芯完成DeepSeek-R1大模型本地化部署

VirtualLab Fusion應(yīng)用:光導(dǎo)布局設(shè)計工具

104條關(guān)于PCB布局布線的小技巧

芯行紀亮相ICCAD-Expo 2024

Vivado之實現(xiàn)布局布線流程介紹

[匠芯創(chuàng)科技]匠芯創(chuàng)AIUIBuilder工具使用初體驗

在DSP上實現(xiàn)DDR2 PCB布局布線

求助,關(guān)于模擬電路的PCB布線及布局問題求解

高速ADC PCB布局布線技巧分享

芯行紀宣布推出布局布線工具AmazeSys

芯行紀宣布推出布局布線工具AmazeSys

評論