簡介

使用可編程邏輯器件進行設計時,最關鍵的步驟之一就是為應用選擇最佳的器件。在 AMD 成本優化產品系列中,有一些專門可供開發者選擇的 FPGA 及異構 SoC。即AMD 成本優化產品系列Cost-Optimized Portfolio(COP)目前包含 AMD 7 系列、 UltraScale+ 系列器件、所有 AMD Spartan 7 與 AMD Artix 7 系列以及 Z7020 以下的 AMD Zynq 7000 器件等。在 UltraScale+ 系列中,COP 包含 AMD Artix UltraScale+ 系列以及包含 ZU3T 的 AMD Zynq UltraScale+ 器件。

什么是COP? 能為開發者帶來哪些優勢?

這些器件通常用于各種應用領域,其中包括機器人、醫療、工業、音頻、視頻、游戲系統、無人機、家庭自動化與聯網等。對于開發者而言,COP 具有以下顯著優勢:

系統集成:可在單個器件內執行多種功能,尤其是在使用異構 SoC 時,在單個器件中集成多種功能可降低材料成本,還可減小產品物理尺寸。

上市時間:集成解決方案的開發時間更短,與基于 ASIC 的解決方案相比FPGA 的靈活性更高。AMD 還為開發者提供了大量開發板和 IP,以加速應用開發。開發板包括 AMD Kria KV260 和 KR260 入門套件、Avnet Ultra96-V2 和 ZUBoard 1CG 等。AMD 論壇、開發者計劃以及 MicroZed Chronicles 等社區資源也非常豐富。

現場更新:隨著產品規劃及標準的發展,FPGA 及異構 SoC 可以在現場進行更新。必要時,還可消除對召回的需求。

低風險解決方案:集成解決方案使電路板的設計更加簡單,還有助于降低與電磁干擾 / 兼容性 (EMI/EMC) 相關的風險。

架構靈活性:異構 SoC 及 FPGA 器件為開發者提供了在順序處理和并行處理之間構建解決方案的能力,既可使用 SoC 中的硬內核,也可使用 FPGA 結構中的軟處理器。此外,可編程邏輯還提供了任意接口連接功能。異構 SoC 器件的獨特架構使開發者能夠通過在可編程邏輯中創建自定義加速器來進一步提高系統性能,如使用 AMD Vivado 高層次綜合 (HLS) 卸載 C 算法。

AMD 已經宣布 AMD 7 系列產品系列器件的供貨至少會延長至 2035 年,以支持醫療、工業和汽車等許多 COP 應用所需的長期生產運行。COP 中包括一系列廣泛的器件,這些器件可提供大量開發者能充分利用的架構特性。FPGA 及 SoC 器件都可分為 7 系列器件和 UltraScale+ 系列器件。7 系列中的 COP 器件包括 AMD Spartan 7 和 Artix 7 系列。AMD Spartan 7 器件可為開發者提供最低的成本、最小的封裝以及最高的 I/O 邏輯比。如果需要多千兆位收發器,則 AMD Artix 7 可為開發者提供工作速率高達 6.6Gbps 的收發器。

如果需要在 7 系列范圍內進行嵌入式處理,從 Z7007S 到 Z7020 的 AMD Zynq 7000 器件可為開發者提供單核或雙核 Arm Cortex-A9 處理器和可編程邏輯。UltraScale+ MPSoC 系列可為開發者提供雙核或四核 A53 處理器。

在 UltraScale+ 系列中,COP 包括 AMD Artix UltraScale+ 器件和 UltraScale+ MPSoC 系列中的 ZU1 至 ZU3T 器件,前者帶有收發器,能夠支持高達 16 Gb/s 的線路速率。

除了可編程邏輯和嵌入式處理器內核外,COP 系列中的 7 系列及 UltraScale+ 器件還包含如下架構特性:

系統監控器 / XADC:一款能夠監控內部電壓軌和溫度的嵌入式 ADC,因此非常適合系統安全和安保實施。

PCIe:通過支持多條通道實現的 PCIe Gen 3 或 Gen 4 端點及根端口實施,可在芯片內外傳輸高帶寬數據。

集成型內存:支持 BlockRAM 與 UltraRAM。BlockRAM 是靈活性極高的專用 36Kb 內存塊。每個 BlockRAM 均提供兩個讀寫端口,可以作為一個 36Kb 存儲器或兩個 18Kb 存儲器來實現 UltraRAM 的目的是取代板外存儲器,通過高達 14 Mb 的 UltraRAM 存儲器實現更好的整體性能。

靈活的 I/O:I/O 支持各種接口,從通過高性能 I/O (HPIO) 實現的高速差分信號,到支持 3v3 標準的高密度和高范圍 I/O (HDIO、HRIO),從而更容易與常用設備集成。

安全特性:多級安全功能,從使用 AES 的比特流加密到使用 AES、RSA 和 SHA 的安全啟動。COP 中的部分器件還具有密鑰管理與滾動功能。

如何選擇最佳 COP 器件

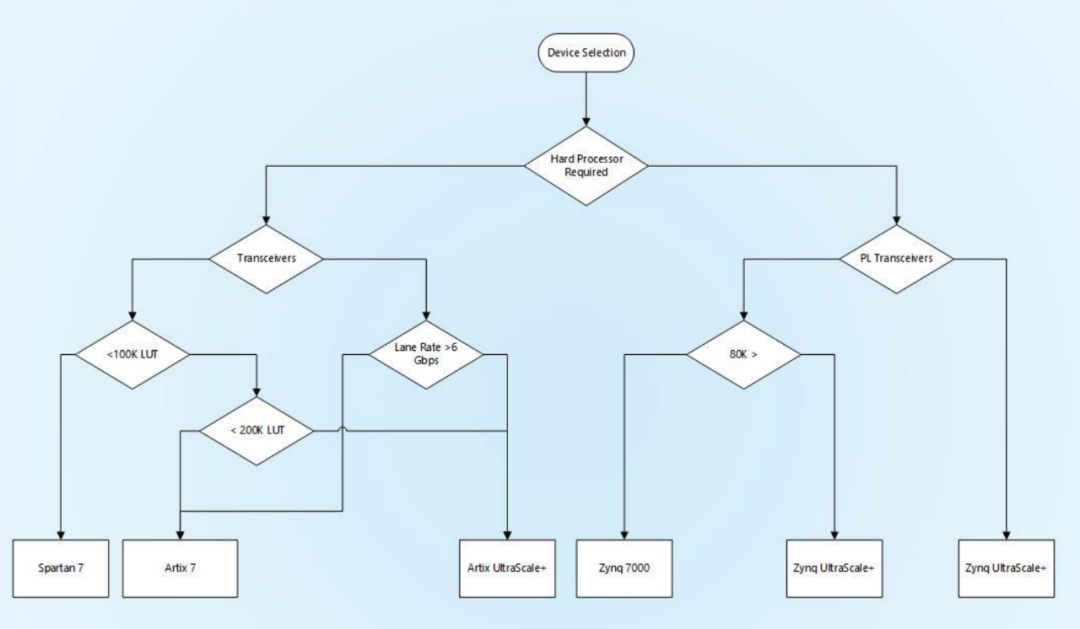

在 COP 器件之間進行選擇可能是一項非常艱巨的任務,因此我們可將以下流程圖作為指導,以幫助為您的應用選出最適合的器件。

第一個決定因素是:是否需要嵌入式處理器。根據這個問題的答案,我們可以在 AMD Zynq 7000 與 AMD Zynq UltraScale+ 器件或 AMD Spartan 7、AMD Artix 7 和 AMD Artix UltraScale+ 器件之間做出選擇。

如果需要嵌入式處理器,我們則需要確定邏輯設計中是否需要 PL 收發器。所有 AMD Zynq 7000 MPSoC 器件都具有 PS GTR 高速收發器,用于實現 USB3.0、SATA 與 DisplayPort 等。如果需要收發器,則應選擇 AMD Zynq UltraScale+ ZU3T,因為它提供 PL 收發器。

如果不需要 PL 收發器,則需要根據所需的邏輯資源的大小評估進一步的決策點。如果需要低于 80k 的 LUT,則應考慮 AMD Zynq 7000 系列器件。如所需的邏輯資源超過 80k,則應考慮 AMD Zynq UltraScale+ MPSoC。值得注意的是,在整個項目生命周期中確定邏輯資源大小時,經常會出現范圍和需求變化,從而增加邏輯資源。因此,在完成初始尺寸估算時,最好將器件尺寸調整為大約滿載的 60%。這既能為設計發展預留空間,又能隨著規模的增大降低實施時序閉合問題的風險。

最后一個考慮因素可能是最終應用。大量邊緣應用要求外形小巧,以符合尺寸、重量和功耗方面的要求。可編程邏輯器件處于系統的核心位置,因此尺寸受限的應用可從占位尺寸更小的器件中獲得巨大優勢。幸運的是,AMD Zynq UltraScale+和 AMD Artix UltraScale+器件采用集成扇出型封裝(InFO),與倒裝芯片解決方案相比,該解決方案可減少組件板面積和高度。如果您不熟悉 InFO 封裝,簡單說它可以去除基板從而減少電路板面積和高度,所選器件的封裝也可能是選擇標準中的一個重要部分。

圖 1. COP 器件選擇流程圖

如果不需要嵌入式處理,則必須確定是否需要收發器。如果需要,可以考慮 AMD Artix 7 或 Artix UltraScale+ 系列。如果不需要收發器,那么決策點就是價格、邏輯資源與 I/O 邏輯比。開發者通常會選擇成本較低的 AMD Spartan 7 器件或邏輯密度較大的 AMD Artix 7 器件。對于邏輯密度較大的器件,可首選 AMD Artix UltraScale+ 系列器件。

案例研究

我們來看幾個有關器件選擇的簡單案例。

1. 第一個案例是一個圖像采集器,需要使用收發器以專有標準采集科學圖像輸出。捕獲的圖像必須能通過以太網下載,使用 PYNQ 框架。

該案例需要一款嵌入式處理器與下游網絡通信還需要 PL 收發器通信來實現千兆位收發器鏈路。PL 還將執行圖像捕獲流水線和 DMA,以便向處理器系統提供圖像數據。由于該應用使用 PL 收發器和嵌入式處理器,因此 ZU3T 是一個值得考慮的合適器件。

2. 第二個案例研究是 SMPTE UH-SDI 至 PCIe 采集卡。該卡將接收 US-SDI 幀,對其進行緩存并通過 PCIe 進行后續處理。這需要在輸入和輸出端采用高速收發器,以實現 12Gbps HD-SDI 所需的高數據速率,并支持 PCIe Gen3 x4(每通道 1Gb/s )。本案例中的決定因素是收發器的速度,AMD Artix UltraScale+ 是 COP 系列中唯一支持 16Gb/s 收發器的器件。

3. 最后一個案例是用于分析和測試除顫器生成的波形的醫療測試設備。這種測試設備采用 ADC 捕獲除顫器生成的波形,FPGA 會將波形捕獲到一個小型外部 SRAM 存儲器中。一旦捕捉到波形并進行緩沖后,就會對數據進行處理和分析,以確保波形符合預期。在此本應用中,不需要收發器,而且邏輯尺寸估計小于 100k LUT,并留有余量。其中的主要驅動因素是并行接收和緩存數據。由于不需要嵌入式處理器,也不需要收發器,因此 AMD Spartan 7 FPGA 的邏輯資源指示< 100k LUT 是開發者考慮的正確起點。

7

總結:

AMD COP 中提供的各種精細粒度器件意味著一種器件可以滿足大多數應用需求。從 AMD Spartan 7 FPGA 產品中的最小封裝,到 AMD Artix UltraScale+ 器件中帶有 16Gb/s 收發器的緊湊型邏輯資源,再到高性能功率優化器件以及 AMD ZU3T 中帶有收發器的異構 SoC,成本優化產品系列可為開發者提供了一系列可用于多種應用的器件。

注:所有性能和成本節約聲明均由 Adiuvo 提供,未經 AMD 獨立驗證。性能和成本優勢可能會受各種變量影響。本文的結果僅針對 Adiuvo,可能不具有廣泛代表性。

審核編輯:劉清

-

收發器

+關注

關注

10文章

3555瀏覽量

107043 -

soc

+關注

關注

38文章

4301瀏覽量

221007 -

嵌入式處理器

+關注

關注

0文章

256瀏覽量

31043 -

GTR

+關注

關注

1文章

19瀏覽量

11223 -

InFO技術

+關注

關注

0文章

5瀏覽量

1207

原文標題:AMD Cost-Optimized Portfolio 成本優化系列-- 為您的應用選擇最佳器件

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

全自動洗衣機微電腦芯片COP8780C11電子資料

鴻蒙生態迎來新機遇,華為開發者大會帶來新特性

潤和軟件榮獲華為開發者聯盟 2022年度最佳生態服務商獎

COP8CDR9 微控制器在多路數據采集中的應用

XGate-COP10 CANopen協議轉換模塊硬件設計指

用COP820CJ實現可變輸入范圍的PWM A/D轉換

什么是COP?能為開發者帶來哪些優勢?如何選擇最佳COP器件?

什么是COP?能為開發者帶來哪些優勢?如何選擇最佳COP器件?

評論