作者: 關(guān)牮 JamesG,來(lái)源: 半導(dǎo)體綜研微信公眾號(hào)

半導(dǎo)體芯片封裝的目的無(wú)非是要起到對(duì)芯片本身的保護(hù)作用和實(shí)現(xiàn)芯片之間的信號(hào)互聯(lián)。在過(guò)去的很長(zhǎng)時(shí)間段里,芯片性能的提升主要是依靠設(shè)計(jì)以及制造工藝的提升。

然而隨著半導(dǎo)體芯片的晶體管結(jié)構(gòu)進(jìn)入到FinFET時(shí)代,工藝節(jié)點(diǎn)的進(jìn)步呈現(xiàn)明顯的趨緩形勢(shì)。雖然根據(jù)行業(yè)的發(fā)展路線圖,工藝節(jié)點(diǎn)的迭代還有很大的上升空間,但我們能夠明顯感覺(jué)到摩爾定律的減緩,以及生產(chǎn)成本暴增帶來(lái)的壓力。

由此,通過(guò)改革封裝技術(shù)來(lái)進(jìn)一步挖掘性能提升的潛力成為一個(gè)非常重要的手段。好幾年前開(kāi)始,行業(yè)內(nèi)就出現(xiàn)了通過(guò)先進(jìn)封裝的技術(shù)來(lái)實(shí)現(xiàn) “超越摩爾(More than Moore)”的口號(hào)

所謂先進(jìn)封裝,一般行業(yè)內(nèi)的常用定義就是:所有利用前道制造的工藝方法的封裝技術(shù)

通過(guò)先進(jìn)封裝的手段,我們可以:

大幅度縮小封裝后芯片的面積

無(wú)論是多個(gè)芯片的合封,還是單個(gè)芯片的Wafer Level化封裝,都可以明顯降低封裝尺寸以減小整個(gè)系統(tǒng)板的使用面積。利用封裝手段縮小芯片面積在經(jīng)濟(jì)上要比提升前道工藝來(lái)得更為劃算

容納更多芯片的I/O端口數(shù)量

由于前道工藝方法的引入,我們可以利用RDL技術(shù)使得單位面積的芯片上能夠容納更多的I/O管腳,從而減少芯片面積的浪費(fèi)

降低芯片綜合制造成本

由于引入Chiplet的方案,我們可以比較容易地將多個(gè)不同功能、不同工藝技術(shù)/節(jié)點(diǎn)的芯片合封到一起,形成一個(gè)系統(tǒng)集成芯片(SIP)。這樣就可以避免所有功能和IP都必須采用同一種(最高工藝)的高成本方法

提升芯片間的互聯(lián)能力

隨著大算力需求的提升,在很多應(yīng)用場(chǎng)景里都需要計(jì)算單元(CPU、GPU...)和DRAM做大量的數(shù)據(jù)交換。這往往會(huì)導(dǎo)致整個(gè)系統(tǒng)幾乎有一半的性能和功耗浪費(fèi)在信息交互上。現(xiàn)在我們通過(guò)各種2.5D/3D封裝,將處理器和DRAM盡可能近的連接在一起,就可以將這種損耗降低到20%以內(nèi),從而大幅度降低計(jì)算的成本。這種效率的提升遠(yuǎn)遠(yuǎn)超過(guò)了通過(guò)采用更先進(jìn)制造工藝帶來(lái)的進(jìn)步

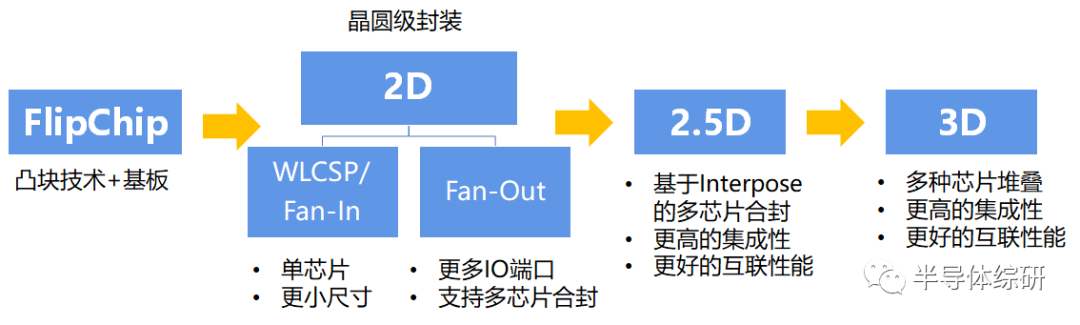

下圖是我簡(jiǎn)單整理的先進(jìn)封裝技術(shù)的演進(jìn)過(guò)程

在Flipchip階段,封裝的方式還比較接近于傳統(tǒng)技術(shù)路線(我多數(shù)時(shí)候其實(shí)是把Flipchip當(dāng)作傳統(tǒng)封裝來(lái)對(duì)待的)

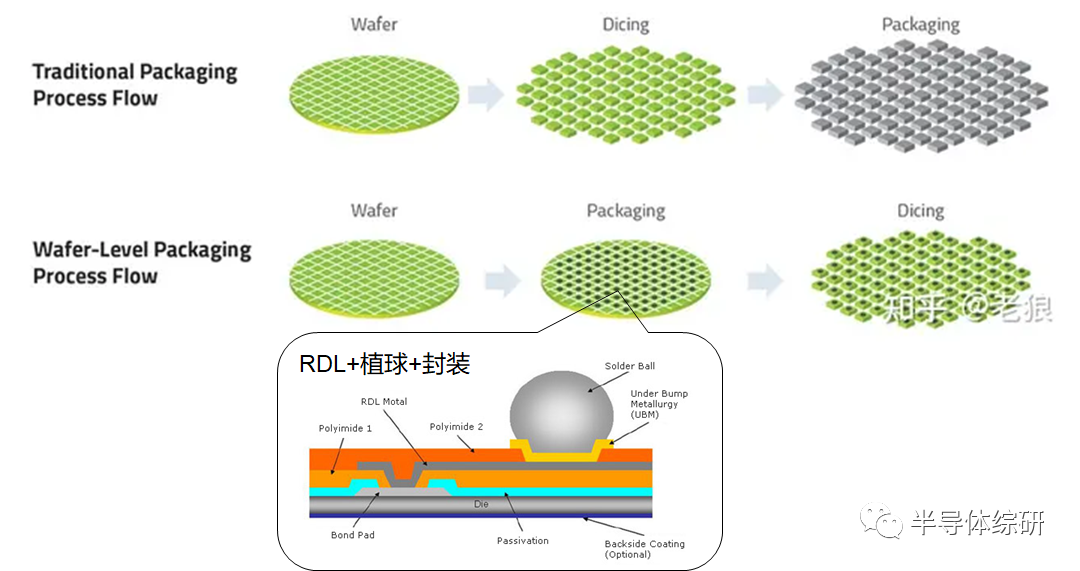

而從下圖可以看到,相對(duì)于傳統(tǒng)封裝,WLCSP(FanIn)的方法就和傳統(tǒng)有著明顯的區(qū)別:用前道技術(shù)直接對(duì)晶圓進(jìn)行加工(RDL+凸塊)后再直接切割形成芯片

數(shù)據(jù)來(lái)源:網(wǎng)絡(luò)

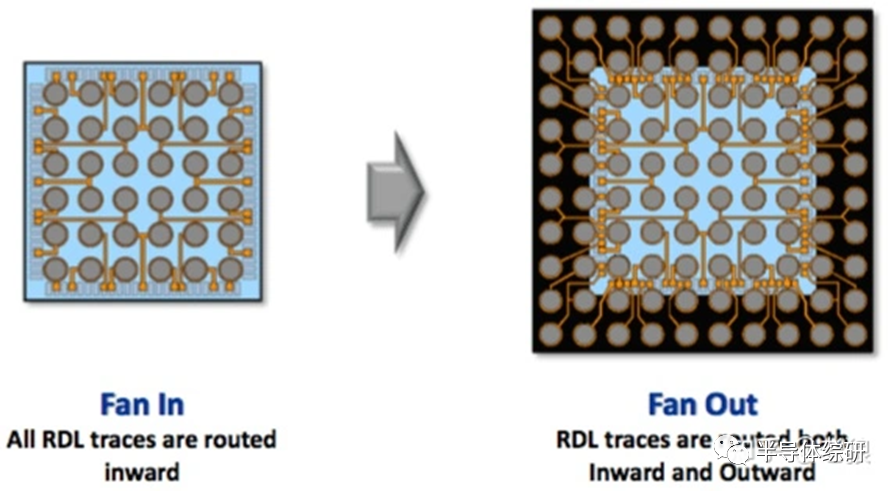

而當(dāng)芯片上的I/O端口越來(lái)越多,以至于芯片有限面積無(wú)法直接容納這么多管腳的時(shí)候,在原來(lái)WLCSP(Fan-In)的基礎(chǔ)上又發(fā)展出了FanOut技術(shù):通過(guò)封裝材料擴(kuò)大芯片面積來(lái)容納更多管腳。而且這樣一來(lái),多芯片的合封也成為了可能

數(shù)據(jù)來(lái)源:網(wǎng)絡(luò)

當(dāng)然,封裝技術(shù)的發(fā)展并未在此止步。隨著大算力芯片的技術(shù)和市場(chǎng)需求的高速發(fā)展,行業(yè)內(nèi)又開(kāi)始開(kāi)發(fā)了2.5D和3D技術(shù):

2.5D:通過(guò)Interposer(通常以硅基板為主要材料)將處理器和HBM(High Bandwidth Memory)進(jìn)行高密度和高效率互聯(lián)。其中最有名的就是最近因?yàn)?a href="http://m.xsypw.cn/v/tag/150/" target="_blank">人工智能而火出圈的臺(tái)積電的CoWoS封裝技術(shù)

3D:直接將不同芯片在Z軸方向上堆疊,通過(guò)TSV等方法實(shí)現(xiàn)更高效率互聯(lián)

在2.5D和3D封裝領(lǐng)域,目前全球主流的晶圓廠、封裝廠以及IDM都推出了自己的方案和技術(shù)路線

以下是我特意整理的各家的產(chǎn)品信息,可謂是五花八門、不一而足。

審核編輯 黃宇

-

芯片

+關(guān)注

關(guān)注

459文章

52267瀏覽量

437186 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28677瀏覽量

233602 -

封裝

+關(guān)注

關(guān)注

128文章

8568瀏覽量

144911

發(fā)布評(píng)論請(qǐng)先 登錄

介紹一些實(shí)用的Linux命令

想了解AVR單片機(jī)的硬件底層的一些操作

用stm32做一些開(kāi)發(fā)應(yīng)用

了解MOSFET的一些原理

需要了解的Linux 系統(tǒng)中一些針對(duì)文件系統(tǒng)的節(jié)能技巧

關(guān)于PADS需要了解哪一些

關(guān)于USB 4你所需要了解的一些知識(shí)

openharmony入門教程需要了解哪些

我們在選擇叉車時(shí)需要了解的一些注意事項(xiàng)

不只是前端,后端、產(chǎn)品和測(cè)試也需要了解的瀏覽器知識(shí)

我們?yōu)槭裁葱枰私庖恍┫冗M(jìn)封裝?

我們?yōu)槭裁葱枰私庖恍┫冗M(jìn)封裝?

評(píng)論